第10章_SPI接口及其应用

SPI接口详解

SPI接口详解SPI(Serial Peripheral Interface,串行外围设备接口)是由Motorola公司开发,用来在微控制器和外围设备芯片之间提供一个低成本、易使用的接口(SPI有时候也被称为4线接口)。

这种接口可以用来连接存储器(存储数据)、A/D转换器、D/A转换器、实时时钟日历、LCD 驱动器、传感器、音频芯片,甚至其他处理器。

支持SPI的元件很多,并且还一直在增加。

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度可达到几Mbps。

与标准的串行接口不同,SPI是一个同步协议接口,所有的传输都参照一个共同的时钟,这个同步时钟信号由主机(处理器)产生,接收数据的外设(从设备)使用时钟来对串行比特流的接收进行同步化。

可能会有许多芯片连到主机的同一个SPI接口上,这时主机通过触发从设备的片选输入引脚来选择接收数据的从设备,没有被选中的外设将不会参与SPI传输。

SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。

SPI主要使用4个信号:主机输出/从机输入(MOSI)、主机输入/主机输出(MISO)、串行SCLK或SCK和外设芯片(CS)。

有些处理器有SPI接口专用的芯片选择,称为从机选择(SS)。

(1)MOSI –主器件数据输出,从器件数据输入(2)MISO –主器件数据输入,从器件数据输出(3)SCLK –时钟信号,由主器件产生(4)/SS –从器件使能信号,由主器件控制在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。

在多个从器件的系统中,每个从器件需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。

MOSI信号由主机产生,从机接收。

在有些芯片上,MOSI只被简单的标为串行输入(SI),或者串行数据输入(SDI)。

第10章_SPI接口及其应用

系统在上电复位时,SPI工作在标准SPI模式,禁止FIFO功能。 FIFO的寄存器SPIFFTX ,SPIFFRX,SPIFFCT不起作用。通 过将SPIFFTX寄存器中的SPIFFEN的位置为1,使能FIFO模式。 SPIRST能在操作的任一阶段复位FIFO模式。 FIFO模式有两个中断,一个用于发送FIFO,SPITXINT,另一 个用于接收FIFO,SPIINT/SPIRXINT。对于标准SPI FIFO接收, 产生接收错误或者接收FIFO溢出都会产生SPIINT/SPIRXINT 中断。 对于标准SPI的接收和发送来说,唯一的SPIINT将被禁止且这 个中断将服务于SPI接收FIFO中断。

第十章

SPI接口及其应用

C28x处理器提供的串行外设接口(SPI)是一个高速

同步的串行输入输出口。

SPI的通信速率和通信数据长度都是可编程的。 SPI通常用于DSP处理器和外部外设以及其它处理

器之间进行通信。

主要应用于:显示驱动器、ADC以及日历时钟等器

件间接口,也可以采用主从模式实现多处理器间的 通信。 F2812处理器的SPl接口有一个16级的接收和传输 FIFO,这样可以减少CPU的开销。

该8位寄存器可以定义最小0个串行时钟周期的延迟和最大

256个时钟周期延迟的SPI模块能在最大延迟模式下发送数

该可编程延时的特点,使得SPI接口可以与许多速率较慢

的SPI外设如EEPROM、ADC、DAC等方便地直接连接。

(8)FIFO状态位:发送和接收FIFO都有状态位TXFFST或

当TALK位(SPICTL.1)清零,数据发送被禁止,输出引脚

(SPISOMl)处于高阻状态。如果在发送数据期间将TALK 位(SPICTL.1)清零,即使SPISOMl引脚被强制置成高阻 状态,也要完成当前的字符传输,这样可以保证SPI设备 能够正确的接收数据。

SPI接口及其在数据交换中的应用

3852007年第11期,第40卷 通 信 技 术 Vol.40,No.11,2007总第191期 Communications Technology No.191,Totally·业务与系统·SPI 接口及其在数据交换中的应用杨美刚, 李小文(重庆邮电大学,重庆 400065)【摘 要】SPI 是一种常用的串行通信协议,用于MCU 系统与外围设备的通信。

文中以OMAP1612/11的SPI 接口为例,论述了SPI 接口的端口、寄存器等结构,介绍了SPI 协议,给出了SPI 在主模式MCU_DSP 发送/接收协议下的数据发送/接收过程,并在FPGA 从端对SPI 接口进行仿真。

【关键词】SPI 接口;FPGA;串行接口技术;数据交换【中图分类号】TN929.5 【文献标识码】A 【文章编号】1002-0802(2007)11-0385-03SPI Interface and Its Application in Data ExchangeYANG Mei-gang, LI Xiao-wen(Chongqing University of Posts and Telecommunication, Chongqing 400065, China)【Abstract】SPI is a common-use serial communication protocol, which is used for communication between MCU and peripherals. Taking the SPI interface of OMAP1612 as an example, the paper gives an account of the structure, including the port for SPI interface and register etc,and describes the SPI protocol in detail. The SPI receive/transmit process of MCU-DSP receive/transmit protocol in master mode is also given, including the simulation of the whole process with FPGA in the terminal.【Key words 】SPI;FPGA;Serial Interface Technology;Data Commutation0 引言在数字技术高速发展的今天,有许多芯片被用作数据交换的核心器件,以起到承上启下的枢纽作用,或者是在集成电路之间进行数据的存储和显示等。

第10章 SPI接口及其应用

数据传输到SPIDAT位移后,则会发生下列事件

SPISET功能:主/从传送信息,置低;

数据传送完毕,置高;从控制器 Nhomakorabea式 MASTER/SLAVE=0

SPISOMI为输出(MSB), SPISIMO为输入(LSB)

SPICLK串行移位时钟输入,由主控制器提供;

SPICLK不大于CLKOUT的四分之一;

7. SPI串行发送缓冲寄存器(SPITXBUF)

8. SPI串行数据寄存器

发送/接收移位寄存器

9. SPIFFTX

10. SPIFFRX

11. SPIFFCT

12. SPI优先级控制寄存器(SPIPRI)

4个外部引脚: SPISIMO、SPISOMI、SPISTE、SPICLK

两种工作方式:主和从工作方式

波特率:126种可编程波特率

数据字长:可编程的1~16个数据长度

4种时钟模式(由时钟极性和时钟相位控制) 无相位延时的下降沿;

有相位延时的下降沿; 无相位延迟的上升沿; 有相位延迟的上升沿;

10.2 SPI数据传输方式

1. SPI通信数据格式

SPI接口有主和从两种操作模式: MASTER/SLAVE(SPICTL.2)选择操作 模式及SPICLK信号的来源

SPI主设备负责产生时钟

主控制器模式 MASTER/SLAVE=1

SPISIMO为输出(MSB),SPISOMI为输入(LSB)

接收和发送可同时操作

通过中断或查询方式实 现发送和接收操作

增强特点 16级发送/接收FIFO; 延时发送控制;

10.2 SPI数据传输方式

SPI主设备负责产生系统时钟,并决定整个 SPI网络的通信速率; 为了满足不同的接口需要,采用时钟的极性 和相位可配调整SPI的通信时序;

SPI的接口及其应用

SPI的接口及其应用2010-09-01 00:10:29| 分类:ARM及程序设计| 标签:|字号大中小订阅1 SPI接口的特点目前很多单片机都配置有SPI、I2C或UART等串行接口。

在SPI、I2C及UART三种串行接口一般情况下速度最快的是SPI。

I2C接口由于是二线协议速度很难超过1MHz/ Bit,而UART工作在方式0(8位移位寄存器)时时钟速度为系统时钟的十二分之一(Fosc/12),而SPI接口时钟速度一般为系统时钟的四分之一(Fosc/4)。

典型SPI接口结构如图1所示。

串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口,Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

SPI 用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI可以同时发出和接收串行数据。

它只需四条线就可以完成MCU与各种外围器件的通讯,这四条线是:串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。

这些外围器件可以是简单的TTL移位寄存器,复杂的LCD显示驱动器,A/D、D/A转换子系统或其他的MCU。

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚(MISO)接收的数据逐位移到移位寄存器(高位在前)。

发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。

主SPI的时钟信号(SCK)使传输同步。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

图2和图3中还给出了SPI总线工作的四种方式及SPI总线接口的时序。

SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

(SPI)工作原理及应用实例分析

ADμC812串行外设接口(SPI)工作原理及应用实例分析本文主要从全集成的12位数据采集系统ADμC812入手,通过首先分析其串行外设接口SPI的工作原理与系统组成,并用一个主机与从机的电路连接实例来说明其串行外设接口的具体应用特征,提供给嵌入式学习研究者一个完整的SPI 串行接口方案。

ADμC812在单个芯片内包含了高性能的自校准多通道ADC、2个12位DAC以及可编程的8位MCU(与8051兼容)。

为便于MCU与各种外围设备进行通信,ADμC812提供了3种串行I/O端口:UART接口、I2C兼容的串行接口和串行外设接口(SPI)。

其中,SPI接口是工业标准的同步串行接口,是一种全双工、三线通信的系统。

它允许MCU与各种外围设备以串行方式(8位数据同时、同步地被发送和接收)进行通信。

在SPI接口中,数据的传输需要1个时钟信号和两条数据线。

SPI可工作在主模式或从模式下。

在主模式,每一位数据的发送/接收需要1次时钟作用;而在从模式下,每一位数据都是在接收到时钟信号之后才发送/接收。

1个典型的SPI系统包括1个主MCU和1个或几个从外围器件。

SPI接口可设置成在发送/接收1个字节的结束时产生1次中断。

主时钟可以通过编程而成为不同的状态,既可编程为4种不同主波特率的任一种,又可对时钟的极性和相位进行编程。

SPI也可用于那些需要比微控制器上的并行I/O端口更多输入或输出端的场合中。

SPI提供了一种扩展I/O功能的最简单的办法,只需使用最少的微控制器引脚。

SPI串行接口可以在短距离内进行主机与从机的数据传送,并且具有多种可调的传输方式、连接电路简单、使用方便等优点。

为实现主机和从机及从外围设备的通信提供了一种简单、易行的方案。

一、工作原理1、SPI的信号说明SPI系统使用4条线可与多种标准外围器件直接接口:ADμC812的串行外设接口(SPI)及其应用2串行时钟线(SCLOCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS。

SPI接口介绍

SPI接口介绍

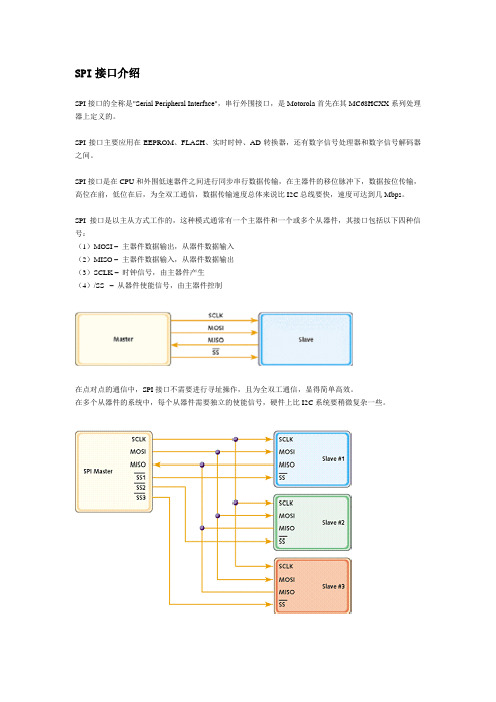

SPI接口的全称是"Serial Peripheral Interface",串行外围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在EEPROM、FLASH、实时时钟、AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,低位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度可达到几Mbps。

SPI接口是以主从方式工作的,这种模式通常有一个主器件和一个或多个从器件,其接口包括以下四种信号:

(1)MOSI –主器件数据输出,从器件数据输入

(2)MISO –主器件数据输入,从器件数据输出

(3)SCLK –时钟信号,由主器件产生

(4)/SS –从器件使能信号,由主器件控制

在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。

在多个从器件的系统中,每个从器件需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

如下图所示,在SCLK的下降沿上数据改变,同时一位数据被存入移位寄存器。

SPI接口内部硬件图示:

最后,SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。

微机原理与嵌入式接口技术(刘显荣)课件章 (10)

四种基本的扩展方法: 专用接口芯片扩展、 I/O模拟时序接 口扩展、 时序可编程芯片扩展和通信扩展。

1. 专用接口芯片扩展 在通用计算机领域, 对 CPU和相应的接口芯片的需求比 较大, 可以大批量生产以降低成本。 另外由于是通用的, CPU和接口芯片的种类不是太多。

第10章 嵌入式接口技术

SPI时序的总体要求是: 确保数据位在前一个时钟沿输出, 接收方在后一个时钟沿读取数据, 这样是最稳定的通信方式。

第10章 嵌入式接口技术 图10.6 SPI总线的环形结构

第10章 嵌入式接口技术

10.3.2 SPI从机选择 由于不具备总线仲裁能力,SPI总线上只能有一个主机,

第10章 嵌入式接口术 图 10.3 1602 字符液晶模块操作时序

第10章 嵌入式接口技术

第10章 嵌入式接口技术

第10章 嵌入式接口技术

10.2.3 STM32扩展1602 1. 硬件设计

STM32扩展 1602 的具体电路如图 10.4 所示。 虽然 1602 的工作电压是 5 V, 但是其数据、 状态和控制引脚为 TTL 电平, 和STM32的输出电平兼容, 引脚可以直接相连。 另外, 还可以用上拉电阻配合 MCU 的 OC 输出实现电平匹配, 不过 此时应该选择 5 V 兼容的STM32 接口线与 1602 液晶相连。

第10章 嵌入式接口技术

如图 10.1 所示,8086CPU与8255A的数据总线、 控制总 线直接相连, 地址总线基本也直接相连, 只有地址总线高位 上有译码电路, 这是因为在总线上往往挂有多个芯片, 在某 个时刻 CPU只能选中一个芯片, 与之建立联系。 因此必须利 用高位地址总线的译码结果选择芯片, 即高位地址 完成芯片选择, 低位地址完成片内寄存器/ 数据单元的选择。 数据与控制总线直连, 是专用接口芯片与CPU相连的一般规律。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

系统在上电复位时,SPI工作在标准SPI模式,禁止FIFO功能。 FIFO的寄存器SPIFFTX ,SPIFFRX,SPIFFCT不起作用。通 过将SPIFFTX寄存器中的SPIFFEN的位置为1,使能FIFO模式。 SPIRST能在操作的任一阶段复位FIFO模式。 FIFO模式有两个中断,一个用于发送FIFO,SPITXINT,另一 个用于接收FIFO,SPIINT/SPIRXINT。对于标准SPI FIFO接收, 产生接收错误或者接收FIFO溢出都会产生SPIINT/SPIRXINT 中断。 对于标准SPI的接收和发送来说,唯一的SPIINT将被禁止且这 个中断将服务于SPI接收FIFO中断。

发送和接收都能产生CPU中断。一旦发送FIFO状态位

TXFFST(位12~8)和中断触发级别位TXFFIL(位4~0)匹配, 就会触发中断。这给SPI的发送和接收提供了一个可编程 的中断触发器。接收FIFO的触发级别位的默认值是 0x11111,发送FIFO的触发级别位的默认值是0x00000。

在典型应用中,SPISET引脚作为从SPI控制器的片选控制

在从模式中(MASTER/SLAVE=0),SPISOMI引脚为数据输出引脚, SPISIMO引脚为数据输入引脚。 SPICLK引脚为串行移位时钟的输入,该时钟由网络主控制器提供, 传输率也由该时钟决定。SPICLK输入频率应不超过CLKOUT频率的 四分之—。 当从SPI设备检测到来自网络主控制器的SPICLK信号的合适时钟边 沿时,已经写入SPIDAT或SPITXBUF寄存器的数据被发送到网络上。 要发送字符的所有位移出SPIDAT寄存器后,写入到SPITXBUF寄存 器的数据将会传送到SPIDAT寄存器。 如果向SPITXBUF写入数据时没有数据发送,数据将立即传送到 SPIDAT 寄存器。为了能够接收数据,从SPI设备等待网络主控制器 发送SPICLK信号,然后将SPISIMO引脚上的数据移入到SPIDAT寄 存器中。 如果从控制器同时也发送数据,而且SPITXBUF还没有装载数据,则 必须在SPICLK开始之前把数据写入到SPITXBUF或SPIDAT寄存器。

寄存器 SPICCR SPICTL SPISTS SPIBRR SPIEMU SPIRXBUF SPITXBUF SPIDAT SPIFFTX SPIFFRX SPIFFCT SPIPRI

功能描述 SPI-A 配置控制寄存器 SPI-A 工作控制寄存器 SPI-A 状态寄存器 SPI-A 波特率寄存器 SPI-A 仿真缓冲寄存器 SPI-A 串行接受寄存器 SPI-A 串行发送寄存器 SPI-A 串行数据寄存器 SPI-A FIFO 发送寄存器 SPI-A FIFO 接受寄存器 SPI-A FIFO 控制寄存器 SPI-A 极性控制寄存器

15-8 reserved

7

6

5-4 reserved

3

2

1

0

SPI CHAR.3-0 字长控制位 字符长度=number+1 e.g. 0000b ⇒ length = 1 1111b ⇒ length = 16 CLOCK POLARITY 0 = 上升沿输出/下降沿输入 1 = 下降沿输入/上升沿输出 SPI SW RESET:在改变配置前清除此位 在重新操作开始前设置此位 0 = SPI 复位 1 = 正常操作

OVERRUN INT ENABLE

0 = 禁止接受溢出中断(SPISTS.7) 1 = 使能接受溢出中断(SPISTS.7)

MASTER/SLAVE 0=从 1=主

SPI INT ENABLE 0 = disabled 1 = enabled

1 0

15-5 reserved

4

3

2

CLOCK PHASE 0 = 无时钟延时 1 = CLK 延时 ½周期

当指定数量的数据位已经通过SPIDAT位移位后,则会发生

下列事件:

SPIDAT中的内容发送到SPlRXBUF寄存器中; SPI INT FLAG位(SPISTS.6)置1; 如果在发送缓冲器SPIRTXBUF中还有有效的数据(SPISTS 寄存器中的TXBUF FULL位标志是否存在有效数据),则这 个数据将被传送到SPIDAT寄存器并被发送出去。否则所有 位从SPIDAT寄存器移出后,SPICLC时钟立即停止; 如果SPI INT ENA位(SPICTL.0)置1,则产生中断。 信号,在主SPI设备同从SPI设备之间传送信息的过程中, SPISET置成低电平;当数据传送完毕后,该引脚置高。

在采用SPI实现数据通信的过程中,多个SPI器件互联的系

统中的一个设备必须设置成Master模式,其他设置为Slave 模式。 主设备驱动总线上的时钟信号为其他从设备提供通信时钟。

SPI设备的通信链接如下图所示,可以有以下几种工作模式:

Sub title

• Master发送数据,Slave发送伪数据; • Master发送数据,其中一个Slave发送数据; • Master发送伪数据,其中一个Slave发送数据;

SPIDAT - Processor #1

11001001XXXXXXXX

接受数据小于16位时必须右 对齐 用户程序屏蔽无效的高字节

SPIDAT - Processor #2

XXXXXXXX11001001

•

SPI接口有主和从两种操作模式,MASTER/SLAVE位(SPICTL.2)选 择操作模式以及SPICLK信号的来源。 SPISIMO 串行输入缓冲 SPIRXBUF SPIRXBUF.15-0 MSB SPIDAT.15-0 移位寄存器 SPITXBUF.15-0 串行发送缓冲 SPITX FIFO LSPCLK baud rate clock polarity clock phase SPICLK LSB

C28x - SPI 主模式

SPISOMI

C28x - SPI 从模式

SPISIMO RX FIFO_0 RX FIFO_15 SPIRXBUF.15-0

LSB

SPIDAT.15-0 SPITXBUF.15-0 TX FIFO_0 TX FIFO_15

MSB

SPISOMI

clock phase

SPICLK

RXFFST(位12—0),状态位定义任何时刻在FIFO中可获 得的字的数量。当发送FIFO复位位TXFIFO和接收复位 位RXFIFO被设置为1时,将使FIFO指针指向0。一旦这 两个复位位被清除为0,则FIFO将重新开始操作。

地址 0x007040 0x007041 0x007042 0x007044 0x007046 0x007047 0x007048 0x007049 0x00704A 0x00704B 0x00704C 0x00704F

理器内部寄存器改变时钟的极性和相位。

SPI设备传输数据过程中总是先发送或接收高字节数据,

每个时钟周期接收器或收发器左移一位数据,对于小于16 位的数据在发送之前必须左对齐,如果接收的数据小于16 位则采用软件将无效的数据位屏蔽。如下图所示。

可编程数据长度1~16 发送数据少于16位时需要左 对齐 ◦ MSB (高字节)先发送

第十章

SPI接口及其应用

C28x处理器提供的串行外设接口(SPI)是一个高速

同步的串行输入输出口。

SPI的通信速率和通信数据长度都是可编程的。 SPI通常用于DSP处理器和外部外设以及其它处理

器之间进行通信。

主要应用于:显示驱动器、ADC以及日历时钟等器

件间接口,也可以采用主从模式实现多处理器间的 通信。 F2812处理器的SPl接口有一个16级的接收和传输 FIFO,这样可以减少CPU的开销。

数据同步传输和接受 SPI主设备提供时钟

SPI 器件 #1 - Master 移位 SPI 移位寄存器 时钟

SPI 器件 #2 - Slave 移位

SPI 移位寄存器

4个外部引脚: SPISOMI:SPI从输出/主输入引脚; SPISIMO:SPI从输入/主输出引脚; SPISTE:SPI从发送使能引脚; SPICLK:SPI串行时钟引脚。 2种工作模式:主工作模式、从工作模式 波特率:125种不同的可编程速率 数据字长:可编程1~16个数据长度 4种时钟模式(由时钟极性和时钟相位控制) ◦ 无相位延迟的下降沿:SPICLK高有效,SPI在SPICLK下降沿发送 数据,上升沿接受数据。 ◦ 有相位延迟的下降沿:SPICLK高有效,SPI在SPICLK的下降沿之 前半个周期发送数据,下降沿接受数据。 ◦ 无相位延迟的上升沿:SPICLK低有效,SPI在SPICLK的上升沿发 送数据,下降沿接受数据 ◦ 带有相位延迟的上升沿:SPICLK低有效,SPI在SPICLK的下降沿 之前半个周期发送数据,下降沿接受数据。

该8位寄存器可以定义最小0个串行时钟周期的延迟和最大

256个时钟周期延迟的SPI模块能在最大延迟模式下发送数

该可编程延时的特点,使得SPI接口可以与许多速率较慢

的SPI外设如EEPROM、ADC、DAC等方便地直接连接。

(8)FIFO状态位:发送和接收FIFO都有状态位TXFFST或

发送和接收缓冲器使用2个16*16

FIFO,标准SPI功能的 一个字的发送缓冲器作为在发送FIFO和移位寄存器间的 一个发送缓冲器。移位寄存器的最后一位被移出后,发送 缓冲器将从发送FIFO装载。

延时的发送:

FIFO 中的发送字发送到发送移位寄存器的 速率是可编程的。SPIFFCT寄存器位 FFTXDLY7~FFTXDLY0定义了在两个字发送间的延时。 这个延时以SPI串行时钟周期的数量来定义。 256个串行时钟周期的延时。0时钟周期延时的SPI模块能 将FIFO字一位紧接一位地移位,连续发送数据。 据,每个FIFO字的移位间隔256个SPI时钟周期的延时。