信号完整性分析笔记(全)

第12章 信号完整性分析

• 信号基值(Signal Base Value)规则 • 信号基值与信号高电平是相对应的,它定义了线路上信号在低电平状 态下所允许的最大稳定电压值,也即是信号的最大基值,系统默认单 位是伏特,如图所示。

• 飞升时间的上升沿(Flight Time-Rising Edge)规则 • 飞升时间的上升沿定义了信号上升边沿允许的最大飞行时间,也即是 信号上升边沿到达信号设定值的50%时所需的时间,系统默认单位是 秒,如图所示。

• 信号下冲的上升沿(Undershoot-Rising Edge)规则 • 信号下冲的上升沿与信号下冲的下降沿是相对应的,它定义了信号上升边沿允许的 最大下冲值,也即信号上升沿上低于信号上位值的阻尼振荡,系统默认单位是伏特, 如图所示。

• 阻抗约束(Impedance)规则 • 阻抗约束定义了电路板上所允许的电阻的最大和最小值,系统默认单 位是欧姆。阻抗和导体的几何外观以及电导率,导体外的绝缘层材料 以及电路板的几何物理分布,也即导体间在Z平面域的距离相关。上 述的绝缘层材料包括板的基本材料、多层间的绝缘层以及焊接材料等。 • 信号高电平(Signal Top Value)规则 • 信号高电平定义了线路上信号在高电平状态下所允许的最小稳定电压 值,也即是信号上位值的最小电压,系统默认单位是伏特,如图所示。

5.“Period Time”:设置激励信号的周期。 设置激励信号的时间参数,在输入数值的同时,要注意添加时间单位, 以免设置出错。 • 信号过冲的下降沿(Overshoot-Falling Edge)规则 • 信号过冲的下降沿定义了信号下降边沿允许的最大过冲位,也即信号 下降沿上低于信号基值的最大阻尼振荡,系统默认单位是伏特,如图 所示。 • 信号过冲的上升沿(Overshoot-Rising Edge)规则 • 信号过冲的上升沿与信号过冲的下降沿是相对应的,它定义了信号上 升边沿允许的最大过冲值,也即信号上升沿上高于信号上位值的最大 阻尼振荡,系统默认单位是伏特,如图所示。 • 信号下冲的下降沿(Undershoot-Falling Edge)规则 • 信号下冲与信号过冲略有区别。信号下冲的下降沿定义了信号下降边 沿允许的最大下冲值,也即信号下降沿上高于信号基值的阻尼振荡, 系统默认单位是伏特,如图所示。

传输线理论及信号完整性分析

信号完整性分析(Signal Integrity) SI的四种分析、描述手段和途径

传输线理论

多长的走线才是传输线? 这和信号的传播速度有关,在FR4板材上铜线条中信号速 度为6in/ns。简单的说,只要信号在走线上的往返时间大于 信号的上升时间,PCB上的走线就应当做传输线来处理。 对于传输时间<信号上升时间的线路,由于对信号的影响 微乎其微,所以在此不做讨论。 假设有一段60英寸长的PCB走线,如图1所示,返回路径是 PCB板内层靠近信号线的地平面,信号线和地平面间在远端开 路。 在这段走线上加一个上升时间为1ns的信号,在最初的1ns 时间,信号在线条上还是走了6英寸。

*这个很容易理解,线之间的间距大,其分布电容电感之间的影响就小,电 磁场耦合也会变小

2.在满足阻抗要求的情况下,应该使传输线和参考平面间的距离越小 越好(减小H)。这样做会让传输线和参考平面更紧密的耦合,减少 临近线的干扰 3.对于关键信号(例如时钟信号)用差分走线,如果系统设计允许的 话

*差分信号的共模抑制好,能有效的抑制临近线的干扰。但是很多时候系统 设计就是单端模式。 *设计中要尽量减小H,但也不是无限制的,还受到制造工艺的限制。

传输线理论与

信号完整性分析

一、传输线理论

§1.什么是传输线

什么是传输线呢?任何2个有长度的导体就是传输线,如下图所示。 对于传输线,要彻底忘记“地”的概念,所谓的地不过是信号的 返回路径。所以传输线就是由信号路径和其返回路径构成的.

信号在传输线上的传播速度到底是多少呢?假定传输线介质的介电常数为4.空 气中信号的速度为 3000, 000km每秒,即30cm/nsec.那么在介质中的速度 就为 :

信号完整性分析(Signal Integrity)

《信号完整性分析与设计》读书笔记思维导图

11.3 EMI 与SI、PI 的关系

04

11.4 电流 回路的辐射

06

11.6 接 “地”之 “迷”

05

11.5 PCB 中主导EMI 的互连结构

11.8 小结

11.7 EMI设计要点

参考文献

12.1 数字器件的选 择与电路设计

12.2 电磁屏蔽与滤 波设计

12.3 参考平面的分 析与设计

5

参考文献

4.1 一般互连与非 理想互连

4.2 走线突变

4.3 过孔

4.4 参考平面不连 续

4.5 连接器 4.6 封装

4.7 小结 参考文献

5.1 信号带宽与上 升边

5.2 互连线的特性 区域

5.3 集总建模与宽 带建模

5.4 基于TDR测量的 走线突变建模

5.6 小结

5.5 基于电流通路 的过孔建模与仿真

1.4 SI、PI和EMI 协同设计

1.6 EMI的源头设 计策略

1.5 PDN影响SI

参考文献

2.1 电阻 2.2 电感

2.3 电容 2.4 传输线基础

2.5 高速及高频的 概念

2.6 高速互连的表 征

2.7 差分传输线 参考文献

1

3.1 反射

2

3.2 串扰

3

3.3 同时开关 噪声

4

3.4 小结

01

7.1 集成 电路的功率 传输

02

7.2 PDN的 组成

03

7.3 电源/ 地平面噪声 的产生与传 播

04

7.4 基于 目标阻抗的 PDN设计

06

7.6 PDN 集总分析技 术

05

7.5 平面 PDN常用的 建模技术

信号完整性分析

一所要面临的问题二一些有用的常识三电感电容及电阻的基础以及要注意的问题四传输线的问题以及反射等问题五有损线的损耗六差分信号和查分对的问题一所要面临的问题一单一网络的信号完整性二两个或多个网络间的串扰三电源和地分配中的轨道塌陷四来自整个系统中的电磁干扰和辐射一个重要的概念1:带宽的问题(注释2)对任意一个非理想的方波信号而言(电子系统这种波形非常常见,比如系统的时钟),该信号均可认为是由同频率的基波信号和高次谐波叠加而成。

假设一个1GHz 的时钟它是有1G 的基波加3次谐波再加5次谐波再加7次谐波组成的。

那个这个时钟信号的带宽就是7G.如果加到31次谐波了,那么这个信号的带宽就是31G。

随着叠加的谐波数越多叠加后的信号就越接近完美的方波。

换句话说那就是10%到90%上升时间越小。

可见信号的上升时间决定了信号的带宽。

这样确定系统时钟的上升时间就非常重要了。

为什么上升时间会这么重要呢?下面举例说明:大多数电路板而言会采用FR4板材,FR4板并非理想的无耗板材。

损耗的机理有两种第一导体损耗,第二介质损耗。

比损耗更为严重的是损耗对不同频率信号的损耗是不同,因为在物理上这涉及到介质充放电过程的快慢以及带来的损耗。

对一个4英寸(4000mil)的FR4传输线而言,这样的导线对8GHz的信号损耗达到能量的50%或幅值的70%.试想如果用这样的线去传导一个带宽为9G的1GHz的方波会怎样?结果就是组成这个方波的信号中九次谐波分量被严重损耗,而其他谐波分量也将不同成度的损耗。

这就导致方波的上升沿退化,比如原来上升边是50ps变成了1.5ns。

如果传输的信号频率是10MHz影响不大。

如果传输信号是500M,(2ns的周期)这下麻烦就大了去了。

下面引入带宽和上升时间的关系这是一个近似的经验上的估计:对于10%到90%上升时间来讲关系为:BW=0.35/RT(RT为10%到90%上升时间)也有一些资料给的上升时间是20%-80%上升时间。

Signal Integrity信号完整性学习笔记_chapter1

参数如何影响产品性能。

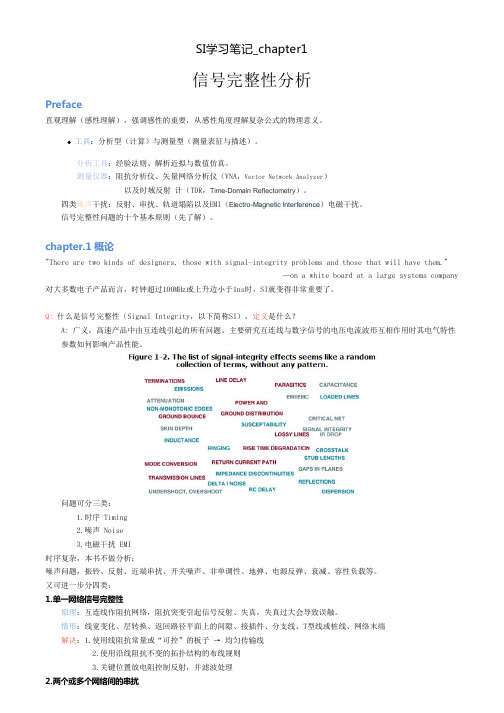

1.时序 Timing3.电磁干扰 EMI原理:电压电流作为噪声传递到邻近网络,而两者相对独立。

情形:互连线均匀与不均匀(插件、封装)。

均匀平面返回路径,感性耦合与容性耦合相当,是实现最低串扰结构。

感性比容性增加噪声多。

感性耦合主导,归为开关噪声、ΔI噪声、dI-dt噪声、地弹、同时开关噪声(SSN)或者同时开关输出噪声(SSO)。

也是耦合电感,即互感造成。

解决:1.从本质出发,在设计上优化2.选介电常数较小的材料3.简短互连线,使用最小封装(CSP,Chip Scale Packege)与高密度互连线(HDI,High DensityInterconnector)3.电源与地分配的轨道塌陷原理:过电源与地的电流发生变化,在电源或地路径间阻抗上产生压降(即轨道塌陷)。

高性能CPU与ASIC趋势:低电压电源供电,高功率损耗。

大开关电流降低了可容忍噪声。

解决:设计低阻抗电源分配系统(PDS,Power Distribution System)低阻抗1.邻电源与地分配层平面介质尽可能薄,慢慢靠近2.低电感去耦电容3.封装安排多个多个很短的电源与地引脚4.片内加去耦电容4.来自系统的电磁干扰与辐射原理:电子产品谐波干扰通信,共模电流辐射的远场强度随频率线性增加、差分电流辐射的远场强度与频率的平方成正比。

常见的两种干扰源:(1)部分差分信号转共模信号,在外部双绞线输出(2)电路板上地弹在外部单端屏蔽线上产生共模电流产生辐射的大多数电压源来自电源与地的分配网络。

上一点的解决方法也适用。

解决:1.使用屏蔽方法隔离2.电缆线正确使用铁氧体3.使用低阻抗电缆信号完整性的两个重要推论一、随上升边减小,四种问题会更严重(即dI/dt或dV/dt越大)。

二、解决SI的有效办法基本就基于互联线阻抗联系。

电子产品趋势大约每两年时钟频率翻一倍。

上升边与时钟频率关系:RT:上升边,单位为nsF clock:时钟频率,单位为GHz测量的信号转换时间都为终值的10%~90%这段时间,称为10-90上升边。

信号完整性分析

信号完整性分析1.背景在一次奇怪的设计失败之后,信号完整性问题首先引起了人们的注意。

当时,美国硅谷一家著名的图像检测系统制造商早在7年前就已经成功上市设计、制造和产品,但在最近出现的问题中,从生产线的产品来看,新产品的正常运行,这是一款20兆赫的系统设计,似乎是不需要考虑的设计上的问题,更使产品设计工程师在设计新产品时不做任何修改,甚至使用元件模型都与原设计要求一致,唯一不同的是集成电路制造技术的进步,新采购的电子元器件实现了小型化、快速化。

新的器件技术使每个芯片都成为一个高速器件,而正是这些高速器件应用中的信号完整性问题导致了系统的失效。

随着IC开关速度的提高和信号上升和下降时间的迅速缩短,无论信号频率如何,系统都将成为一个高速系统,并会出现各种信号完整性问题。

在高速PCB系统设计方面,信号完整性问题主要体现在以下几个方面:工作频率的提高和信号上升/下降时间的缩短会降低系统的定时裕度,甚至出现时序问题;传输线效应导致噪声容限,信号传输中的单调性甚至逻辑错误。

信号间的串扰随着信号传播时间的减少而加剧。

当信号传播时间接近0.5ns或以下时,供电系统的稳定性降低,产生电磁干扰。

2.含义(1)信号完整性(Signal Integrity)简称SI,指信号从驱动端沿传输线到达接收端后波形的完整程度。

即信号在电路中以正确的时序和电压作出响应的能力。

如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。

反之,当信号不能正常响应时,就出现了信号完整性问题。

从广义上讲,信号完整性问题指的是在高速产品中由互连线引起的所有问题,主要表现为五个方面:(2)延迟。

延迟是指信号在PCB 的导线上以有限的速度传输,从驱动端到接收端存在的传输延时。

信号的延时会对系统的时序产生影响,在高速PCB 设计中,传输延迟主要取决于导线的长度和导线周围介质的介电常数。

(2)反射。

当传输线的特性阻抗与负载阻抗不匹配时,信号到达接收端后有一部分能量将沿着传输线反射回去,使得信号波形发生畸变,甚至出现信号的过冲和下冲。

图讲信号完整性

信号完整性基础信号完整性问题过冲(overshoot/undershoot)振铃(ringing/ring back)非单调性(non-monotonic)码间串扰(ISI)同步开关噪声(SSN)噪声余量(noise margin)串扰(crosstalk)信号完整性(Signal Integrity)主要包括以下几方面问题:1.过冲(Overshoot/Undershoot)一般IC对于过冲的高度和宽度的容忍度都有指标。

因为过冲会使IC内部的ESD防护二极管导通,通常电流有100mA左右。

信号长期的过冲会使IC器件降质,并是电源噪声和EMI的来源之一。

2. 振铃(Ringing/Ring Back)振铃会使信号的threshold域值模糊,而且容易引起EMI。

3.非单调性(Non-monotonic)电平上升过程中的平台会产生非单调性,这有可能对电路有危害,特别是针对异步信号如:Reset、Clock等会有影响。

4. 码间串扰(ISI)主要是针对高速串行信号。

其产生的本质是前一个波形还没有进入稳态,另外也有可能是传输线对不同频率衰减不同所造成的。

一般通过眼图来观察,方法是输入一伪随机码,观察输出眼图。

5. 同步开关噪声(SSN)同步开关噪声会使单根静止的信号线上出现毛刺?V,另外还会影响输入电平的判断。

SSN的另一种现象是SSO(同步开关输出),这会使得传输线的特性如阻抗、延时等特性发生改变。

6. 噪声裕量(Noise Margin)控制噪声余量的目的是防止外界干扰,用于克服仿真没有分析到的一些次要因素。

一般对于TTL信号应留有200~300mV的余量。

7. 串扰(Crosstalk)串扰主要有线间串扰、回路串扰、通过平面串扰(常见于数模混合电路)三种形式。

通常示波器所观察到的数字信号。

图中为各相关的信号完整性参数:•Overshoot、Undershoot指信号的过冲。

•Ringback 指信号的振铃。

信号完整性SI学习笔记_chapter8

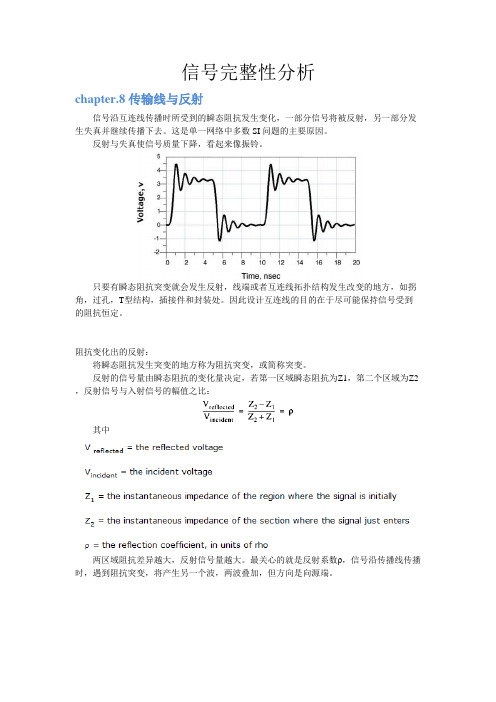

信号完整性分析chapter.8 传输线与反射信号沿互连线传播时所受到的瞬态阻抗发生变化,一部分信号将被反射,另一部分发生失真并继续传播下去。

这是单一网络中多数 SI 问题的主要原因。

反射与失真使信号质量下降,看起来像振铃。

只要有瞬态阻抗突变就会发生反射,线端或者互连线拓扑结构发生改变的地方,如拐角,过孔,T型结构,插接件和封装处。

因此设计互连线的目的在于尽可能保持信号受到的阻抗恒定。

阻抗变化出的反射:将瞬态阻抗发生突变的地方称为阻抗突变,或简称突变。

反射的信号量由瞬态阻抗的变化量决定,若第一区域瞬态阻抗为Z1,第二个区域为Z2,反射信号与入射信号的幅值之比:其中两区域阻抗差异越大,反射信号量越大。

最关心的就是反射系数ρ,信号沿传播线传播时,遇到阻抗突变,将产生另一个波,两波叠加,但方向是向源端。

反射形成机理由上一特性,在设计高速板时,要运用以下设计要素:1.使用可控阻抗互连线2.传输线末端至少有一个终端匹配3.使用能使多分支产生影响最小的布线拓扑结构4.最小化几何结构的不连续性产生反射:区域1,2交界面两侧电压,电流应该相等,否则两侧不等会产生无限大电场与磁场。

V1=V2,I1=I2,而,I=V /R,当区域阻抗不同时,关系式绝不会同时成立。

为平衡系统,交界处区域1侧产生反射回源端的电压,唯一目的就是吸收入射信号和传输信号之间不匹配的电压与电流。

满足的条件:且两区域应满足:代换即最终,得到反射系数ρ同样,可以推导出传输系数t没有确切的原因知道怎么产生反射电压,但知道反射电压会遵循上述关系,电压电流要保持连续阻性负载的反射假定传输线特性阻抗为50Ω,传输线的终端匹配有三种情况:5.传输线的终端开路,末端未连接。

末端瞬态阻抗为无穷大。

反射系数ρ为1。

例:6.传输线末端与返回路径短路,即末端阻抗为0。

此时反射系数ρ为-1,短路突变处测的电压为(入射电压与反射电压之和)0V。

7.特殊情况,终端阻抗等于传输线的特性阻抗,即匹配。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在AD出Gerber的时候,在layer选项下有2个栏,Layer to Plots和Mechanical layers to Add to All Plot. 一般情况下Mechanical layers to Add to All Plot.可以不予理会,此处的意思表示需要添加到任何层面的mechanical layers出Gerber的时候,如果没有删除room,有时会提示The film is too small for this PCB.因为room 会在角落离开PCB很远,但是gerber需要包含room的信息,如果gerber时候设置的film 的大小比较小,就会有这个问题。

如果有些object实在无法寻找,而需要的object比较好选择,可以ctrl+A,然后deselect需要的object,直接del即可将无法找寻的objectdel掉用PCB Inspector批量修改pad的soldermask expansion的时候,必须先勾选soldermask override,表示可以自定义soldermask expansion在Altium Designer里面设置内层pad和via的连接的时候,需要将pad设置为thermal,而via不需要,在设置all pad thermal connect以后,需要再add一个all direct connect的rule,优先级设置低于all pad thermal connect..否则所有的via将不会被连接到内层的plane低阻抗PDS的设计要点使GND与VCC尽量靠近 / 低电感值的去耦电容 / 封装assign多个寄生电感低的VCC与GND Via/常见的电磁干扰源差分信号转化为公模信号,在外部双绞线缆上输出PCB地弹在外部单端屏蔽线上产生公模电流。

附加的噪声可以由内部产生的辐射泄露溢出屏蔽罩引起做PCB NPTH的时候,可以在mechaincal 1层做一个NPTH,选中,Tool -> Convert -> Creat Board Cutout from Select Primitives可以在PCB上做一个针对所有层的Routing Keepout(not all electronical layer),首先在mechaincal 1 layer上做一个primitive,选中,Tool -> Convert -> Creat Cutout from Select Primitives在allegro中,框选一个封闭的line,可以compose 以line为外框的shape。

也可以选择一个unfill的shape,compose一个static shape返回路径是平面时是实现串扰最低的结构,一旦返回路径的平面发生变化,就会增加传输线之间的串扰上升沿时间与频率的关系:RT=1/10F其中:RT单位为ns,F的单位为GHz信号沿传输线传输,电压形成传输线之间的电场,电流形成传输线周围的磁场,传输线上信号的传播也是电磁波的传输。

信号的传输不仅传输电流和电压,同时还传播着电场和磁场单位长度导线的自感约为25nH/in圆形线圈的回路自感 L=32XRXIn(4R/D)nHR为线圈半径,D为导线直径,单位均为in在每个频率点,反射电压与入射电压之比称为S参数任何谐波的幅度都可以由V×2/(nπ)计算得出,V为最大电压值带宽用来描述频谱中有效的最高正弦波频率导体损耗和介质损耗,每种损耗过程对高频分量和低频分量的衰减是不一样的,所以以传输线传输的信号在到达load的时候信号的上升时间会有所改变在FR4介质上, 2G以下的频率的衰减不过-1dB,10G以上频率的衰减为-4dB带宽与上升时间的关系:BW=0.35/RT其中BW为带宽,单位为GHz; RT表示10%~90%的上升时间,单位为ns理想方波的谐波幅度下降的速度近似于1/f, 当实际波形的谐波幅度下降速度大于1/f的时候,此时谐波的频率即带宽电路中的振铃可能会使高频分量的幅度增加。

当波形出现振铃时,其带宽约等于振铃频率如果电流有理想方波的特性,尽管各次谐波的幅度已1/f的速度下降,但是由于共模电流的辐射是随着频率线性增加的,各次谐波的辐射能力也随着频率f上升,因此各次谐波对EMI 的影响都是相等的,为了减小EMI,应在设计中尽量减小信号的带宽。

带宽与时钟的经验公式BW=5 X F(以上升时间为7%周期为前提)测量的带宽指在带宽频率的范围内,测量得到的数据有比较好的精度。

注意与器件的带宽相区别。

模型的带宽指在带宽的范围内,利用模型可以得到比较精确的结果。

传输线带宽指用传输线传输信号,当信号传输损耗不影响系统工作时最高正弦波的频率传输线的3dB带宽:在实际应用中,传输线的带宽指传输的频率分量减小了3dB,也就是幅度减小为入射值的70%。

传输线的本征上升时间指传输线的带宽对应的最快上升时间。

比如传输线的带宽是1G,那么对应的传输线的最小的上升时间为RT=0.35/1G=0.35ns.,如果不考虑传输线带宽,一个信号的带宽是8G,对应的上升时间RT=0.35/8G=0.044ns,.当这个信号以1G带宽的传输线作为载体的时候,他的上升时间会受到传输线带宽的制约,具体的计算公式R tout=sqrt(RT in2+RT interconnect2)其中所有RT均为10%~90%的上升时间正弦电流与正弦电压之比不是正弦波,而是一些包含每个频率点上幅度的比值和相移的信息在频域中,阻抗所表示的相移指的是电压超前电流的相移随着频率的升高,流经电容器的电流(I=C×w×V×cos(wt))会增大流经电容的电流超前于电压π/4的相位,流经电感的电流滞后于电压π/4的相位。

实际零件模型的带宽很难计算,只能通过测量得到电阻值的计算公式R表示电阻值,单位 Ohmρ表示导线的体电阻率,单位为Ω.cmd表示互联线2端的距离,单位为cmA表示导线的横截面,单位为cm*cm直径为1mil, 长为80mil的键合线的电阻值大约为0.1 Ohm,键合线(铜)的单位长度的电阻大约是1 Ohm/in宽10mil,厚度为0.5 oz的铜导线的单位长度电阻是0.1 Ohm/in。

对于1oz的铜导线,电阻在20MHz处开始增加体电阻率与体电导率的积为1电阻率的单位是Ω.m,电导率的单位为Ω/m2个同心球面之间的电容为C=4πε*r*r1/(r1-r)ε:空间的介电常数,自由空间的介电常数为0.089pF/cm或者0.225pF/inr,r1: 球体的内外径,单位为cm或者in当内球面半径大于外球面半径10倍以上时候C=4πε*r(r为内球面半径)相对于某个表面,每个孤立的导体都有电容,这个电容不一定很小,而是有个与直径相关的最小值,导体距离附近的某个表面越近,他的电容量就越大。

通常1in的直径的球面电容量约为2pF平行板电容近似有一个前提条件,他假定了平行板周围的的边缘场效应是不存在的。

在实际中,考虑边缘场效应后,实际的电容量要大于近似值介电常数的本质是相对于空气的介电常数,所以是没有单位的,空气的介电常数为0.089pF/cm或者0.225pF/in。

介电常数越大,电容值越高。

水的介电常数约为80,同质固体材料介电常数会随频率的变化而变化,FR4从1KHz到10MHz,介电常数由4.8为4.4,而从1G到10G,介电常数就非常稳定了互联线中常用介质的相对介电常数多层板中存在的地与电源的平板电容,无法提供有效的去耦(相差3个数量级),他的作用只是为芯片和去耦电容提供低电感的路径如果线宽是介质厚度的2倍,介电常数为4,针对50 Ohm的传输线,则microstrip单位长度的电容C=2.7pF/in, Stripline的单位长度电容为3.5pF/in传输线厚度对传输线的寄生电容的影响是微小的传输线线宽的变化会影响微带线的有效介电常数,当线很宽时,大部分电力线都在介质中,这时有效介电常数约等于介质的介电常数。

当微带线的线宽比较小的时候,大部分的电力线都在空气中,此时有效介电常数会小于介质的介电常数若要求阻抗精度小于10%,则不能应用IPC关于阻抗的计算公式电介质不会对磁力线产生影响导线中电流愈大,导线越长,磁力线的匝数越多,磁场越强。

当导体中含有铁钴镍(铁磁金属,磁导率大于1)时,磁力线将显著增加,其他的任何金属都不会对磁力线产生任何影响电感是导体上流过单位安培电流时,导体周围磁力线的韦伯值L=N/IL表示电感,单位为HN表示电流导体周围的的磁力线匝数,单位为韦伯I是流过导体的电流,单位为安培此处应该深刻理解电感的定义,电感只与导体的几何结构有关。

影响电感的唯一因素就是导体的分布和在铁磁金属情况下导体的磁导率电感应与磁场强度区分开,电感源自导线上的电流,可以用比较具体的实物描述为以导线为轴心,有一定半径的圆柱体体积,导线越长,圆柱体越高,包含的体积越大,即电感越大。

影响电感的唯一因素是导体的分布和在铁磁金属情况时导体的磁导率导线周围的磁力线发生变化,则导线两端就会产生压降V=△N/△t△N标示磁力线的变化量,△t表示磁力线变化的时间当导线上电流发生变化时,电流的自感会发生变化,由于自感的变化而在导线上产生压降,这就是电流变化产生感应电压的原因V=△N/△t=L△I/△t=L(dI/dt)感应电压的极性可以根据原则判断:感应电压产生的感应电流将阻止导线上的电流的变化由电流变化产生的感应电压是所有有电感引起的信号完整性问题的根本原因串扰形成的原因是由于导线之间的互感,当其中一根导线的电流发生变化的时候,另一条导线的互感会发生变化,产生感应电压,从而对自身的信号产生影响,产生的噪声电压为Vnoise=M(dI/dt)Vnoise表示目标导线干扰电压M为两条导线之间的互感I为噪声源导线上的电流由于感应电压取决与电流变化速度,所以也用开关噪声此处所有电感均为局部电感直环形导线局部自感计算公式(精度优于几个百分点)L: 局部自感,单位为mHd:导线的长度,单位为inr: 导线的半径,单位为in从公式中可以看出,导体的局部自感与导体的长度成正比。

但是在实际中,还应考虑互感在新增长的导线上所起的增加的作用。

同时可以从上式看出,导体截面增大时,电感会减小,即电流越分散,局部电感就越小此处注意局部自感与局部互感的区别导线的局部自感大约为25nH/in或1nH/mm经验法则:从电容到via约50mil的线的局部自感约为1.2nH;板厚为64mil的过孔的局部自感约1.6nH。

局部互感当局部互感大于局部自感的20%时当导线的间距远大于导线长度时,两段导线的局部互感小于任意导线的局部自感的10%,这时互感通常可以忽略不计。