基于FPGA高速数据采集的解决方案

基于FPGA的高速数据采集系统设计

基于FPGA的高速数据采集系统设计武汉纺织大学毕业设计(论文)任务书课题名称:基于FPGA的高速数据采集系统设计完成期限: 2012年3月2日至2012年5月25日学院名称电子与电气工程学院专业班级电子082 学生姓名陈明秀学号 0803741084 指导老师王骏指导教师职称讲师学院领导小组组长签字一、课题训练内容采集系统的研制工作;以实现对模拟高频信号的处理和控制。

课题选用现场可编程逻辑器件FPGA技术,在Altera公司的Quartus II开发环境中应用VHDL 语言进行FPGA的编程与仿真,研究各模块的设计方法和控制流程,结合USB2.0总线接口技术,以期实现系统与PC机连接,在PC上对数据进行分析、显示和监控等,最后对系统性能指标进行验证。

1. 培养学生通过图书馆、互联网等资源查阅相关资料(包括外文资料),训练学生自主获得知识的能力和自学能力;2. 培养学生把所学的知识用于实践并引申到相关专业知识上,锻炼出自学能力;3. 锻炼学生外文阅读及翻译能力;4. 锻炼学生的自我创新能力;5. 在书写论文的过程中,锻炼学生的语言组织能力、逻辑思维能力、办公软件使用的能力;6. 培养学生与人合作、相互交流的能力。

二、设计(论文)任务和要求1. 大量收集与本课题有关的资料:到图书馆、各大书店寻找无线充电技术以及相关电路的资料,并认真进行阅读;到各大数据库和相关网站上搜索与本课题相关的学位论文和相关资料。

2. 第四周前上交毕业设计开题报告一份。

开题报告内容与学校模板要求一致,字数不少于2000字;经指导教师检查合格后才能进行后续工作。

3. 理清论文的总体思路,完成主要的研究工作:1)以CY7C68013为核心,设计一个FPGA的最小系统,并在此基础上通过编写VHDL程序进行系统的开发。

2)对数据采集,高频电路设计信号和电源完整性设计。

3)提高数据采集总体设计方案。

4)结合USB2.0接口的控制器CY7C68013芯片,采集系统进行硬件设计。

基于FPGA的高速数据采集器

内 尚 不 具 备 该 类 型 的 高 速 采 集 器 。 文 设 本

计 了一 种 基 于F GA的 高速 数 据 采 集 器 , P 由

当f m较大 时 , 往 对采 样 速 率f要 求 较 往 s

) 以准 确 地恢 复原 信 号 ( , 个过 可 f 这 )

, ‘ ,

高, 即需 要 A/ 转 换 器 采 样 速率 较 高 , D 这样 程 即 称 为 带 通 采 样 定理 。 如 果 用信 号 的 中 心 频 率 f = o 示 式 ()得 到 : 1,

1高速 数据采集理论及技术

括 采样 速 率 、 辨 率 、 储 量 和 实 时性 等 技 分 存

采样定理 和带通采样定理 。 术指标。 数 据 采 集 系统 发 展 的 趋 势 是 往 高速 高 1 1低通 采样 定 理 . 分 辨 率 方 向发 展 , 是 受 到 器 件 和 工 艺 的 但 指标 的限制 , 现高 速高分辨率 的采样 系 实 统 依然具有一 定的难 度。 目前 国 外 高 速 采 集 器的 采 样 速 率 可 以 达 到 几 十 G P 但 国 S S,

复。

限 制 , 别是 采 样 速 率 和 分 辨 率 这 一 矛 盾 理 , 特 假设 有 一 模 拟 信 号 x t , 带 宽 限 制 在 () 其

: 2 1 m

() 1 、

其 中 m 取 能 保 证 条件 ≥ ( 一 ) 2 的 最 大 正 整 数 , 得 到 的 采 样 离 散 序 列 则

信 号

A 4 03 T8 AS 0 作为采 样器 件 , 该芯 片是采 样速 率可 达到 l S S 分辨率 为l bt 采样后 的数 G P , Oi 。

据送  ̄F G ] I P A中 , 由于 采样 后数 据率 较 高 , 在

作品说明书(基于FPGA的新型高速PCI采集卡的设计)讲解

西北工业大学研究生创意创新种子基金作品说明书作品名称:基于FPGA的新型高速PCI采集卡的设计基于FPGA的新型高速PCI采集卡的设计摘要:从自主研发的角度,本设计通过板载FPGA实现了对16路模拟信号的采集及滤波处理,并将最终结果送入工控机。

其中关键技术是通过对FPGA编程开辟控制空间并实现具体滤波算法,上位机通过设置对应的控制空间实现对于16路AD采集通道的开启及不同滤波算法的调用。

采用PLX9052实现PCI的接口设计。

根据上述要求选用ALTERA公司的EP2C8Q208型号的FPGA。

关键词:采集卡,PCI,FPGA,滤波算法0、前言在现代工业领域,随着控制系统日益大型化,复杂的系统会给有用信号叠加许多高频噪声干扰。

如何滤除这些干扰,成为业内普遍关注的问题。

目前普遍使用的处理方式分为两种,利用硬件电路滤波和通过上位机软件滤波,但这两种方式均存在很多缺陷:(1) 通过硬件电路滤波,不仅会大大增加成本、占用宝贵的PCB面积,而且滤波效果不彻底,还会造成有用信号的相位偏移。

(2) 通过上位机软件滤波,要求具有很高的信号采集速度,一方面造成了数据传输量大的负担,另一方面在上位机执行滤波算法会占用控制资源,从而大大降低了控制效率。

为了解决以上问题,本作品设计了一种基于FPGA的新型高速PCI采集卡,通过FPGA对模拟信号进行高速的过采样,并针对信号类型进行算法可选的滤波处理,同时配合上位机的控制频率设计抽取算法,通过双端口RAM将数据通过PCI总线传至上位机。

这样既在下位机完成了滤波,又保证了信号传输速度,降低了数据传输量,从而大大减少上位机的运算量,提高控制程序的执行效率。

1、采集卡参数:1.1 AD采集:单通道采集频率可达1MSPS,可实现最多16通道的循环采集,循环采集频可达990KSPS。

采集范围为-10V~10V,采集精度实测可达到0.5‰。

AD采集内嵌滤波参数可选的8阶FIR滤波算法,截止频率在1~250KHZ之间可调,并可由软件测试界面进行设置。

基于FPGA的高速数据采集系统设计

基于FPGA的高速数据采集系统设计随着科学技术的不断进步,数据采集系统在许多领域都发挥着重要作用。

为了满足高速数据采集的需求,基于现场可编程门阵列(FPGA)的高速数据采集系统设计应运而生。

本文将介绍这一系统的设计原理和关键技术。

首先,我们需要了解FPGA的基本原理。

FPGA是一种可编程的硬件设备,可以根据需要重新配置其内部逻辑电路。

这使得FPGA在数据采集系统中具有极大的灵活性和可扩展性。

与传统的数据采集系统相比,基于FPGA的系统可以实现更高的采样率和更低的延迟。

基于FPGA的高速数据采集系统设计主要包括以下几个关键技术。

首先是模数转换(ADC)技术。

ADC是将连续的模拟信号转换为数字信号的关键环节。

在高速数据采集系统中,需要使用高速、高精度的ADC来保证数据的准确性和完整性。

其次是FPGA内部逻辑电路的设计。

为了实现高速数据采集,需要设计高效的数据处理逻辑电路。

这些电路可以实现数据的实时处理、存储和传输等功能。

同时,还需要考虑电路的时序约束和资源分配等问题,以确保系统的稳定性和可靠性。

另外,时钟同步技术也是高速数据采集系统设计的重要内容。

在高速数据采集过程中,各个模块需要保持同步,以确保数据的准确性。

因此,需要设计合理的时钟同步方案,保证各个模块在同一个时钟周期内完成数据的采样和处理。

最后,还需要考虑系统的接口和通信问题。

基于FPGA的高速数据采集系统通常需要与其他设备进行数据交互,如计算机、存储设备等。

因此,需要设计合适的接口和通信协议,实现数据的传输和存储。

综上所述,基于FPGA的高速数据采集系统设计涉及多个关键技术,包括ADC技术、FPGA内部逻辑电路设计、时钟同步技术以及接口和通信问题。

通过合理的设计和优化,可以实现高速、高精度的数据采集,满足现代科学研究和工程应用的需求。

这将为各个领域的数据采集工作带来巨大的便利和发展空间。

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

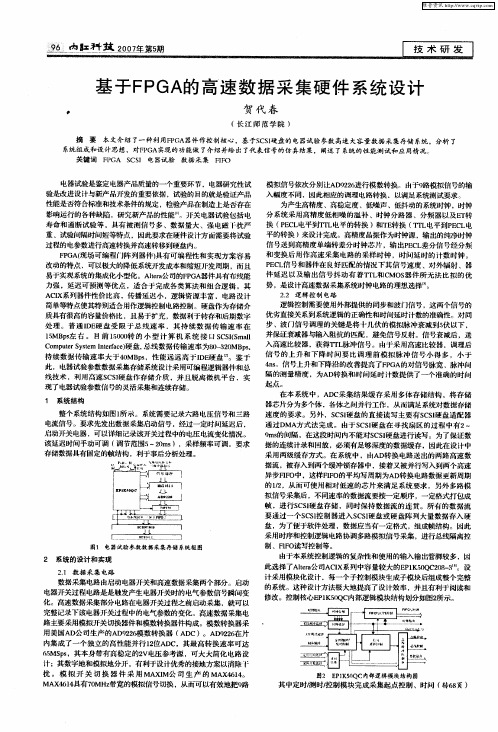

基于FPGA的高速数据采集硬件系统设计

关 键 词 F GA CS 电器试 验 P S I 数 据 采 集 FF IO

电器试验是鉴定 电器产 品质量的—个重要环节 ,电器研究性试

模拟信号依次分别 [A 9 2 进 行模 数转换 。由于9 I D 26 z 路模拟信 日的输 . 入幅度不同 .因此 相应 的调理电路转换 .以满足系统 测试要求 。 为产生高精度 、高稳定度 、低噪声 、低抖动的系统时钟 ,时钟 分系统 采用高精度 低相噪的温 补 、时钟分路器 、分频器 以及E 转 T 换 (E L P C 电平 到 r 电平 的转 换 ) E L 和T 转换 ( r 电平 ̄ P C 电 L J IE L

1MB s 右 。 目前 1 00 的 小 型 计 算 机 系统 接 口S S(m l 5 p左 50 转 C I a S l C m u r yt t f e o pt s mI e a ) e S e n r c 硬盘 . 总线数据 传输速率 为8 一 2 MB s O 3 0 p. 持续 数据传 输速 率大  ̄ 4 MB s :0 p ,性 能远远 高 于l E D 硬盘 。鉴 于 此 ,电器试验参数数据采集存储系统没 汁采用可编程逻辑器件和总

势 ,是设计高速数据采集系统时钟 电路 的理想选择 。 。

22 逻 辑 控 制 电路 .

逻辑控制需要使用外部提供 的同步和 波门信 号, 两个信号 的 这 优 劣直接关系到系统逻辑的正确性和时 问延时 计数的准确性 。对 同 步 、波门信号调理 的关键 是将十儿伏 的模拟脉 冲衰 减到5 以下 , 伏 并保证衰减器与输入阻抗的匹配 ,避免信号反射 。信号衰减后 ,送 入高速 比较器 ,获得T L T 脉冲信号 。由于采用高速比较器 ,调理后 信 号 的上升 和 下降 时 问要 比调 理 前模 拟脉 冲信 号小 得 多 ,小于 4s n 信号上升和下降沿的改善提高 了F G 的对信号脉宽 脉冲间 PA 隔的测 量精 度 ,为A 转 换和时间 延时 汁数提供 了一个 准确的时问 D

基于FPGA的高速数据采集讲解

IFCLK

FADRR0

FADDR1

FLAGB-FULL

FLAGC-EMPTY

SLWR

FD[15:0]

Z

PKTEND

N

N+1

IFCLK FADDR0 FADDR1 FLAGB-FULL FLAGC-EMPTY SLWR FD[15:0] PKTEND

Core Auto Commits Pkt

2.77

输入信号峰峰值给定是4.0V 示波器上显示为4.04V

示波器显示频率(HZ)

100

200

500

1K

2K

LABVIEW显示频率(HZ) LABVIEW显示VPP(V) 示波器显示频率(HZ)

100.0 3.98

5K

200.5 499.3 998.3

3.98

3,99

3.99

10K

50K

100K

目前,随着微电子技术的发展,电子自动化设计工 具的普及,大规模可编程逻辑器件也越来越得到广泛的 实际应用。可编程逻辑器件不仅使系统趋于小型化、集 成化和高可靠性,而且具有用户可编程特性,这些优点 将缩短系统设计周期,减小设计成本,降低设计风险。 不仅如此,部分器件除具有用户可编程能力外,还具有 简单的在线可编程能力。

100.1 3.01

5K

199.8 499.6 1000.2 1996.7

3.01 3.09 3.02

3.04

10K

50K

100K

200K

LABVIEW显示频率(HZ) LABVIEW显示VPP(V)

5008.3 9992.4 50000 100168 200360

3.05

基于FPGA的高速图像采集系统设计.

基于FPGA的高速图像采集系统设计引言在低速的数据采集系统中,往往采用单片机或者DSP进行控制;而对于图像采集这种高速数据采集的场合,这种方案就不能满足需要。

因此这种方案极大浪费了单片机或DSP的端口资源且灵活性差;若改用串口方式收集数据,则一方面降低了数据采集的速度,另一方面极大地耗费CPU的资源。

本系统采用FPGA作为数据采集的主控单元,全部控制逻辑由硬件完成,速度快、成本低、灵活性强。

为了增加缓冲功能,系统在FPGA外扩展了256Mb的RAM,不仅增大了缓冲区容量,而且极大地降低了读写频率,有效地减轻了上位机CPU的负担。

在图像数据接口中,比较常见的是VGA、PCI—Express,而这些接口扩展性差、成本高。

本系统采用高速的USB接口作为与上位机通信的端口,速度快、易安装、灵活性强。

1 系统框图系统框图如图1所示。

FPGA控制单元采用A1tera公司Cyclone II系列的EP2C5F256C6,主要由4个部分组成——主控模块、CMOS传感器接口、RAM 控制器以及EZ—USB接口控制器。

传感器接口负责完成SCCB时序控制,RAM控制器用于实现RAM读写与刷新操作的时序,USB接口模块完成主控模块与EZ—USB之间的数据读写;而主控模块负责对从EZ—USB部分接收过来的上位机命令进行解析,解析完命令后产生相应的信号控制各个对应模块,如CMOS传感器传输的图像格式、RAM的读写方式、突发长度等。

2 OV7620模块设计图像传感器采用OV7620,接口图如图2所示。

该传感器功能强大,提供多种数据格式的输出,自动消除白噪声,白平衡、色彩饱和度、色调控制、窗口大小等均可通过内部的SCCB控制线进行设置。

OV7620属于CMOS彩色图像传感器。

它支持连续和隔行两种扫描方式,VGA与QVGA两种图像格式;最高像素为664×492,帧速率为30fps;数据格式包括YUV、YCrCb、RGB三种。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA 高速数据采集的解决方案于 1,肇云波2(1.贵州大学通信工程学院 贵州贵阳 550003;2.沈阳理工大学 辽宁沈阳 110168)摘 要:随着接口速度和带宽的不断提高,有必要对高速数据采集问题进行研究。

如何在高接口速率的情况下正确采集到有效的数据,成为目前要解决的问题。

解决此问题的方法是采用Xilinx Virtex 4FP GA 的ChipSync 或Altera Stratix ⅡFP GA DPA (动态相位调整)两种不同技术,并介绍了Altera DPA 技术在高速源同步接口的实际设计过程。

使用这两种技术的结果是在数据速率达到1Gb/s 时,完成对有效数据的正确采集。

关键词:源同步;FP GA ;ChipSync ;DPA中图分类号:TP355+14 文献标识码:B 文章编号:1004373X (2007)0514504High Speed Data Acquisition B ased on FPG AYU Xuan 1,ZHAO Yunbo 2(munication Engineering College ,Guizhou University ,Guiyang ,550003,China ;2.Shenyang Ligong University ,Shenyang ,110168,China )Abstract :With the interface speed and bandwidth is constantly increasing ,it is important to undertake a study of high 2speed data acquisition.How to collect the high rate of correct data effective is the current problem should be solved.One way is using Chip Sync of FP GA Xilinx Virtex4or DPA (dynamic phase adjustment )of the Altera Stratix ⅡFP GA which are two different technical approaches.We introduced the actual design process of Altera DPA technology in high 2speed source syn 2chronous interfaces.The results of using both techniques show that it could complete the effective collection of the correct data at 1Gb/s data rates.K eywords :source synchronization ;FP GA ;Chip Sync ;DPA收稿日期:20060726 当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此。

随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能宽,动态范围要尽可能大,以便得到更宽的频率搜索范围,获取更大的信息量。

因此,通信系统对信号处理前端的A/D 采样电路提出了更高的要求,即希望A/D 转换速度快而采样精度高,以便满足系统处理的要求[1]。

随着系统时钟的不断提高,系统同步的收发两端的时钟延迟不能得到有效地解决,因此提出采用源同步接口设计的解决方案。

在数据接口速度和带宽的不断提高,数据有效窗口不断缩减的情况下,源同步接口无法采集到正确数据,因此在信号余量不断缩减的情况下,采用Xilinx Virtex 4FP GA 或Altera Stratix ⅡFP GA 的两种不同技术解决如何正确地采集数据的问题是有效的,并在SPI 412高速源同步接口上得到广泛的应用。

1 系统同步与源同步的简述1.1 系统同步与源同步系统同步中多个部件在同一个系统时钟下同步工作,各个部件之间的通道只传递数据,数据的时序关系以系统时钟为参考,在常见的电子系统中通常采用系统同步设计方式。

系统同步设计具有部件间各系统全局同步工作的特点,但是在部件之间高速传递数据时接口收发两端的时延比较难确定,因此不太适合高速的芯片间的接口设计。

源同步系统中每两个部件之间数据单项或双向传递,在和数据同向的传递方向上同时传一个和数据保持特定相位关系的参考时钟,在数据的源端,参考时钟和数据保持确定的相位关系,而在数据的目的端,另外一个部件可以根据参考时钟的相位来准确捕获对应的数据。

源同步接口是相对系统同步接口而言的,通常存在于两个芯片之间的局部,他的时钟和数据之间关系是局部的、是准确的,时延模型得到了进一步的简化,因此非常适合高速芯片间的接口设计。

随着系统互连的带宽的需求的不断增长,源同步接口逐渐成为主流,得到了广泛的应用。

目前SFI 24(SERDES 到“成帧器”的接口)和SPI 412(系统信息包接口,level4,phase2)接口已经采用了源同步互连的接口,而且接口带宽可达到16GHz 。

电信网络中SPI 412,SFI 24和XSBI 和大量的高速存储器DDR SDRAM ,DDR2SDRAM ,QDR ⅡSRAM ,PLDRAM Ⅱ已广泛采用源同步设计技术。

5411.2 源同步目前面临的挑战虽然源同步技术被广泛的应用,但他在数据速率非常高时就会出现问题。

在数据速率达到1Gb/s 时,由于数据与数据之间的偏斜,数据与时钟之间的偏差,加上PCB 走线的影响,尤其是信号连接器的容性阻抗的不一致,都会加剧时钟与数据之间的偏差,导致有效采样窗口逐渐变小,以至于时钟信号在管脚处根本找不到一个有效的能把并行数据一次采样进来的采样窗口。

下面的例子是单项差分源同步接口设计中数据有效窗口的典型值,数据速率为800Mb/s DDR 数据时,有效周期为1125ns ,数据的有效窗口通常只有60%(如图1所示)。

数据速率为1Gb/s DDR 时,数据有效周期为1ns ,而数据的有效窗口通常只有45%(如图2所示)。

可以发现数据有效窗口的缩减比有效周期的缩减要快,因此接口数据率越高,数据有效窗口变短,这就增大了源同步设计的难度。

图1 800Mb/s 数据有效窗口与数据的有效周期图2 1Gb/s 数据有效窗口与数据的有效周期2 解决方案在源同步接口设计中,在数据接口速度和带宽的不断提高,数据有效窗口不断的缩减的情况下,无法采集到正确数据。

因此在信号余量的不断缩减的情况下,采用Xil 2inx Virtex 4FP GA 和Altera Stratix ⅡFP GA 的两种不同技术解决此问题。

2.1 时序余量(Timing Margin )在一个同步设计中,时序是同步系统正常工作的关键因素。

特别在高速系统设计中,所有的时序路径延时都必须在系统规定的时钟周期以内,如果某一个路径超出了时间限制,那么整个系统都会发生故障.应用Xilinx Virtex 4FP GA 和Altera Stratix ⅡFP GA 的两种不同技术解决问题时,一定要特别注意时序余量计算的问题。

在计算设计内部的时序余量时,必须要考虑的一些延时因素:源触发器的时钟到输出口延时t co ;触发器到触发器的走线及逻辑延时t logic ;目的触发器的建立时间t su 和保持时间t h 。

假设设计规格需要的时钟周期为T ,因此需要满足时钟建立的要求:t co +t logic +t su ≤T(1) 同样也需要满足目的端触发器的保持时间t h 要求。

在同步接口的设计中,另一个需要重点考虑的就是FP GA 和周围(上游和下游)器件的接口时序。

由于芯片I/O 管脚的输入输出存在相对较大的延时,同时还涉及到和时钟信号之间的相位关系,所以接口电路的时序往往成为设计中的难点。

在计算同步I/O 管脚的时序余量时,用户通常会考虑发送器件的时钟到输出延时T co ,单板走线延时T fight ,以及接收器件的建立时间T su 和保持时间T h 。

假设设计规格需要跑的时钟周期是T ,需要满足:T co +T fight +T su ≤T(2) 同样也需要满足接收器件的外部保持时间T h 的要求。

在一个实际的系统中,把同一个时钟源分布到不同的时钟目的端的延时差叫做t skew (如果到源端触发器比到目的触发器延时小,t skew 为正值,否则为负值)。

而时钟沿的到达时间也会与理想情况有一些差别,这里把理想的时钟周期与实际的时钟周期的差别叫做t jitter (如果理想的时钟周期大于实际的时钟周期,t jitter 为正值,否则为负值)。

如果时钟信号的下一个有效边沿超前于预定时间到达,这样时钟的有效周期缩短,而在这个时钟周期内,电路同样需要正常工作。

这样,在考虑时序余量时,就需要把时钟的偏斜和抖动计算在内,满足:t co +t logic +t sy ≤T +t skew -t jitter(3) 与此类似,在考虑同步I/O 接口时序时,也必须考虑单板上时钟分配系统之间的偏斜以及时钟抖动。

2.2 Xilinx 的Chip Snyc 技术与Altera 的DPA 技术Xilinx 的ChipSnyc 技术与Altera 的DPA 技术所完成的功能都是为了在高速数据率的情况下,实现源同步的数据传输,只是中间实现比特对齐的环节不同。

Xilinx 的ChipSnyc 技术采用75ps 为粒度的64级延迟线,并采用系统状态机来实现比特对齐,而Altera 的DPA 技术采用快速锁相环(Fast PLL )产生的8个以45°为粒度的相位,他的相移值是由快速锁相环的输出频率控制的,快速锁相环的最高输出频率为1GHz ,可以实现01125ns 为粒度8级延迟线,因此时延的精度没有Xilinx FP GA 的高。

2.2.1 Xilinx Virtex 4系列FP GA用Xilinx Virtex 4系列FP GA 的Chipsync 实现在数据有效窗口的正中央采集数据,可获得更大的时序余量。

在Virtex 4管脚和逻辑之间嵌入一个叫ChipSync 的关键电路,他由ISERDES ,OSERDES ,时钟组成。

ISERDES 为输入方的串行和解串行电路,主要有分频、比特和字对齐电路;OSERDES 为输出方的串行和解串行电路,主要有倍频电路;时钟为局部的时钟,主要有具有时钟能力的I/O 。

(1)Xilinx Virtex 4ChipSync 系统结构Xilinx Virtex 4中的ChipSync 由Idelay 、控制Idelay的系统状态机、Idelay 的控制模块、200M Hz 的校准时钟组成(如图3所示),这些部件配合起来工作可保证精准的641大约75ps 为粒度且共有64级的延迟线,可实现时钟和数据的比特对齐。