一种基于锁相环的数字频率合成器的设计(1)

数字锁相环的频率合成器设计

数字锁相环的频率合成器设计摘要:近几年来,无线通讯获得飞速发展。

随着其应用领域的不断扩张,市场对低功耗、低造价、高性能、高集成度的收发机的需要也越来越高。

在无线通信收发机中包含一个很重要的模块,频率合成器,它通过产生一系列与参考信号具有同样精度和稳定度的离散信号,为频率转换提供基准的本地震荡信号。

频率合成器设计的优劣直接影响到无线通信收发机的性能、成本,故其实现方式一直是一个挑战。

而本次课程设计仅考虑方案的实用性,即是实验室环境的局限性以及电子器件的价格等因素。

关键词:数字锁相环,分频,频率合成器一、选题的背景与意义随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。

数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还具有对离散样值的实时处理能力,已成为锁相技术发展的方向。

锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号是离散的数字信号,而不是模拟电压,因而受控的输出电压的改变是离散的而不是连续的。

本文主要介绍了仿真技术的概念、特点、发展情况及其在控制系统的应用;分析了MATLAB/SIMULINK的功能及如何在MATLAB语言提供的仿真环境SIMULINK 下实行控制系统的仿真,并对数字锁相环进行仿真。

利用计算机对控制系统进行仿真与分析,是研究控制系统的重要手段;MATLAB软件、MCGS组态软件可成功地用于控制系统的仿真、分析及监控,在科研、生产和教学等领域具有广泛的应用前景和推广价值,从上面两方面看来,本课题数字锁相环技术的matlab/simulink仿真具有一定的研究价值。

二、研究内容与拟解决的主要问题本设计从模拟锁相环研究出发,掌握锁相环的基本工作原理,了解环路失锁、捕获、跟踪过程及环路锁定条件等。

掌握数字锁相环的工作原理,并用MATLAB语言对该系统进行设计,给出数字锁相环电路各个主要模块的设计过程及仿真结果,得到该系统的顶层电路。

基于锁相环的频率合成器的设计

基于锁相环的频率合成器的设计随着现代技术的进展,具有高稳定性和精确度的频率源已经成为通信、雷达、仪器仪表、高速计算机及导航系统的主要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模的进展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高精确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环频率合成器的原理1.1 锁相环原理锁相环(PLL)是构成频率合成器的核心部件。

主要由相位(PD)、压控(VCO)、环路(LP)和参考频率源组成。

锁相环是一种利用外部输入的参考信号控制环路内部振荡信号反馈控制。

他的被控制量是相位,被控对象是压控振荡器。

1所示,假如锁相环路中压控振荡器的输出信号频率发生变幻,则输入到相位比较器的信号相位θv(t)和θR(t)必定会不同,使相位比较器输出一个与相位误差成比例的误差Vd(t),经环路滤波器输出一个缓慢变幻的直流电压Vc(t),来控制压控振荡器输出信号的相位,使输入和输出相位差减小,直到两信号之间的相位差等于常数。

此时,压控振荡器的输出信号频率和输入信号频率相等,且环路处于锁定状态。

1.2 锁相环频率合成器原理2所示,锁相环频率合成器是由参考频率源、参考分频器、相位比较器、环路滤波器、压控振荡器、可变分频器构成。

参考分频器对参考频率源举行分频,输出信号作为相位比较器参考信号。

可变分频器对压控振荡器的输出信号举行分频,分频之后返回到相位比较器输入端与参考信号举行比较。

当环路处于锁定时有f1=f2,由于f1=fr/M,f2=fo/N,所以有fo=Nfr/M。

只要转变可变分频器的分频第1页共3页。

锁相式数字频率合成器设计

信息科学与技术学院通信原理课程设计课题名称:数字频带通信系统的建模与设计学生姓名:王太程2011508199学院:信息科学与技术学院专业年级:电子信息工程2011级指导教师:钟福如讲师完成日期:二○一四年七月十日目录第0章引言 (2)第1章 (4)1.1 设计任务要求及方案论证 (4)1.1.1 任务要求 (4)1.1.2 锁相环频率合成的原理 (4)1.1.3锁相环频率的合成与应用(调制与解调) (6)1.1.4锁相环在调制中的应用 (7)1.1.5 锁相环在解调中的应用 (8)1.1.6 锁相环在频率合成电路中的应用 (9)1.2 仿真工具SYSTEMVIEW简介 (9)1.3 电路的设计与调试 (10)1.3.1 三环式锁相环频率合成电路 (10)第2章 (12)2.1 仿真的结果及分析 (12)第3章 (14)参考文献 (15)第0章引言锁相环(Phase Lock Loop),简称PLL,是一种利用外部输入的参考信号控制环路内部振荡信号反馈控制电路。

他的被控制量是相位,被控对象是压控振荡器。

如果锁相环路中压控振荡器的输出信号频率发生变化,则输入到相位比较器的信号相位θv(t)和θR(t)必然会不同,使相位比较器输出一个与相位误差成比例的误差电压Vd(t),经环路滤波器输出一个缓慢变化的直流电压Vc(t),来控制压控振荡器输出信号的相位,使输入和输出相位差减小,直到两信号之间的相位差等于常数。

此时,压控振荡器的输出信号频率和输入信号频率相等,且环路处于锁定状态。

锁相环是构成频率合成器的核心部件。

主要由相位比较器(Phase Discriminator)、压控振荡器(Voltage Control Oscillator)、环路滤波器(Loop Filter)组成。

锁相环路是一个能跟踪输入信号相位的闭环自动控制系统。

锁相环路系统在各个领域都有很多的用途,发展将势不可挡。

锁相环路在宇宙飞行目标的跟踪、遥测和遥控、电视接收机、电动机转速控制、自动跟踪调谐等领域都有更好的发展。

基于单片机的锁相环频率合成器设计

基于单片机的锁相环频率合成器设计摘要:本文介绍了一种基于单片机的锁相环(PLL)频率合成器设计。

该频率合成器采用了数字式频率合成技术,可实现在1MHz至40MHz的频率范围内的频率锁定。

系统采用C8051F340单片机作为主控芯片,通过程序控制实现倍频器、除频器和加减频器的频率合成,而将合成后的频率与参考信号进行比较并通过反馈控制调整产生高精度、稳定的合成信号。

实验测试表明,该频率合成器具有良好的稳定性和合成精度。

关键词:锁相环,频率合成器,单片机,数字式频率合成,反馈控制Abstract:This paper describes a design of phase-locked loop (PLL) frequency synthesizer based on single-chip microcontroller. The frequency synthesizer integrates the digital frequency synthesis technology and can achieve frequency lock within the frequency range of 1MHz to 40MHz. The system usesC8051F340 single-chip microcontroller as the main control chip, which controls the frequency synthesis of the multiplier, frequency divider and adder/subtractor through programming. The synthesized frequency is compared with the reference signal and feedback control is used to adjust the generated frequency to achieve high-precision and stable synthesis signal. Experimental tests show that the frequency synthesizer has good stability and synthesis accuracy.Keywords: Phase-locked loop, frequency synthesizer, single-chip microcontroller, digital frequency synthesis, feedback control正文:引言锁相环(PLL)频率合成器是一种常用的高频信号源。

基于CD4046锁相环的数字频率合成器电路设计

文章编号 : 1 6 7 4 - 4 5 7 8 ( 2 0 1 3 ) 0 5 - 0 0 0 9 - 0 3

应 用 实 践

基于 C D 4 0 4 6锁 相 环 的 数 字频 率 合 成 器 电路 设 计

刘艳红

( 国营第七 八五 厂 , 山 西 太原 0 3 0 0 2 4 )

定时器产生 的电信号作为输入信 号 ( 参 考信号 ) f i 输入 4 0 4 6

相位 比较器一端 , 从 压控 振荡 器输 出信 号 f n经 可预置 分频 器( J 7 、 r 分频 ) 合 成后 得反 馈信 号 f b加 到相 位 比较 器 的另 一 端, 两个输入信号在相 位 比较 器 中进行 相位 或频率 比较 , 然

信号处理技术 , 它能严格跟踪相干信号频率 。利用锁 相环构 成的频率 合成 器电路结构 简单 , 输 出频率 成分 频谱 纯度 高 ,

是一个较好的频率 转换 系统 。

1 电路总体 设计 思路

该锁相环数字频率合成器 实现的主要 技术 指标为 : 输 入 频率 f i =1 0 0 H z ; 输 出频率 f o =1 0 0 H z ~9 9 . 9 k H z ; 分频 系数 Ⅳ为 1— 9 9 9之间的任意整数。其 总体框 架如图 1所示 :

摘 要: 主要介绍 C D 4 0 4 6锁相环 数字频率合成器的构成 电路及原理 。C D 4 0 4 6锁相 环数 字频 率合成 器主要 由 振荡源电路 、 1 / N可预置分频 器以及锁相 环电路 构成。其功能是将一给定 频率的输入信号 经频 率合成后产 生一 系 列的 Ⅳ倍频 率的输 出信号 。此频 率合 成器具有 系统稳定 、 精确度 高、 较 高的可选择 性与实用性等特 点。 关键词 : 频率合成 ;锁相环 ;C D 4 0 4 6 ;分频 器 中图分类号 : T N 7 4 2 . 1 文献标识码 : A

一种级联锁相环频率合成器的设计与实现

一种级联锁相环频率合成器的设计与实现随着信息科技的发展,频率合成技术变得越来越重要。

由于频率合成器不仅能够提供精确控制的信号,而且具有高灵敏度、高精度、高稳定性和可靠性等优越特性,在很多领域,尤其是语音和数据传输领域,频率合成器被广泛应用。

级联锁相环(Cascaded Phase-Locked Loop,CPL)技术是一种先进的频率合成技术,能够提高抑制失真的能力,降低合成器的时钟数量,改进合成器的频率设计和合成器的工作稳定性。

因此,研究一种基于CPL技术的频率合成器具有重要意义。

本文以一种基于CPL技术的频率合成技术为研究对象,主要包括三个部分:基本原理、技术设计和实验验证。

首先,介绍CPL技术及其基本原理,着重介绍锁相环结构、锁相技术和差分分频结构等技术要素,并结合实际应用场景分析其优点和缺点。

其次,讨论多级CPL 合成器的技术设计,指出本研究中采用的多级CPL结构,分析各部分的构建原理,给出各部分的参数设定及其实现方法,并阐明其和其他结构的不同。

最后,给出通过FPGA实现本研究基于CPL技术的合成器系统,并对其进行实验验证,从实验结果可以看出,相比于传统合成器,本研究的基于CPL技术的合成器系统,具有较高的频率精度和稳定性,在信息传输领域有着更高的应用价值。

从以上内容可以看出,基于CPL技术的频率合成器已经成为一种先进的合成技术,具有抑制失真、降低合成器时钟数量、改进合成器频率设计及工作稳定性等优越性能,它受到了电子行业及其他行业的高度重视。

未来,将结合实际应用不断优化之前的CPL技术,构建更

先进的CPL合成器,并将其运用于更广泛的领域,以满足用户不断变化的应用需求。

一种基于锁相环的数字频率合成器的设计

入信号 , 后经固定分频电路 分频 , 成为 P D一端的输 人参考频率 F 。 C V O的输出信号频率 经可预置分频 器进行 J 分频后输入 P 7 v D的另一端。这两种信号进行 比 较, 当其有相位差时 ,D便 向低通滤波器 ( P ) 出一 P LF 输 个对应 于 相位 差 的误差 电压 。L F将误 差 电压 中 的高 频 P 分量和噪声滤除 , 并向 V O输送一个控制 电压 , C 使 发 生改变 , 从而使 P D的输入相位差逐渐消失, 使锁相环路

( 西安近代化学研究所 , 陕西 西安 7 0 6 ) 10 5

摘 要: 现代电子技术对信 号源频率 的准确度 、 稳定度要求愈来愈高 , 而一个信 号源输 出频率的精度建立在主振器的稳定度上 。当前产生高精度 , 高

稳定度的频率源主要是 石英晶体振荡器 和原子振荡器等 。然而它们只能产生单一 的频率 。 且造价 昂贵 。于是 , 本文设计出一种数 字锁相环频率合成 器 。它能够输出若干高精度 。 高稳定度 的, 可调 的频率值 。 具有 电路简洁 , 操作方便 , 造价低 廉等优点 。本设计 可广泛应用 于需要输 出稳 定的信号频 率 的场合 。 关键词 : 数字锁相环 ; 分频 ; 频率合 成器

最 终锁 定 。这 时 , : 有

f

=

f

,

图 2 套 环 式 振 荡 器

即有 = ‘ / = ‘ NM N

此 电路 易 起振 , 采用 一 块 “ 非 ” 电路 。前 三 级 它 与 门

可见 随 』 v的变化而改变 , 从而实 现频率输 出可

调 的 目的。

门电路组成无稳 态振荡器 。最 后一个 门电路作缓 冲输 出 。由 尺 , 。尺 , 2 英 晶体及 第二 个 门组成 的第 二个 。C ,:c 石

基于cd4046锁相环的数字频率合成器电路设计

基于cd4046锁相环的数字频率合成器电路设计1. 介绍在当今的数字电子领域,频率合成器扮演着至关重要的角色,它可以将一个基础频率信号合成出多个频率信号,广泛应用于收音机、数字通信、无线电、雷达等领域。

本文将重点讨论基于cd4046锁相环的数字频率合成器电路设计,以及CD4046的基本工作原理和性能特点。

2. 基础原理CD4046作为一种锁相环集成电路,它由相位比较器、环路滤波器和振荡器组成。

在频率合成器中,CD4046可以将输入信号频率合成成另一个输出频率信号,并且具有较高的信号锁定能力。

其基本工作原理是根据输入信号频率与振荡器输出信号频率之间的差值,不断调节振荡器输出频率,直至二者频率相同,从而实现信号的合成。

3. 设计步骤(1) 确定合成频率范围:根据实际需求确定所需合成频率范围,进而选择合适的分频倍数和振荡器参数。

(2) 选择振荡器电路:根据合成频率范围选择合适的振荡器电路和频率合成器芯片,CD4046是目前较为常用的选择之一。

(3) 进行电路仿真:使用电路仿真软件对设计电路进行仿真和调试,确保电路工作稳定和合成频率准确。

(4) 调节环路参数:根据实际需求调节环路参数,如环路带宽和环路增益,以实现更精准的频率合成效果。

4. 性能分析CD4046锁相环具有较高的抗干扰能力和频率稳定性,能够在一定程度上抵抗外部环境干扰和波动。

其响应速度较快,能够实现快速锁定输入信号频率,并且具有较高的合成精度和稳定性,适用于多种频率合成场景。

5. 个人观点在设计数字频率合成器时,选择合适的频率合成器芯片对电路性能起着至关重要的作用。

CD4046锁相环作为一种可靠的集成电路芯片,具有较高的性能和稳定性,是设计高质量数字频率合成器的重要选择之一。

在实际应用中,需要根据具体需求合理设计振荡器电路和调节环路参数,以实现更加精准和稳定的频率合成效果。

总结:本文对基于CD4046锁相环的数字频率合成器电路设计进行了全面评估和探讨,介绍了其基本工作原理、设计步骤、性能分析和个人观点,并对其在数字频率合成器设计中的重要性进行了强调。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

)

θ r

(

S

)

=

1

G (S) + G (S)

/N

式中 G ( S )是开环传递函数 ,且

G ( S ) = KV ·F ( S ) /S

KV = Kd Ko /N 112 初步估算

举例说明 ,假设设计的要求为

( a)频率范围 ( fo ) : (10~1000) KHz; ( b)频率分辨力 : 10KHz;

则 M = fI / fref = 4000 /10 = 400。 2 单元电路的设计

211 晶振电路的设计

本设计中的晶体振荡电路采用套环式振荡器电路 ,

如图 2所示 。

图 2 套环式振荡器

此电路易起振 ,它采用一块“与非 ”门电路 。前三级 门电路组成无稳态振荡器 。最后一个门电路作缓冲输 出 。由 R1 , C1 , R2 , C2 石英晶体及第二个门组成的第二个 内环 ,可提供一个接近晶体谐振频率的振荡频率 ,并呈现 电容性 。

fI M

=

fo N

, 即有

:

fo

= fi ·N /M

= N ·fref

可见 , fo 随 N 的变化而改变 ,从而实现频率输出可 调的目的 。

设上图中 PD 的增益为 Kd , LF的传递函数为 F ( S ) , VCO的增益系数 Ko ,则可得到单环锁相频率合成器中环

路的闭环传递函数为

θ o

(

S

36

《计量与测试技术 》2006年第 33卷第 6期

一种基于锁相环的数字频率合成器的设计

D esign of F requency S yn thes ize r B ased on D ig ita l P hase L ocked L oop

张红武 李 菲

(西安近代化学研究所 ,陕西 西安 710065)

作者简介 :严宏剑 ,男 ,助理工程师 。工作单位 : 新疆阿克苏地区质量与计 量检测所 。通讯地址 : 843000 新疆阿克苏市英巴格路 12号 。 收稿时间 : 2006 - 03 - 28

(上接第 37页 )

图 6 CD4046的环路滤波器

3 总体电路的测试 晶振电路实测的输出信号频率为 3199992MHz。当

LF是线性低通滤波器 ,其功用是滤除 PD 输出误差

电压信号中的高频分量 ,起到平滑作用 ,以保证环路的稳

定性 ,改善环路的跟踪性能和噪声特性 。

本设计中采用图 6所示的无源比例积分滤波器 。其

时间常数 τ = ( R1 + R2 ) C1 , 通常选择 R2 取值为 R1 的

10% ~30% ,这既可消除环路的过激和振荡 ,又有较快的

图 3 固定式分频器

4518中一块电路级联最大可记数到 99,可用作固定 分频器 。4518中输入脚是复零端 RA 和 RB ,时钟输入端 CKA 和 CKB ,时钟选通端 CEA 和 CEB 。用 Q 输出兼作进 位 。复零端不用其功能时就接地 。进位取自 Q4 的下跳 边沿送往下一级 CE端去计数 ,更多位的级联均可如此 处理 。CKA 送入计数时钟 ,上跳边沿完成计数 (这时 CEA 须加高电平 ) 。 213 可预置式分频器的设计

图 5 数字锁相环 4046的管脚功能框图

CD4046 外 围 的 阻 容 元 件 R1 , R2 和 C1 的 选 择 对 VCO 的振荡频率以及线性度有着直接的影响 。若采用

补偿电阻 R2 时 (R2 ≠∞) , VCO 的频率为 :

若 V IVCO = VSS ,则 fM IN = 1 /R2 ( C1 + 32PF) 若 V IVCO = VDD ,则 fMAX = 1 /R1 ( C1 + 32PF) + 1 /R2 ( C1

锁相环与其它有相同功能的线路相比有可实现理想 的频率控制 、良好的窄带跟踪特性 、良好的调制跟踪特性 和低门限特性等优点 。

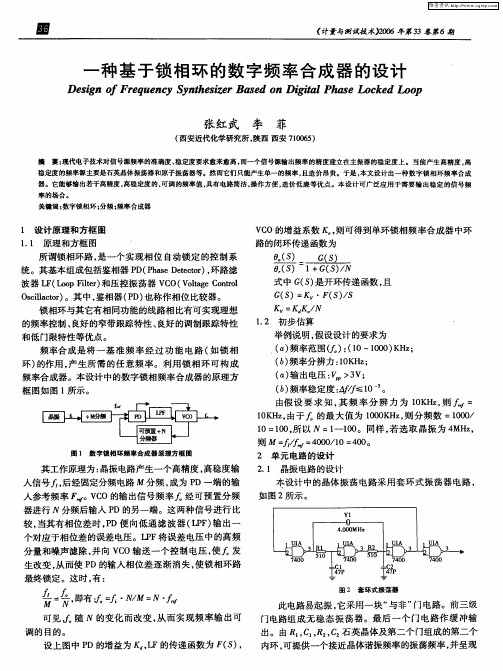

频率合成是将一基准频率经过功能电路 (如锁相 环 )的作用 ,产生所需的任意频率 。利用锁相环可构成 频率合成器 。本设计中的数字锁相频率合成器的原理方 框图如图 1所示 。

图 1 数字锁相环频率合成器原理方框图

其工作原理为 :晶振电路产生一个高精度 ,高稳度输 入信号 fI ,后经固定分频电路 M 分频 ,成为 PD 一端的输 入参考频率 Fref 。VCO 的输出信号频率 fo 经可预置分频 器进行 N 分频后输入 PD 的另一端 。这两种信号进行比 较 ,当其有相位差时 , PD 便向低通滤波器 (LPF)输出一 个对应于相位差的误差电压 。LPF将误差电压中的高频 分量和噪声滤除 ,并向 VCO 输送一个控制电压 ,使 fo 发 生改变 ,从而使 PD 的输入相位差逐渐消失 ,使锁相环路 最终锁定 。这时 ,有 :

PD 和 VCO 两 部 分 可 用 单 片 集 成 数 字 锁 相 环 CD4046来完成 。这种锁相环采用 CMOS电路工艺 ,由于 其工作稳定可靠 ,电路简单 ,功耗极低和低成本等优点 , 在低 、中频段上较之其它方案具有更多的优越性 。由于 输出信号是方波信号 ,其幅度大 ,锁定范围和捕捉范围均 较理想 ,适合不同的应用领域 。CD4046的框图及功能引 脚如图 5所示 。

( a)输出电压 : Vpp > 3V; ( b)频率稳定度 :Δf / f≤10 - 5 。

由假设 要 求 知 , 其 频 率 分 辨 力 为 10KHz, 则 fref = 10KHz,由于 fo 的最大值为 1000KHz,则分频数 = 1000 / 10 = 100,所以 N = 1—100。同样 ,若选取晶振为 4MHz,

1 设计原理和方框图 111 原理和方框图

所谓锁相环路 ,是一个实现相位自动锁定的控制系 统 。其基本组成包括鉴相器 PD ( Phase Detector) ,环路滤 波器 LF (Loop Filter)和压控振荡器 VCO (Voltage Control O scillactor) 。其中 ,鉴相器 ( PD )也称作相位比较器 。

+ 32PF)

通常 , R1 , R2 和 C1 取以下范围为宜 : 10KΩ ≤R1 , R2 ≤1MΩ;

VDD = 5V 时 , C1 ≥100PF; VDD = 10V 时 , C1 ≥50PF。

根据假设要求 ,可取 R1 , R2 和 C1 的值分别为 : R1 = 10KΩ , R2 在 不同 频段 分 别 取 10KΩ , 100KΩ , 1MΩ 三个值 , C1 = 100PF。 215 环路滤波器的设计

环路锁定时 , CD4046的相位脉冲输出端 (1脚 )输出一个 稳定的高电平信号 。同时 ,本设计的输出信号的电压值 VPP大于 3V ,符合要求 。

在调试过程中可发现 , CD4046 的锁定范围是随着 R2 阻值的改变而变化的 。从小到大 ,根据实际不同输出 频率的要求 , R2 值依次取 1MΩ , 100KΩ 和 10KΩ。 4 结束语

VCO 是电压 —频率转换器 ,其瞬时频率 WV ( t)是控 制电压 Vc ( t) 的函数 。在环路锁定点附近可近似为直

37

线 ,且有控制方程 : W v ( t) =W o + KoVc ( t) ,式中 Ko = tgα 是控制特性的斜率 ,它表示单位控制电压可使 VCO 角频 率变化的大小 ,又称为 VCO 的控制灵敏度或增益 ,单位 为 [ rad / s·v ]。

严宏剑 :传感器技术在生产实践中的研究与应用

R1 , C1 , R2 , C2 的取值只要使不接晶体时振荡频率约 为晶体频率的 70% ~90%即可 。该电路可选 1MHz至 20MHz的晶体 。根据假设要求 ,选晶振为 4MHz。 212 固定式分频器的设计

固定式分频器可 采用 双 BCD 码 同步加 法计 数器 4518来实现 20 ×20 = 400的分频 。其电路模块图如图 3 所示 。

其次 ,是应变片和粘接胶 。影响应变片稳定性的是 箔材本身 ,制造应变片的电阻合金种类很多 ,其中以康铜 合金使用最广 ,它有较好的稳定性 ,高的疲劳寿命及小的 电阻温度系数 ,是理想的丝栅制造材料 。此外 ,制造应变 片过程中应消除不良影响而造成的不稳定性 。如 :丝栅 与基底胶的粘接强度 ,应变片与弹性体间的粘帖强度 ,基 底胶内应力的释放等等 ,都是不稳定因素 。另外 ,应变片 的粘帖 ,也是非常关键的要素之一 ,这一工作的好坏 ,直 接影响胶的粘接质量 ,乃至测量精度 ,如果帖片不严格 , 技术不熟练 ,即使使用最好的应变片也无济于事 。

目前传感器属高新技术的瓶颈工业 ,它的地位非常 重要 ,由于历史的原因 ,我国的传感器技术比较落后 。改

革开放以后 ,民营企业和股份制公司已经蓬勃发展起来 , 传感器的发明创造不断涌现 ,有望能迅速赶上世界先进 水平 。但是目前这些企业多属技术人员经营 ,力量单薄 , 引进资金缺乏渠道 ,难以参与国内外的激烈竞争 。要改 变这种局面 ,可采取以下多种办法 。其一 ,走大联合的道 路 ,不仅要将分散孤立的传感器企业横向联合起来 ,而且 还要把同一类产品从科研 、生产 、流通到使用的有关单位 和个人纵向联合起来 ,发挥优势互补 、利益与共的作用 。 其二 ,发挥学会 、协会的重要作用 ,寻求发展机会 ,这也是 国外发达国家的企业普遍采用的方法 ,协会侧重从事业 内企业 、组织的协调工作 ,学会要多搞学术 、技术交流活 动 ,这样群策群力 ,共同发展 。其三 ,宣传推广与学术活 动结合起来 ,无论是业内企业还是学会 、协会 ,应该在努 力搞好本身的生产与工作的同时 ,注重产品的外在包装 与宣传 ,把生产 、学术研究与推广应用结合起来 ,把参加 研讨会和展览会结合起来 ,把新闻媒体和展览公司结合 起来 ,必将得到较好的效果 。这也是我国传感器技术发 展所能够走向顶峰的必经之路 。

工作速度 。本设计中取 R1 = 470KΩ , R2 = 47KΩ , C1 =