模拟IC基础学习(二)-模拟IC电路设计问题

ic_设计_智力测试题(3篇)

第1篇引言:集成电路(IC)设计是一项复杂而精细的工作,要求设计者具备深厚的理论知识、丰富的实践经验以及出色的逻辑思维能力。

为了帮助您了解自己在IC设计领域的智力水平,我们特别设计了以下智力测试题。

请您认真作答,完成后可对自己的设计能力有一个初步的认识。

第一部分:基础知识1. 选择题- 下列哪个选项不是IC设计中所使用的制造工艺?A. CMOSB. TTLC. ECLD. LED2. 填空题- 在IC设计中,版图(Layout)是电路的__________,而原理图(Schematic)则是电路的__________。

3. 简答题- 简述CMOS工艺的基本原理。

第二部分:逻辑分析与设计1. 选择题- 下列哪个电路可以实现逻辑与功能?A. OR门B. AND门C. NOT门D. XOR门- 在组合逻辑电路中,如果某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称为__________。

3. 简答题- 解释竞争与冒险现象,并说明如何消除它们。

第三部分:版图设计1. 选择题- 下列哪个工具常用于IC版图设计?A. Altium DesignerB. CadenceC. OrCADD. Pro/ENGINEER2. 填空题- 在版图设计中,为了防止寄生效应,通常需要将__________与__________保持一定的距离。

3. 简答题- 简述版图设计中的规则检查(DRC)和设计规则约束(DRC)。

第四部分:IC制造1. 选择题- 下列哪个步骤是IC制造过程中的关键步骤?A. 光刻B. 化学气相沉积C. 离子注入D. 刻蚀- 在IC制造中,__________是将电路图形转移到硅片上的关键步骤。

3. 简答题- 简述IC制造过程中可能遇到的问题及解决方法。

第五部分:模拟IC设计1. 选择题- 下列哪个电路属于模拟电路?A. 741运算放大器B. 555定时器C. 74LS00D. 74HC002. 填空题- 在模拟IC设计中,__________是放大信号的关键元件。

模拟IC设计知识分享(1)

模拟IC设计知识分享(1)最近刚好要考AAIC了,于是就想着怎么把考试的知识点总结起来分成章节。

本来想画成思维导图,但一是很多公式很多图,二是知识点间相互都有联系,也着实不太好具象化。

模拟电路就是折中的艺术,硬要画成放射状也是有点难为我了。

不如就写成文章,不仅能帮助我learning by teaching,说不定也能造福点后人。

MOS管作为模拟IC的基础组成部分,掌握MOS的各项特性是重中之重。

但由于MOS管其实是一个特性非常复杂,且无法用一个简单模型做出概括的非线性器件,我们也有必要对其进行一定的简化。

我们首先介绍MOS的基本结构和简化模型。

一、MOS管三维结构MOS管符号[1]典型的NMOS拥有四个端口,分别是栅极(gate),源极(source),漏极(drain)和衬底(body/bulk)。

MOS管是一种将电压转化为电流的器件,可以简单理解为一个压控电流源,以栅极和源极间的电压控制流过漏极和源极的电流。

根据各个端口间电压的不同,MOS管还可以分为三个工作区域,分别为截止区(cut-off region),线性区/三极管区(triode region)和饱和区(saturation region)。

我们可能已经了解MOS管可以用作开关,也可以对信号进行放大。

当MOS管用作开关时,它就工作在线性区;而当用作放大器时,它需要工作在饱和区。

在进一步分析每个工作区域的特性和条件之前,我们首先把这个抽象模型和实际世界的MOS管这一半导体器件对应起来。

NMOS管三维结构[2]上图所示是一个NMOS的结构图。

器件制作在p型衬底(substrate)上,两个n离子掺杂区形成源极和漏极,并通过金属引出。

早期MOS管的栅极由金属层制成(如图,这也是MOSFET名字中第一个M-Metal的由来),但现今大部分的MOS 管采用多晶硅(poly)来制作栅极,而名字却没有随之修改。

当然多晶硅和金属制作栅极各有利弊,还请详见半导体物理一书。

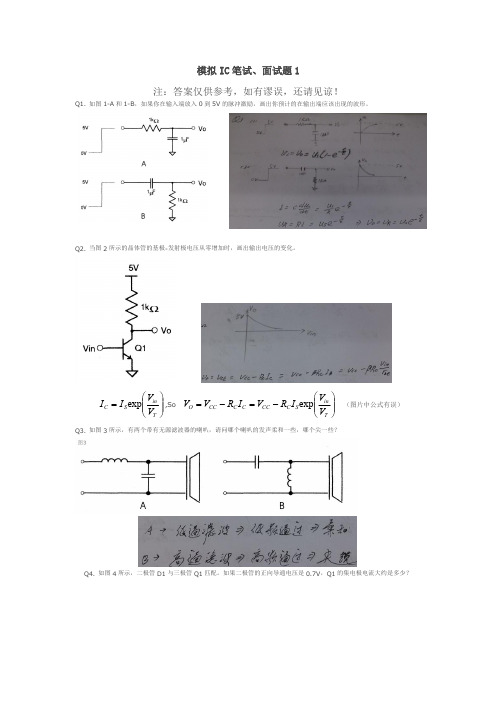

2套模拟IC岗位笔试、面试题及解答

Q16. 一个 300K 温度下的 1K 电阻的热噪声电压是多少?

Q17. 一个晶体管在环境温度为 25C 的环境下消耗 25W 的功率。已知这个晶体管的热电阻是 3C/W,它的最大可工作电压为 150C,那么散热片的热电阻应该为多大?

RSA≤[(TJ-TA)/over{PD}]-(RJC+RCS)=(150℃-25℃)/25W-3℃/W=2℃/W

Q18. 用反相器、与非门和或非门电路画出异或门等效电路。

Q19. 在如下的工作中,你从事何种工作? a. C++编程人员; b. Canary 岛的滑板俱乐部教员; c. 滚石乐队巡演的保安; d. 模拟设计工程师。

模拟 IC 笔试、面试题 2

三极管, 放大器, 负反馈, 灵敏度, 微电子

1、基尔霍夫定理的内容是什么?(仕兰微电子) 基尔霍夫第一定理:在集总电路中,任何时刻,对电路中的任一节点,流进某一节点的电流之和恒等于流出该节点的电流之和。 基尔霍夫第二定理:在集总电路中,任何时刻,对电路中的任一闭环回路,沿回路绕行方向上各段电压代数和恒等于零。 (集总电路:电路所涉及电路元件的电磁过程都集中在元件内部进行。用集总电路近似实际电路是有条件的,这个条件是实际电路 的尺寸要远小于电路工作时的电磁波长。对于集总参数电路,由基尔霍夫定律唯一地确定了结构约束。) 2、平板电容公式 (C=εS/4πkd)。(未知) 3、最基本的如三极管曲线特性。(未知) 4、描述反馈电路的概念,列举他们的应用。(仕兰微电子) 在电路中,将输出量的一部分或全部通过一定的电路形式作用到输入回路,来影响其输入量的措施称为反馈。 负反馈能起到稳定电路的作用,比如共射放大电路中射级电阻 Re 能抵消由于温度升高引起的 Ic 上升。 正反馈可用于振荡器电路,将电路的自激振荡维持下去,最终形成稳定的振荡信号。 5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈的优点(降低放大器的增益灵敏度,改 变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知) 优点: (1)牺牲放大倍数而达到稳定放大倍数的效果,Af 减小到 A 的(1+AF)分之一,而增益稳定性提高到 A 的 (1+AF)倍。 (2)改变输入、输出电阻:串联负反馈 增大输入电阻(1+AF)倍、并联反馈减小输入电阻(1+AF)分之一 电压负反馈(稳定输出电压) 减小输出电阻 (1+AF)分之一 电流负反馈(稳定输出电流) 增大输出电阻 (1+AF)倍 (3)展宽频带 (1+AF)倍 (4)改善放大器的非线性失真(只能抑制电路内部的非线性失真;输出量在闭环前、后的基波不变时,非线性失真(输出的 谐波部分)才能减小到基本放大电路的(1+AF)分之一) 6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子) 补偿: 引入负反馈,增加相位裕度(至少 45 度),使电路稳定性提高。 补偿方式: (1)密勒补偿 使极点 P1 更加靠近原点,极点 P2 更加远离原点,使相位在第二个极点处的-90 度变化延后了, 而 0dB 点的位置没变,从而相位裕度增加了。 (2)前馈补偿 抵消前馈路径(比如加一个单位缓冲器),消除右半平面零点。(相位曲线每经过一个 RHP 的 变化和经过一个极点的变化一样。) (通过加入调零电阻,调节 Rz 使右半平面零点远在带宽之外,也可以控制 RHP 的作用) 7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。(未知) 稳定:环路增益下降到 1 时,反馈信号的相位变化小于 180 度。改变方法:补偿-密勒补偿(控制极点位置)、前馈补偿(控 制右半平面零点位置) 8、给出一个差分运放,如何相位补偿,并画补偿后的波特图。(凹凸) 可参考两级运放的补偿及补偿前后波特图的变化(重点是极点位置的改变) 9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。(未 知) 差分放大器:抑制共模干扰 10、给出一差分电路,告诉其输出电压 Y+和 Y-,求共模分量和差模分量。(未知)

模拟IC设计流程总结PPT课件

PM Group 陈志军

1

微固学院 功率集成技术实验室

.

主要内容

31

绪论

2

前端设计

3

后端设计

4

后端设计工具

35

结论

2

.

模拟IC与数字IC的比较

3

.

模拟IC设计的特点 ▪ Geometry is an important part of the design ▪ Usually implemented in a mixed analog-digital circuit ▪ Analog is 20% and digital 80% of the chip area ▪ Analog requires 80% of the design time

9 CMOS Mixed-Signal Circuit Design

10 Analog MOS Integrated Circuits II 11 Fundamentals of Power Electronics 12 Switching Power Supply Design 13 Power Electronics :Circuits,Devices and Applications 14 Modern DC- to-DC Switchmode Power Converter Circu8its

养成边标线边纪录的习惯。

▪ 提取版图是一个需要细心和耐心的过程。版图提取错误,会给

随后的电路分析造成很大的麻烦和重复劳动,浪费时间,延缓 进度。

▪ 按照版图的布局分块提取版图,注明晶体管的类型,遵循版图

原状,不要合并晶体管。

▪ 提取版图时应先确定器件的类型,再从POLY层画出器件,然后

模拟电子电路基础

(n+1)IB

n 个输出电流时的

相对误差= (n+1) /β

休息1 休息2

返回

2.精密镜像电流源

(1) 电路结构:

EC

用 T3 代替了基本电流源电路中的短路线 IR

I B3

IC2

(2) 电路分析: 同理有:UBE1=UBE2=UBE

IC1

IB1 IE3 IB2

∴

IC1=IC2=IS

exp

U BE UT

(2)电路分析:

因为 UBE1= UBE2= UBE ,IB1=IB2=IB

所以

IC1=IC2=ISexp

U BE UT

又因为

IR

IC1

2IB

IC1

1

2

IC1

2

IC1 IC2

IR

2

IR

2

当β>>1 时: IC2 IR

而 IR

EC

U BE R

EC R

EC

IR

IC2

2IB

IB1

IB2

IC1

+

UBE —

返回 休息1 休息2

1 基本镜像电流源:

EC

(3)讨论

IR

IC2

(ⅰ4):电I流C2源 I的R 输出电镜阻像关系

2IB

ⅱrⅲ0:=I:rRce2=另EUIRCC外 A2 ,参输考I出电R-电流IC与阻2=晶等2体于I管BT参2 管数的无存输关在出,稳电误定阻差, IC1

IB1

IB2

+

UBE

§ 3.1 半导体集成电路概述

第一块集成电路出现于1958年。在使用电子电路的绝大 多数场合,IC已经基本上取代了分立元件电路。

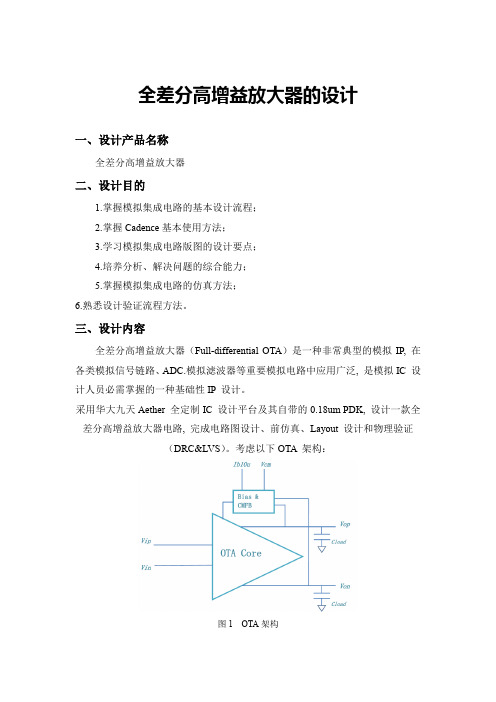

模拟集成电路设计——两级全差分高增益放大器设计_2

全差分高增益放大器的设计一、设计产品名称全差分高增益放大器二、设计目的1.掌握模拟集成电路的基本设计流程;2.掌握Cadence基本使用方法;3.学习模拟集成电路版图的设计要点;4.培养分析、解决问题的综合能力;5.掌握模拟集成电路的仿真方法;6.熟悉设计验证流程方法。

三、设计内容全差分高增益放大器(Full-differential OTA)是一种非常典型的模拟IP, 在各类模拟信号链路、ADC.模拟滤波器等重要模拟电路中应用广泛, 是模拟IC 设计人员必需掌握的一种基础性IP 设计。

采用华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 设计一款全差分高增益放大器电路, 完成电路图设计、前仿真、Layout 设计和物理验证(DRC&LVS)。

考虑以下OTA 架构:图1 OTA架构四、电路设计思路模拟集成电路的设计分为前端与后端, 设计流程可以分为明确性能要求、选择电路结构、计算器件参数、原理图绘制、前仿真、版图绘制、DRC设计规则检查、LVS版图与电路图一致性检查、寄生参数提取及后仿真、流片测试。

本次实验使用基于华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 实现模拟集成电路全差分高增益放大器的全流程设计与仿真。

(1)性能指标:需要验证三种PVT Corner:a) 电源电压1.8V, 温度27℃, corner 为TT;b) 电源电压1.6V, 温度80℃, corner 为SS;c) 电源电压2.0V, 温度-40℃, corner 为FF;要求各Corner 下开环技术指标(含Cload=10fF):①放大器开环DC 增益Av0≥90dB;②0dB 带宽BW0≥500MHz;③相位裕度Phase Margin≥50°。

④DC 抑制比PSRR-0≥60dB, (3*2=6 分)⑤10MHz 时抑制比PSRR-10M≥45dB。

数字ic设计流程与模拟IC

数字ic设计流程与模拟IC1. 首先是使用HDL语言进行电路描述,写出可综合的代码。

然后用仿真工具作前仿真,对理想状况下的功能进行验证。

这一步可以使用Vhdl或Verilog作为工作语言,EDA工具方面就我所知可以用Synopsys的VSS(for Vhdl)、VCS(for Verilog)Cadence的工具也就是著名的Verilog-XL和NC Verilog2.前仿真通过以后,可以把代码拿去综合,把语言描述转化成电路网表,并进行逻辑和时序电路的优化。

在这一步通过综合器可以引入门延时,关键要看使用了什么工艺的库这一步的输出文件可以有多种格式,常用的有EDIF格式。

综合工具Synopsys的Design Compiler,Cadence的Ambit3,综合后的输出文件,可以拿去做layout,将电路fit到可编程的片子里或者布到硅片上这要看你是做单元库的还是全定制的。

全定制的话,专门有版图工程师帮你画版图,Cadence的工具是layout editor单元库的话,下面一步就是自动布局布线,auto place & route,简称apr cadence的工具是Silicon Ensembler,Avanti的是Apollo layout出来以后就要进行extract,只知道用Avanti的Star_rcxt,然后做后仿真,如果后仿真不通过的话,只能iteration,就是回过头去改。

4,接下来就是做DRC,ERC,LVS了,如果没有什么问题的话,就tape out GDSII格式的文件,送制版厂做掩膜板,制作完毕上流水线流片,然后就看是不是work 了做DRC,ERC,LVSAvanti的是Hercules,Venus,其它公司的你们补充好了btw:后仿真之前的输出文件忘记说了,应该是带有完整的延时信息的设计文件如:*.VHO,*.sdfRTL->SIM->DC->SIM-->PT-->DC---ASTRO--->PT----DRC,LVS--->TAPE OUT1。

IC笔试题大全(部分含答案)

EE笔试/面试题目集合分类--IC设计基础1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

(仕兰微面试题目)2、FPGA和ASIC的概念,他们的区别。

(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)2、平板电容公式(C=εS/4πkd)。

(未知)3、最基本的如三极管曲线特性。

(未知)4、描述反馈电路的概念,列举他们的应用。

(仕兰微电子)5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。

(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。

(未知)11、画差放的两个输入管。

(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

(仕兰微电子)13、用运算放大器组成一个10倍的放大器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

模拟IC基础学习(二):模拟IC电路设计问题

很多时候,我们在初期设计或者优化电路时,满脑子想的都是性能如何能一点一点提高,而忽略了所谓的模拟设计的一些基本考虑;待到版图设计时已经晚矣。

那个时候再去修改基本设计无疑是不值得,要么耗费精力,要们前功尽弃。

作为教训,如果我们能够在设计初期,就带着这些基本考虑,那么在选择基本器件的时候,就会有的放矢,知道一个大概的合理的选取范围,有利于版图设计和优化。

1. 晶体管最小沟长为工艺最小特征尺寸的4-5倍,用来减小沟长调制效应。

2.目前模拟设计仍然是使晶体管工作在饱和区,故应使Vgs 大于Vt约30%。

3. 应把大管分成小晶体管,使其宽/长特征尺寸

第1页共1页。