用层次原理图设计四位全加器 教案

全加器四位串行加法器.最全优质PPT

• signal c: std_logic_vector(0 to 4);

• begin

• g0:f_adder

• port map(x(0),y(0),c(0),s(0),c(1));

• x<='0'&a(3 dowgn1to:0f)_; adder

该方法常用于系统数学模型的仿真或是系统工作原理的仿真。

a,b : •in std_logicp_voecrtotr(3mdoawnpto(0x);(1),y(1),c(1),s(1),c(2));

std_logic_1164.

• g2:f_adder 四位串行加法器(逻辑图)

std_logic_unsigned.

e数n据d e流•n式tity电f_路a设dd计per方;o法rt:m通过a对p数(据x流(2在)设,y计(中2的),具c体(2行)为,s的(描2述),来c建(3模)。); • g3:f_adder x<='0'&a(3 downto 0);

• architecture bhv of f_adder is

• begin

• g0:s<=x xor y xor cin;

• g1:cout<=(x and y)or(x and cin)or(y and cin);

• end architecture bhv;

四位串行加法器(逻辑图)

四位串行加法器(结构体式)

• use ieee.std_logic_unsigned.all;

• entity bit_f_adder is

• port(cin: in std_logic;

•

a,b : in std_logic_vector(3 downto 0);

实验一 4位全加器的设计(1)

实验一4位全加器的设计一、实验目的:1 熟悉QuartusⅡ与ModelSim的使用;2 学会使用文本输入方式和原理图输入方式进行工程设计;3 分别使用行为和结构化描述方法进行四位全加器的设计;4 理解RTL视图和Technology Map视图的区别;5 掌握简单的testbench文件的编写。

二、实验原理:一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的进位输入信号cin相接。

三、实验内容:1.QuartusII软件的熟悉熟悉QuartusⅡ环境下原理图的设计方法和流程,可参考课本第4章的内容,重点掌握层次化的设计方法。

2.设计1位全加器原理图设计的原理图如下所示:VHDL源程序如下(行为描述):library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity f_add_bev is(A : in std_logic;B : in std_logic;CIN : in std_logic;S : out std_logic;CO : out std_logic);end entity;architecture bev of f_add_bev isbegin(CO,S)<=('0',A)+('0',B)+('0',CIN);end bev;VHDL源程序如下(行为描述)的RTL与technology map视图VHDL源程序如下(数据流描述):library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity f_add_fl is(A : in std_logic;B : in std_logic;CIN : in std_logic;S : OUT std_logic;CO : out std_logic);end entity;architecture fl of f_add_fl isbeginS<=A XOR B XOR CIN;CO<=((A XOR B)AND CIN)OR(A AND B);end fl;VHDL源程序如下(数据流描述)的RTL与technology map视图:VHDL源程序如下(结构化描述):library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity f_add_con isport(A : in std_logic;B : in std_logic;CIN : in std_logic;S : OUT std_logic;CO : out std_logic );end entity;architecture con of f_add_con is COMPONENT hadd_vhdPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;co : OUT STD_LOGIC;s : OUT STD_LOGIC );END COMPONENT;SIGNAL S1:STD_LOGIC;SIGNAL CO1:STD_LOGIC;SIGNAL CO2:STD_LOGIC;beginh_add1 : hadd_vhdport map(a => a,B => B,S => S1,CO => CO1);h_add2 : hadd_vhdport map(a => S1,B => CIN,S => S,CO => CO2);CO<=CO1 OR CO2;end con;VHDL源程序如下(结构化描述)的RTL与technology map视图:Testbench文件源程序如下:LIBRARY cycloneiii ;LIBRARY ieee ;USE cycloneiii.cycloneiii_components.all ;USE ieee.std_logic_1164.all ;ENTITY f_add_fl_tb ISEND ;ARCHITECTURE f_add_fl_tb_arch OF f_add_fl_tb ISSIGNAL A : STD_LOGIC :='0';SIGNAL CO : STD_LOGIC ;SIGNAL CIN : STD_LOGIC :='0'; SIGNAL B : STD_LOGIC :='0'; SIGNAL S : STD_LOGIC ;COMPONENT f_add_flPORT (A : in STD_LOGIC ;CO : buffer STD_LOGIC ;CIN : in STD_LOGIC ;B : in STD_LOGIC ;S : buffer STD_LOGIC );END COMPONENT ;BEGINDUT : f_add_flPORT MAP (A => A ,CO => CO ,CIN => CIN ,B => B ,S => S ) ;A<=NOT A AFTER 0.25US;B<=NOT B AFTER 0.5US;CIN<=NOT CIN AFTER 1US;END ;功能仿真波形如下:时序仿真波形如下:3.利用层次化原理图方法设计4位全加器(1)生成新的空白原理图,作为4位全加器设计输入(2)利用已经生成的1位全加器作为电路单元,设计4位全加器。

组合逻辑课程设计4位二进制全加器全减器原创

关键字 74LS283 全加器、四位二进制、迭代电路、并行进位、串行进位、VHDL

摘要

加法器是数字系统中产生数的和的装置。加数和被加数为输入,和数与进 位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进

...

.

..

..

位为输出则为全加器。例如:为了节省资源,减法器和硬件乘法器都可以用加法 器来构成。但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设 计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成 主要有两种:并行进位和串行进位。并行进位加法器设有并行进位产生逻辑,运 行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多 位加法器。加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令 调用。此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二 进制作运算。

1 0 0100 11011000

1 0 0101 00011010

1 0 0001 10011100

1 0 0001 10111110

1 0 1010 01000111

1 0 1010 01101001

1 0 0010 01000011

1 0 0010 01100101

... ... ... ... ... ... ... ... ... ... ... ... ... ...

课题 四位全加器

课题 四位全加器

一、课题目的

1.用组合电路设计4位全加器。

2.了解VHDL 语言的行为描述的优点。

3.初步掌握系统内部STD_LOGIC_UNSIGNED 包的调用。

二、课题原理

4位全加器可看作4个1位全加器串行构成,具体连接方法如下图所示: 由1位全加器构成4位全加器连接示意图

采用VHDL 语言设计时调用其附带的程序包,其系统内部会自行生成此结构。

三 、课题内容

1. 用VHDL 语言设计4位全加器。

2. 锁定引脚,并下载验证之。

3. 不调用包,用户自行按示意图进行设计,体会调用系统包的便利性。

四、设计提示

1.调用STD_LOGIC_UNSIGNED 包,可以使用户在更高层次上进行设计。

五、课题报告要求

1. 叙述所设计的4位全加器工作原理。

2. 写出1位全加器的VHDL 语言源程序。

3、写出心得体会。

用原理图输入法设计4位全加器

实验一------用原理图输入法设计4位全加器

1.实验目的

熟悉利用MAX+PLUSⅡ的原理图输入法来设计简单组合逻辑电路,学会层次化设计方法,并通过一个4位全加器的设计,学会利用EDA软件进行电子电路设计的详细流程。

2.实验原理。

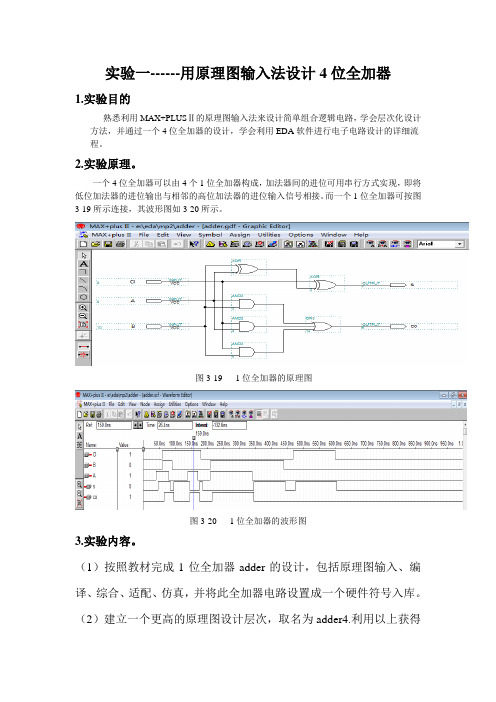

一个4位全加器可以由4个1位全加器构成,加法器间的进位可用串行方式实现,即将低位加法器的进位输出与相邻的高位加法器的进位输入信号相接。

而一个1位全加器可按图3-19所示连接,其波形图如3-20所示。

图3-19 1位全加器的原理图

图3-20 1位全加器的波形图

3.实验内容。

(1)按照教材完成1位全加器adder的设计,包括原理图输入、编译、综合、适配、仿真,并将此全加器电路设置成一个硬件符号入库。

(2)建立一个更高的原理图设计层次,取名为adder4.利用以上获得

的1位全加器构成4位全加器,电路原理图如图3-21所示。

图3-21 4位全加器电路原理图

4.实验结果。

首先按照原理图设计1位全加器,之后通过四个1位全加器正确连接后则设计出4位全加器,其波形图如上图所示.。

eda课程设计论文4位全加器

eda课程设计论文4位全加器一、教学目标本课程的目标是让学生理解并掌握全加器的工作原理和设计方法,能够运用数字逻辑设计出功能完整的全加器。

知识目标:使学生了解全加器的功能和作用,理解其内部电路的工作原理,掌握全加器的真值表和布尔表达式。

技能目标:培养学生运用数字逻辑设计简单电路的能力,能够独立完成全加器的设计和仿真。

情感态度价值观目标:培养学生对电子技术的兴趣,提高学生解决问题的能力,培养学生的创新精神和团队协作精神。

二、教学内容本课程的教学内容主要包括全加器的功能和工作原理、全加器的真值表和布尔表达式、全加器的设计和仿真。

首先,讲解全加器的功能和作用,通过具体的实例让学生了解全加器在计算机中的重要性。

然后,讲解全加器的内部电路工作原理,使学生理解全加器是如何实现加法的。

接下来,介绍全加器的真值表和布尔表达式,让学生掌握全加器的工作原理。

最后,讲解全加器的设计和仿真方法,培养学生运用数字逻辑设计电路的能力。

三、教学方法为了提高学生的学习兴趣和主动性,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法。

首先,通过讲授法向学生传授全加器的理论知识,使学生了解全加器的基本概念和工作原理。

然后,通过讨论法引导学生进行思考和讨论,提高学生的理解能力。

接下来,通过案例分析法分析实际案例,使学生了解全加器在计算机中的应用。

最后,通过实验法让学生动手设计和仿真全加器,提高学生的实践能力。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将选择和准备适当的教学资源,包括教材、参考书、多媒体资料和实验设备。

教材:选用《数字逻辑设计》作为主教材,系统地介绍全加器的理论知识。

参考书:推荐《计算机组成原理》等参考书,供学生深入学习和参考。

多媒体资料:制作全加器的原理讲解和设计过程的视频,通过动画和图像等形式直观地展示全加器的工作原理。

实验设备:准备数字逻辑设计实验室,提供全加器的设计和仿真实验所需设备。

eda4位加法课程设计

eda4位加法课程设计一、课程目标知识目标:1. 学生能理解并掌握4位加法的基本概念和原理;2. 学生能够掌握并运用EDA工具进行4位加法电路的设计与实现;3. 学生能够理解并描述4位加法器的工作原理及其在各种电子设备中的应用。

技能目标:1. 学生能够运用所学知识,独立完成4位加法电路的设计和搭建;2. 学生能够运用EDA工具进行电路仿真,分析并解决4位加法电路中可能出现的实际问题;3. 学生通过实践操作,提高逻辑思维能力和问题解决能力。

情感态度价值观目标:1. 学生在学习过程中,培养对电子技术和数字电路的兴趣和热情;2. 学生通过团队协作,培养合作精神和沟通能力;3. 学生在实践过程中,认识到科技对社会发展的作用,增强创新意识和责任感。

课程性质:本课程为电子设计自动化(EDA)相关课程,旨在让学生掌握4位加法电路的设计与实现,提高学生的实践操作能力和逻辑思维能力。

学生特点:学生处于初中阶段,对电子技术有一定的好奇心,但可能对具体操作和理论知识掌握不足。

教学要求:结合学生特点,注重理论与实践相结合,通过实例分析和动手操作,使学生能够扎实掌握4位加法电路的相关知识。

同时,关注学生的情感态度价值观培养,提高学生的综合素质。

在教学过程中,将课程目标分解为具体的学习成果,便于教学设计和评估。

二、教学内容1. 4位加法电路基本原理:包括全加器、半加器的概念,4位加法器的工作原理及其在不同进位模式下的特点。

- 教材章节:第三章第三节《加法器的设计与应用》2. EDA工具的使用:介绍并练习使用EDA工具进行4位加法电路的设计、仿真和验证。

- 教材章节:第五章《电子设计自动化工具》3. 4位加法电路的设计与实现:- 教学内容:指导学生利用EDA工具进行4位加法电路的设计,包括原理图绘制、电路仿真和波形分析。

- 教材章节:第四章《数字电路设计与实现》4. 实践操作与问题分析:- 教学内容:组织学生进行4位加法电路的搭建,分析并解决实际操作中遇到的问题。

4位全加器verilog课程设计

4位全加器verilog课程设计一、课程目标知识目标:1. 理解4位全加器的原理和功能,掌握其Verilog硬件描述语言实现方法。

2. 学习并掌握数字电路中加法器的基本结构和工作原理。

3. 掌握Verilog模块化编程,能够实现并测试4位全加器的基本功能。

技能目标:1. 能够运用Verilog语言编写4位全加器的代码,并进行功能仿真。

2. 学会使用硬件描述语言进行数字电路的设计,提高实际问题解决能力。

3. 能够对4位全加器进行调试和优化,提升编程实践技能。

情感态度价值观目标:1. 培养学生的团队合作意识,提高学生在项目实践中的沟通与协作能力。

2. 增强学生对数字电路设计领域的兴趣,激发学生的创新精神。

3. 引导学生树立正确的价值观,认识到科技发展对社会进步的重要性。

课程性质:本课程为电子信息工程及相关专业高年级的数字电路设计课程,旨在通过4位全加器的Verilog实现,让学生掌握数字电路设计的基本方法和实践技能。

学生特点:学生已具备一定的数字电路基础和Verilog编程知识,具备分析问题和解决问题的能力。

教学要求:注重理论与实践相结合,鼓励学生积极参与课堂讨论,培养学生的动手能力和实际操作技能。

通过课程学习,使学生在知识、技能和情感态度价值观方面均取得明显进步。

二、教学内容本课程教学内容主要包括以下几部分:1. 数字加法器原理回顾:介绍加法器的基本原理,重点讲解4位全加器的工作流程和关键特性。

- 教材章节:数字电路基础,第3章第2节。

2. Verilog硬件描述语言基础:复习Verilog的基本语法,强调模块化编程方法。

- 教材章节:硬件描述语言Verilog,第4章。

3. 4位全加器的Verilog设计:- 设计原理:讲解4位全加器的设计思路和实现方法。

- 代码编写:引导学生编写4位全加器的Verilog代码,并进行模块化设计。

- 教材章节:数字电路设计,第5章第3节。

4. 功能仿真与调试:- 介绍仿真工具和仿真方法,指导学生进行4位全加器的功能仿真。

四位全加器版图课程设计

四位全加器版图课程设计一、课程目标知识目标:1. 让学生理解四位全加器的原理,掌握其功能、结构和操作方法。

2. 使学生掌握数字电路中加法器的基本概念,了解四位全加器在数字系统中的应用。

3. 帮助学生掌握二进制数加法运算的规则,并能运用四位全加器进行简单的二进制加法计算。

技能目标:1. 培养学生运用所学知识,分析并设计简单的四位全加器电路。

2. 提高学生动手实践能力,能够正确搭建四位全加器电路,并进行调试。

3. 培养学生运用四位全加器解决实际问题的能力。

情感态度价值观目标:1. 培养学生对数字电路的兴趣,激发他们学习电子技术的热情。

2. 培养学生严谨的科学态度,注重实验数据的准确性和可靠性。

3. 引导学生认识到数字电路在现代科技中的重要作用,增强他们的国家荣誉感和责任感。

课程性质分析:本课程为电子技术基础课程,旨在让学生掌握四位全加器的基本原理和实际应用,培养他们的实践操作能力。

学生特点分析:学生为初中年级学生,对电子技术有一定的基础,具备基本的电路知识和动手能力,但需要进一步引导和培养。

教学要求:1. 注重理论与实践相结合,让学生在实际操作中掌握四位全加器的原理和应用。

2. 采用启发式教学方法,引导学生主动思考、探索,培养他们的创新意识。

3. 注重个体差异,因材施教,使每位学生都能在课程中取得实质性的进步。

二、教学内容1. 四位全加器的基本概念与原理:- 加法器的作用与分类- 四位全加器的结构及工作原理- 二进制数加法运算规则2. 四位全加器的电路设计与分析:- 电路元件的选用与连接- 四位全加器的逻辑表达式及简化- 电路图的绘制与解读3. 四位全加器的实际应用:- 在数字系统中的应用场景- 与其他数字电路的组合应用- 实际电路搭建与调试4. 教学内容的安排与进度:- 第一课时:介绍加法器的基本概念,引导学生了解四位全加器的原理和结构- 第二课时:讲解二进制数加法运算规则,分析四位全加器的电路设计方法- 第三课时:指导学生动手搭建四位全加器电路,进行调试与优化- 第四课时:探讨四位全加器在实际应用中的组合运用,培养学生的创新意识教材关联:教学内容与教材第四章“数字电路基础”中第四节“加法器”相关内容紧密关联,涵盖了四位全加器的基本原理、电路设计、实际应用等方面,为学生提供了系统性的学习指导。

层次化4位加法器设计 VHDL

课程设计说明书学院专业题目学号姓名同组人员报告完成日期成绩指导教师实验一层次化4位加法器设计一.实验目的1、掌握用 VHDL 设计全加器的方法并实现。

2、熟悉设计平台及VHDL层次化设计。

二.实验仪器1、硬件:计算机Gxsoc/sops-Dev-LabCycloneII EP2C35F672C8 核心板2、软件:正版Quartus8.0三.实验设计要求学习用VHDL或原理图设计方法,掌握全加器的设计方式及表示方式,极其与二进制表示的转换方法,完成编译、综合、适配、仿真和实验箱上的硬件测试,通过数码管观察结果。

采用层次化方法实现4位加法器,完成编译,仿真,引脚锁定,下载。

四.实验原理通过动态扫描两组4BIT的二进制数据,同时还有一个单BIT 的进位,把三者按照二进制加法原理进行加,求出和及进位,并通过电路显示出各部分数据(输入,输出)。

加数、被加数、“和”显示在共阳数码管上,进位输出显示在LED上。

五.程序代码1、半加器Hadder代码LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY HADDER ISPort (a,b: In Bit;Co, So: Out Bit);END HADDER;ARCHITECTURE fh1 Of HADDER Is BEGINSo <= (a Xor b);Co <= (a And b);END fh1;2、或门ora代码LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY ora ISPort ( a: in Std_Logic;b: in Std_Logic;c: out Std_Logic);END ora;ARCHITECTURE org OF ora ISBEGINc <= a Or b;END org;3、1位全加器f_hadder代码LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY f_ADDER ISPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END f_ADDER;ARCHITECTURE fd1 Of f_ADDER Is Component HADDERPort( a,b: In Std_Logic;co,so: Out Std_Logic);END Component;Component oraPort(a,b: In Std_Logic;c: Out Std_Logic);END Component;Signal d,e,f: Std_Logic;BeginU1: HADDERPort Map(a=>X,b=>Y,Co=>d,so=>e);U2:HADDERPort Map(a=>e,b=>cin,Co=>f,so=>sum);U3:ora Port Map(a=>d,b=>f,c=>cout);END ARCHITECTURE fd1;4、4位全加器Qadd:Library ieee;Use ieee.std_logic_1164.all;Entity Qadd isPort (a:in std_logic_VECTOR(3 DOWNTO 0);b:in std_logic_VECTOR(3 DOWNTO 0);--cin:in std_logic;s:out std_logic_VECTOR(3 DOWNTO 0)); End Qadd;Architecture one of Qadd isSignal c0,c1,c2,c3 : std_logic;Component f_ADDERPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END Component;Beginu1 :F_ADDERPort map(sum=>s(0),cout=>c0,X=>a(0),Y=>b(0),cin=>'0');u2 :F_ADDERPort map(sum=>s(1),cout=>c1,X=>a(1),Y=>b(1),cin=>c0 );u3 : F_ADDERPort map(sum=>s(2),cout=>c2,X=>a(2),Y=>b(2),cin=>c1 );u4 : F_ADDERPort map(sum=>s(3),cout=>c3,X=>a(3),Y=>b(3),cin=>c2 ); END;六.仿真结果程序代码进行编译后,建立waveform文件,设定输入输出端口进行仿真,仿真结果如图1-1所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

启动放置方块图进出点命令后,光标变成十字状,将光标移动到方块电路中,点击鼠标,光标上面出现一个小圆点,且光标将被限制在方块电路的左右边界内,确定合适的位置后点击鼠标,即可在该处放置一个方块图的进出点,点击右键结束放置方块图进出点状态。

2.设置方块图进出点对话框

三、电路的输入输出点

(8)此后我们就可以在这些输入输出点之间具体完成“Half Adder.Sch”原理图的绘制。

教师讲解示范,要求学生利用自上而下的层次电路设计方法完成电路:

主控模块电路图

4 Full Adder.sch

子系统方块图

Full Adder.Sch

基本模块原理图

Half Adder.Sch

示范

巡回指导

答疑

知识点3:电路的输入输出点

启动放置输入输出点的命令有两种方法:

1.点击画电路图工具栏里的图标 。

2.执行菜单“Place\Port”。

知识点4:层次电路设计方法

1.而下的设计方法

2.自下而上的设计方法

看一看:

教师示范

做一做:

学生练习

一、放置方块电路

1.放置方块电路。

2.设置方块电路编辑对话框

二、放置方块电路的进出点

【用层次原理图设计四位全加器】电子教案

授课教师:贡建霞班级:1210

时间:20XX年10月18日第二节地点:三楼CAD室

教学单元(章节):用层次原理图设计四位全加器

教学目标

1、了解层次电路设计方法;

2、掌握层次电路原理图的基本组成;

3、掌握层次电路原理图中的层次关系;

4、运用Protel 99 SE原理图编辑器绘制复杂的层次电路原理图;

观察操作

按照பைடு நூலகம்求完成设计

作品演示,总结提高

1、请掌握较快的学生演示操作

2、展示作品

3、本次课的主要内容总结

1、请学生演示,并分析其操作;

2、展示个别作品,分析其优点及存在的问题;

3、对每位学生的作品打分

4、总结

1、学生演示;

2、对个别作品展示,并进行分析;

作业布置,巩固提升

1、完成作品

2、对学习情况反思,想一想存在的问题和解决的方法

1.放置输入输出点

2.设置输入输出点

四、层次电路设计方法

讲解、示范操作

1、认真听讲

2、观察教师操作

3、动手操作,出现问题思考提问,熟练操作方法。

落实知识,完成任务:

层次电路设计实例

1.自上而下的层次电路设计方法

(1)在前面创建的项目里,执行菜单命令:File→New→schematic,创建一个新的原理图文件,并改名为主图4 Full Adder.sch。

(2)放置四个框图名字(Name)分别为F0-F3的方块图,内层电路名(File Name)为Full Adder。

(3)放置方块电路进出点,并编辑方块电路进出点名称。

(4)画出其它部分电路,和各方块图的进出点之间连线,完成后即可得到主控模块电路图。

(5)由项目方块图生成子系统方块图。执行菜单命令“Design\Create SheetFrom Symbol”,光标变成十字状,将光标移到方块电路模块F0上(注意不要指到方块图进出点上),单击鼠标,屏幕将出现下图所示的端口I/O方向确认对话框。

(6)此后我们就可以在这些输入输出点之间具体完成“FullAdder.Sch”原理图的绘制。

(7)由子系统方块图生成基本模块原理图。执行菜单命令“Design\Create Sheet From Symbol”,光标变成十字状,将光标移到方块电路模块H0上,与第五步操作一样,系统将自动在你以前创建的项目下产生原理图,文件名为“Half Adder.Sch”。

要求学生对所学反思

1、完成作品;

2、反思

落实知识,完成任务:

学习知识点

学一学:

知识点1:放置方块电路

启动放置方块电路方式有两种:

1.点击画电路图工具栏里的图标 。

2.执行菜单命令Place/Sheet Symbol。

知识点2:方块电路的进出点

启动放置方块电路进出点的命令有两种方式:

1.点击画电路图工具栏里的图标

2.执行菜单命令“Place\Add Sheet Entry”。

5、提高学生的动手能力及团队合作的意识。

教学重点

掌握层次电路原理图的基本组成

教学难点

运用Protel 99 SE原理图编辑器绘制复杂的层次电路原理图

教学环节

教学内容

教师活动

学生活动

创设情境

导入新课

看一看:

彩电的原理图

图片展示

介绍复杂的电路图无法在一张图纸中画下,引出层次设计

思考:当电路图无法在一张图纸中画下时,怎么办?