北京理工大学数电期末试卷(含答案)

北京理工大学数字电路第七章答案

北京理工大学数字电路第七章答案二进制数10101转换为十进制数后为() [单选题] *A.15B.21(正确答案)C.18D.10逻辑函数式D+D,简化后结果是() [单选题] *A.2DB.D(正确答案)C.D²D.0一位十六进制数可以用二进制数来表示,需要二进制的位数是() [单选题] *A.1B.2C.4(正确答案)D.16当决定某个事件的全部条件都具备时,这件事才会发生。

这种关系称为() [单选题] *A.或逻辑B.与逻辑(正确答案)C.非D.异或010*********的8421码为() [单选题] *A.496(正确答案)B.495C.598D.4694位二进制数可用十六进制数来表示,需要十六进制的位数是() [单选题] *A.1(正确答案)B.2C.3D.48421BCD码用4位二进制数表示十进制数的位数是() [单选题] *A.1(正确答案)B.2C.3D.4在数字电路中,不属于基本逻辑门是() [单选题] *A.与门B.或门C.非门D.与非门(正确答案)如图所示门电路,电路实现的逻辑式Y= [单选题] *A.Y=(AB)\B.Y=ABC.Y=A+B(正确答案)D.Y=(A+B)\如图所示的波形图表示的逻辑关系是()[单选题] *A.F=A·B(正确答案)B.F=A+BC.F=(A·B)\D.F=(A+B)\异或门F=A⊕B两输入端A、B中,A=1,则输出端F为() [单选题] *A.A⊕BB.B\(正确答案)C.BD.0下列表所示的真值表完成的逻辑函数式为()[单选题] *A.F=ABB.F=ABC.F=A⊕BD.F=A+B(正确答案)当A=B=0时,能实现F=1的逻辑运算是() [单选题] *A.F=A·BB.F=A+BC.F=A⊕BD.F=(A+B)\(正确答案)八位二进制数能表示十进制数的最大值是() [单选题] *A.255(正确答案)B.248C.192D.168将(01101)2转换为十进制数为() [单选题] *A.13(正确答案)B.61C.51D.25逻辑函数式Y=A+A,化简后的结果是() [单选题] *A.2AB.A(正确答案)C.1D.A2逻辑函数式Y=EF+E\+F\的逻辑值为() [单选题] *A.EFB.(EF)\C.0D.1(正确答案)以下表达式中符合逻辑运算法则的是() [单选题] *=C2B.1+1=10C.A·1=1D.A+1=1(正确答案)当逻辑函数有n个变量时,取值组合有() [单选题] *A.nB.2nC.n²D.2"(正确答案)二进制数码为(11101),则对应的十进制数为() [单选题] *A.29(正确答案)B.28C.13D.14下列说法中与BCD码的性质不符的是() [单选题] *A.一组四位二进制组成的码只能表示一位十进制B.BCD码是一种人为选定的0~9十个数字的代码C.BCD码是一组四位二进制数,能表示十六以内的任何一个十进制数(正确答案)D.BCD码有多种数字信号和模拟信号的不同之处是() [单选题] *A.数字信号在大小上不连续,时间上连续,而模拟信号则相反B.数字信号在大小上连续,时间上不连续,而模拟信号则相反C.数字信号在大小、时间上均不连续,而模拟信号则相反(正确答案)D.数字信号在大小、时间上均连续,而模拟信号则相反“与非”运算的结果是逻辑“0”的输入是() [单选题] *A.全部输入是“0”B.任一输入是“0”C.仅一输人是“0”D.全部输入是“1”(正确答案)相同为“0”不同为“1”,它的逻辑关系是() [单选题] *A.或逻辑B.与逻辑C.异或逻辑(正确答案)D.同或逻辑一只四输入端或非门,使其输出为“1”的输入变量取值组合有种。

北京理工大学2020年5月《数字电子技术》作业考核试题(答案)

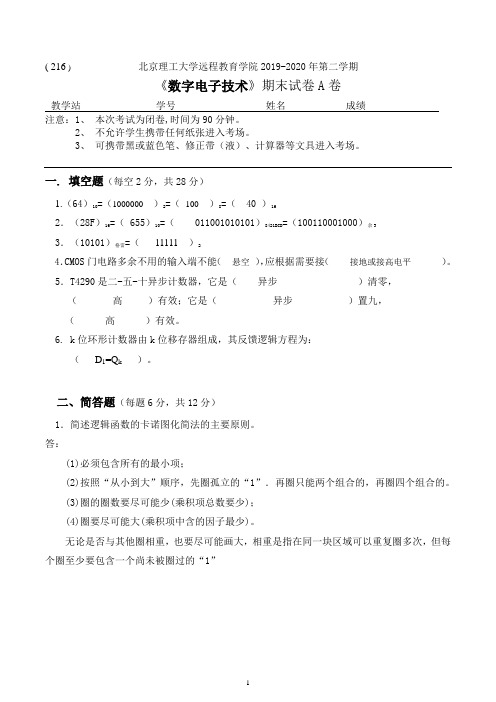

( 216 ) 北京理工大学远程教育学院2019-2020年第二学期《数字电子技术》期末试卷A卷教学站学号姓名成绩注意:1、本次考试为闭卷,时间为90分钟。

2、不允许学生携带任何纸张进入考场。

3、可携带黑或蓝色笔、修正带(液)、计算器等文具进入考场。

一. 填空题(每空2分,共28分)1.(64)10=(1000000)2=(100)8=( 40 )162.(28F)16=( 655)10=( 011001010101)8421BCD=(100110001000)余33.(10101)格雷=(11111 )24.CMOS门电路多余不用的输入端不能(悬空),应根据需要接(接地或接高电平)。

5.T4290是二-五-十异步计数器,它是(异步)清零,(高)有效;它是(异步)置九,(高)有效。

6. k位环形计数器由k位移存器组成,其反馈逻辑方程为:(D1=Q k)。

二、简答题(每题6分,共12分)1.简述逻辑函数的卡诺图化简法的主要原则。

答:(1)必须包含所有的最小项;(2)按照“从小到大”顺序,先圈孤立的“1”.再圈只能两个组合的,再圈四个组合的。

(3)圈的圈数要尽可能少(乘积项总数要少);(4)圈要尽可能大(乘积项中含的因子最少)。

无论是否与其他圈相重,也要尽可能画大,相重是指在同一块区域可以重复圈多次,但每个圈至少要包含一个尚未被圈过的“1”2.简述单稳态触发器的三个显著特点:答:(1)电路有一个稳态、一个暂态。

(2)在外来触发信号的作用下,电路由稳态翻转到暂稳态。

(3)哲稳态是一个不能长久保持的状态,经一段时间后电路会自动回到稳态。

暂态的持续时间取决于电路本身的参数。

三、分析题(每题10分,共20分)1.在图1所示电路中,试写出当图1中的“与非”门分别是TTL、CMOS两类门时的输出电平。

答:TTL:F=0 电平约为:0.2V; MOS:F=1 电平约为:5V。

F V IH图110k2.请写出D触发器的特性表,及画出工作波形图。

北京理工大学《高等数学》历年期末考试试题及答案解析(精编版)

x = (t − 1)et 八. 设曲线 C 的方程为 y = 1 − t4

求

dy dx

,

d2y dx2

及曲线

C

在参数

t

=

0

对应点处

–2/48–

第 1 部分 北京理工大学试题集

的曲率半径.

九. 设 f ′(x).

f (x)

=

1 x

−

ex

1 −

1,

x

<

0

1

−

1 c2os x

x

,

, x

x= >0

等于

mg k

.

∫1

十一. 设 f (x) 在 [0, 1] 上连续, 在 (0, 1) 内可导, 且满足 f (1) = 2 2 xe1−x f (x)dx, 证明:

0

至少存在一点 ξ, 使得 f ′(ξ) = (1 − ξ−1) f (ξ).

1.2 2011 级秋季学期期末试卷

一. 填空题

1. 极限 lim

x→0

x

− ln(1 x2

+

x)

=

2. 设 y

=

x2 + ln x, 则

dx dy

=

dy =

∫∞

3. 广义积分

e

dx x ln2

x

=

4.

微分方程

y′′

=

1

1 + x2

的通解为

; lim

1

∫

x

(1

+

sin

2t)

1 t

dt

=

.

x→0 x 0

√ ; 设 f 可导,y = f (tan x) + 1 − x2, 则

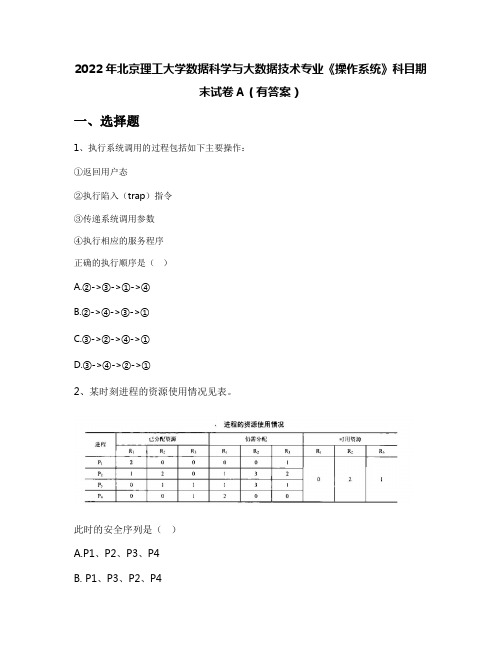

2022年北京理工大学数据科学与大数据技术专业《操作系统》科目期末试卷A(有答案)

2022年北京理工大学数据科学与大数据技术专业《操作系统》科目期末试卷A(有答案)一、选择题1、执行系统调用的过程包括如下主要操作:①返回用户态②执行陷入(trap)指令③传递系统调用参数④执行相应的服务程序正确的执行顺序是()A.②->③->①->④B.②->④->③->①C.③->②->④->①D.③->④->②->①2、某时刻进程的资源使用情况见表。

此时的安全序列是()A.P1、P2、P3、P4B. P1、P3、P2、P4C. P1、P4、P3、P2D.不存在3、下列描述中,()并不是多线程系统的特长。

A.利用线程并行地执行矩阵乘法运算B.Web服务器利用线程响应HTTP请求C.键盘驱动程序为每个正在运行的应用配备一个线程,用以响应该应用的键盘输入,D.基于GUI的调试程序用不同的线程分别处理用户输入、计算和跟踪等操作4、若系统中有n个进程,则在阻塞队列中进程的个数最多为()?Α. n B.n-1 C.n-2 D.15、采用时间片轮转调度算法分配CPU时,当处于执行状态的进程用完一个时间片后,它的状态是()A.阻塞B.运行C.就绪D.消亡6、下列有关设备独立性的说法中,正确的是()。

A.设备独立性是指I/O设备具有独立执行I/O功能的种特性B.设备独立性是指用户程序独立于具体物理设备的·种特性,C.设备独立性是指能够实现设备共享的一种特性D.设备独立性是指设备驱动程序独立于具体物理设备的·种特性,7、某进程的段表内容见表,当访问段号为2、段内地址为400的逻辑地址时,进行地址转换的结果是()。

A.段缺失异常B.得到内存地址4400C.越权异常D.越界异常8、已知某磁盘的平均转速为r秒/转,平均寻找时间为T秒,每个磁道可以存储的字节数为N,现向该磁盘读写b字节的数据,采用随机寻道的方法,每道的所有扇区组成一个簇,其平均访问时间是()。

数字电子技术基础_北京理工大学中国大学mooc课后章节答案期末考试题库2023年

数字电子技术基础_北京理工大学中国大学mooc课后章节答案期末考试题库2023年1.逐次渐近型8位A/D转换器中的8位D/A转换器的Vomax=10.2V,若输入为3V,则转换后的数字输出D为:答案:010010112.用ROM设计逻辑电路实现两个两位二进数的全加运算,则需要ROM的地址线和数据线至少为:答案:5,33.存储容量为8k×16位的RAM,地址线有()根。

答案:134.静态RAM一般采用MOS管的栅极电容来存储信息,必须由刷新电路定期刷新。

答案:错误5.以下触发器电路中能够实现二进制计数器(对输入的时钟进行计数,辨识两个时钟周期)功能的电路有:答案:___6.ROM为只读存储器,因此不能对其进行写操作。

答案:错误7.施密特触发器具有两个稳定状态。

答案:正确8.由555定时器构成的电路如图所示,则此电路能够实现()功能。

【图片】答案:单稳态触发器9.555定时器构成电路如图所示,则此电路的功能为:【图片】答案:施密特触发器10.【图片】上图可以实现的逻辑功能为:答案:半减器11.下图所示74LS151为8选1数据选择器,当用此器件设计逻辑函数【图片】时,D0D1D2D3D4D5D6D7应分别连接到:【图片】答案:0100101012.如图所示74LS283为四位二进制加法计数器,如果要将输入的8421BCD码D3D2D1D1转换为余3码F3F2F1F0,并且把D3D2D1D1分别接到输入端A3A2A1A0上,则输入端B3B2B1B0和低位进位输入CI分别接到:【图片】答案:0010113.已知TTL反相器电路的参数如下:VOH/ VOL=3.6V/0.3V,IOH/IOL=0.2mA/8mA, IIH/ IIL=20uA/0.4mA ,则其驱动同类门的数量即其扇出系数为多少。

答案:1014.三位环形计数器的模为()?答案:315.如图所示电路输出信号为00110010。

【图片】答案:正确16.单稳态触发器输出信号的脉宽由输入的触发信号决定。

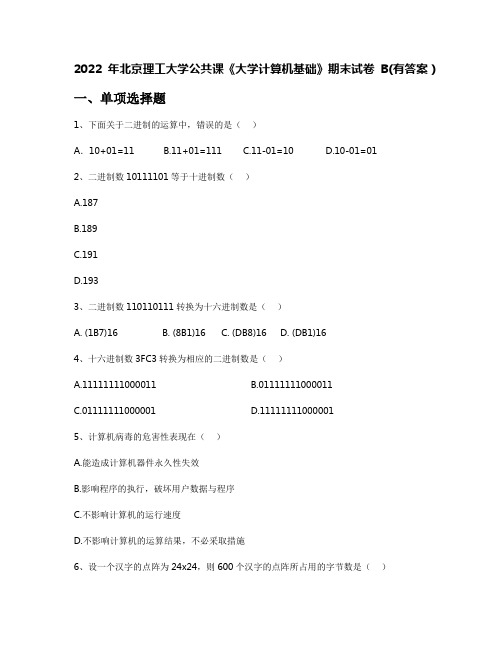

2022年北京理工大学公共课《大学计算机基础》期末试卷B(有答案)

2022年北京理工大学公共课《大学计算机基础》期末试卷B(有答案)一、单项选择题1、下面关于二进制的运算中,错误的是()A.10+01=11 B.11+01=111 C.11-01=10 D.10-01=012、二进制数10111101等于十进制数()A.187B.189C.191D.1933、二进制数110110111转换为十六进制数是()A. (1B7)16B. (8B1)16C. (DB8)16D. (DB1)164、十六进制数3FC3转换为相应的二进制数是()A.11111111000011B.01111111000011C.01111111000001D.111111110000015、计算机病毒的危害性表现在()A.能造成计算机器件永久性失效B.影响程序的执行,破坏用户数据与程序C.不影响计算机的运行速度D.不影响计算机的运算结果,不必采取措施6、设一个汉字的点阵为24x24,则600个汉字的点阵所占用的字节数是()B.72 x600C.192 x600D.576 x6007、世界上第一台具有程序存储功能的计算机是()A.ENIACB.EDSACC.EDVAC8、在Windows 7“资源管理器”中,若要用鼠标拖动的方法进行不同文件夹的文件移动操作,选择文件后,应()A.直接用鼠标左键拖拽文件.B.按住Alt键同时用鼠标左键拖拽文件C.按住Shift键同时鼠标左键拖拽文件D.按住Ctrl键同时用鼠标左键拖拽文件9、在Windows 7系统中,利用标题栏左边的控制菜单,不能完成的操作是()A.打开窗口B.改变密口的大小C.关闭窗口D.移动窗口10、剪贴板是个临时存储区,它属于什么的一部分()A.内存B.硬盘C.光盘D.BIOS11、在Windows 7的“剪贴板”操作中,“粘贴”命令的组合键是()A.Ctrl+CB.Ctrl+XC.Ctrl+A12、在Windows 7中,想选定多个文件名,如这多个文件名连续成一个区域的,则先选定第一个文件名,然后按住()键,再在最后一个文件名上单击一下即可。

数电考试题及答案

数电考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算答案:C2. 一个触发器可以存储()位二进制信息。

A. 1B. 2C. 4D. 8答案:A3. 以下哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时间延迟C. 输出状态不依赖于电路的历史状态D. 输出状态不依赖于电路的初始状态答案:B4. 一个4位二进制计数器可以计数的最大值是()。

A. 15B. 16C. 255D. 256答案:B5. 以下哪个不是时序逻辑电路的特点?()A. 输出不仅依赖于当前输入,还依赖于电路的历史状态B. 输出与输入之间存在时间延迟C. 输出状态不依赖于电路的初始状态D. 输出状态依赖于电路的初始状态答案:C6. 在数字电路中,使用最多的触发器是()。

A. SR触发器B. JK触发器C. D触发器D. T触发器答案:C7. 一个3线-8线译码器可以译码()种不同的输入信号。

A. 3B. 4C. 8D. 27答案:C8. 以下哪个不是数字电路的优点?()A. 高抗干扰性B. 高稳定性C. 低功耗D. 易于集成答案:C9. 在一个二进制计数器中,如果计数器从0开始计数,那么它的第一个状态是()。

A. 0000B. 0001D. 0101答案:B10. 以下哪个不是数字电路设计中常用的简化方法?()A. 布尔代数简化B. 卡诺图简化C. 逻辑门替换D. 电阻网络简化答案:D二、多项选择题(每题3分,共15分)11. 下列哪些是数字电路中常用的逻辑门?()A. 与门B. 或门D. 异或门E. 与非门答案:ABCDE12. 在数字电路中,以下哪些因素会影响电路的稳定性?()A. 电源电压波动B. 温度变化C. 信号传输延迟D. 电路的初始状态E. 电路的负载答案:ABDE13. 以下哪些是时序逻辑电路的基本组成元素?()A. 触发器B. 计数器D. 译码器E. 编码器答案:ABC14. 在数字电路中,以下哪些是常用的计数器类型?()A. 二进制计数器B. 十进制计数器C. 约翰逊计数器D. 环形计数器E. 移位寄存器答案:ABCD15. 以下哪些是数字电路设计中常用的测试方法?()A. 功能测试B. 时序测试C. 静态测试D. 动态测试E. 模拟测试答案:ABCD三、填空题(每题2分,共20分)16. 在数字电路中,一个基本的与门电路有 ______ 个输入端和______ 个输出端。

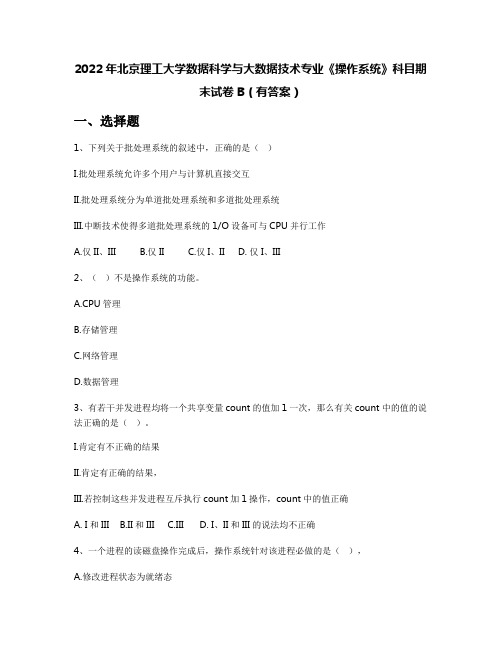

2022年北京理工大学数据科学与大数据技术专业《操作系统》科目期末试卷B(有答案)

2022年北京理工大学数据科学与大数据技术专业《操作系统》科目期末试卷B(有答案)一、选择题1、下列关于批处理系统的叙述中,正确的是()I.批处理系统允许多个用户与计算机直接交互II.批处理系统分为单道批处理系统和多道批处理系统III.中断技术使得多道批处理系统的1/O设备可与CPU并行工作A.仅II、IIIB.仅IIC.仅I、IID. 仅I、III2、()不是操作系统的功能。

A.CPU管理B.存储管理C.网络管理D.数据管理3、有若干并发进程均将一个共享变量count的值加1一次,那么有关count中的值的说法正确的是()。

I.肯定有不正确的结果II.肯定有正确的结果,III.若控制这些并发进程互斥执行count加1操作,count中的值正确A. I和IIIB.II和IIIC.IIID. I、II和III的说法均不正确4、一个进程的读磁盘操作完成后,操作系统针对该进程必做的是(),A.修改进程状态为就绪态B.降低进程优先级C.给进程分配用户内存空间D.增加进程时间片大小5、进程从运行态到阻塞态可能是()A.运行进程执行P操作B.进程调度程序的调度C.运行进程的时间片用完D.运行进程执行了V操作6、缓冲技术的缓冲池通常设立在()中。

A.主存B.外存C.ROMD.寄存器7、若I/O所花费的时间比CPU的处理时间短很多,则缓冲区()A.最有效B.几乎无效C.均衡D.以上都不是8、若某文件系统索引节点(inode)中有直接地址项和间接地址项,则下列选项中,与单个文件长度无关的因素是().A.索引节点的总数B.间接地址索引的级数C.地址项的个数D.文件块大小9、在文件系统中,若文件的物理结构采用连续结构,则文件控制块FCB中有关文件的物理位置的信息包括(),I.首块地址 II.文件长度 III.索引表地址A.只有IIIB. I和IIC. II和IIID. I和III10、在可变分区分配管理中,某一作业完成后,系统收回其内存空间,并与相邻区合并,为此修改空闲区说明表,造成空闲分区数减1的情况是()。