集成电路中esd失效机理分析

由版图引起的CMOS+ESD保护电路失效的分析

万方数据陶删磊等:由版图引起的cM0sEsD保护电路失效的分析又可能出现在寄生回路部位)。

本文通过两种EsD保护电路中的典型失效实例,研究了它们产生EsD失效的机理,并提出了改进EsD保护电路设计的方法。

EsD保护结构因外部原因或本身的结构缺陷产生击穿时,首先是漏区的pn结发生反向击穿,通过寄生的横向晶体管泄放电流。

此时,若电流不再增大,则只造成漏区的反向击穿,使击穿电压下降,漏电流加大,在击穿位置会产生红外发光点。

如果电流继续增加,就会发生二次击穿,结果就会出现闩锁效应。

此外,EsD保护结构发生介质层击穿时也会产生微弱的红外发光。

利用EsD保护结构在击穿失效时的“显微红外发光”现象【4J,并结合显微红外发光显微镜EMMI和0BIRcH的使用瞪J,本文快速准确地对由EsD应力导致的失效点进行定位,并借助于使用sEM等结构、形貌分析手段,为进一步的电路级的分析提供基础。

2ESD保护电路的失效分析21保护电路电流泄放能力不足在人体放电模式(HBM)下对一个采用0.6“m工艺制程的功率cMosIc器件进行L/O.GND(+)测试时,按照文献[6]中的标准,每个引脚各测3次,测试结果见表1。

从表l中发现2+引脚抗EsD电压仅为500v(取3次测试中的最小值)。

图1失效的ESD保护电路的PEM照片表1HBM下的ESD电压测试结果结合版图分析,发现发光部位是一个充当EsD保护电路的GGNM0s的漏区,直接用光学显微镜观察发光部位,未能看到明显的损伤。

在进行表面铝布线的全剥离之后,再对发光部位进行sEM观察f网21.枯珊漏匮的砗一绨瓠仆熔融.百T毗看厶r分析发现在该引脚处存在很大的漏电流。

将器件开封后用显微红外发光显微镜EMMI和0BIRcH进行观察。

如图1所示,发现在OBIRcH照片上有明显的电阻异常现象,在EMMI的照片上存在明显的红外发光点a图2蒲区部位的sEM照片1004半导体技术第32卷茅11期2007年11月 万方数据陶割磊等:由版图引起的cM0sEsD保护电路失效的分析到有明显的损伤,这就是导致器件未能通过EsD测试的原因。

(二)半导体集成电路的失效机理及其预防措施

半导体集成电路的失效机理及其预防措施半导体集成电路的失效机理及其预防措施((小结小结))Xie Meng-xian. (电子科大,成都市)因为集成电路是由许多元器件组成的,所以其中元器件的失效必然会导致集成电路的失效,然而引起半导体集成电路(IC )失效的机理尚不仅如此,实际上还要复杂得多,有关系到设计方面的,也有关系到工艺方面的。

与集成电路设计密切相关的、能够做到部分或者完全避免的一些失效机理,主要有如下11种。

(1)静电放电静电放电((ESD ):IC 端头上积累的静电电荷可以产生很高的电压,从而会引起p-n 结击穿(造成短路或者大的漏电流)、或者使栅氧化层马上击穿或经过一段时间以后穿通。

为了防止静电放电所引起的失效,首先,在多数管脚上需要设置抗ESD 的保护器件;但连接到衬底的管脚、或者连接到大面积扩散区上的管脚(例如与npn 晶体管集电极相连的管脚),则不需要加保护器件。

其次,对于采用薄发射极氧化物工艺的BJT ,与管脚相连的内引线不能在薄的发射极氧化层上走线(穿越),否则可能引起薄发射极氧化层的击穿;不过对于采用较厚发射极氧化物的标准双极工艺而言,就不必考虑这种限制。

此外,在使用IC 时也要特别注意防止静电的产生和积累,如采用静电屏蔽,腕带、电烙铁和工作台要接地,室内要保持一定的湿度等。

(2)电迁移电迁移::IC 在大电流、高温下、长时间工作之后,就有可能产生电迁移失效,即出现金属电极连线发生断裂(开路)或者短路的现象。

防止电迁移的根本措施就是限制通过连线的最大电流(这与金属成分、厚度和温度有关)。

对于不穿越氧化层的导线,单位宽度上的电流一般要小于2mA/µm ;而对于穿越氧化层的导线,一般要小于1mA/µm 。

金属层的厚度和宽度越大,则抗电迁移的能力就越强。

另外,改进电迁移的主要措施有如:在电极金属Al 中掺入原子质量较大的Cu (0.5%~4%),这可使大电流承受能力提高5~10倍;采用耐热性好的势垒金属等。

集成电路中ESD防护研究

集成电路中ESD防护研究作者:赵瑞来源:《环球市场》2017年第20期摘要:随着集成电路的发展,芯片采用先进的工艺,性能越来越好。

然而这些先进的工艺对芯片的静电放电(ESD)的承受能力削弱,同时人们对于芯片 ESD 的防护要求不但没有降低,反而越来越高,这使得 ESD 防护电路更加不容易设计。

国内 ESD 防护的研究相对落后于国际先进水平,特别是国产的集成电路芯片,ESD 已经使芯片的成品率和可靠性大大降低,因此对芯片 ESD 的研究意义非常重大。

本文对集成电路的 ESD 防护技术进行了研究。

关键词:集成电路;ESD 防护技术;应用当今科技日新月异,发展更新速度飞快,尤其是是在电子信息领域。

在集成电路设计方面,集成电路(IC)的工艺水平不断发展进步,集成电路的工艺尺寸不断下降,高分子材料也在集成电路中得到广泛使用,但是在器件特征尺寸的缩小以及新材料得到应用的同时,不可避免的会带来一些负面的影响,其中静电放电(Electrostatic Discharge,ESD)保护器件的设计就变得越来越困难,使得产品的静电现象的产生日益严重,因而静电的危险性越来越大,也使得芯片的静电放电(ESD)保护电路的设计越来越复杂。

1、ESD防护电路设计的基本原则①保护器件在电路正常工作的时候必须处于关闭状态(即没有ESD事件发生时),这与ESD器件的触发电压有关,否则误触发会导致核心电路出现故障;②当微电子芯片遭遇ESD 事件时,该保护器件必须迅速打开(纳秒级别),特别是对于快的ESD事件尤为重要,如器件充电模型(CDM),否则如果保护电路不能及时开启,会导致核心电路损毁;③芯片pin管脚上的电压(即落在ESD保护器件上的电压与金属互连线上的电压之和),必须不能超过核心电路所能承受的最高电压,否则会导致核心电路损毁;④在设计的ESD保护等级下,保护电路必须不被损毁,这是ESD器件鲁棒性相关问题;⑤在ESD事件发生过后,保护器件必须回到关闭状态,否则,器件会进入到被禁止的闩锁状态,导致核心电路发生故障。

ESD机理与测试_AEC-Q100-002

ESD(electrostatic discharge):摩擦生电使电荷聚集起来,当聚集有电荷的物体接触器件时,通过器件的管脚与地之间形成放电通道,当聚集的电荷足够多时,这样的快速放电,会形成很大的电流(几十安级),对微安或毫安级的集成电路来说,或造成严重损伤。

损伤的可能情况如下:1,由于介质击穿而导致氧化物薄膜破裂。

2,导致金属导线熔化。

3,由于寄生的pn结而导致CMOS器件闭锁。

4,产生隐藏的缺陷。

5,强电场对附近的电器引起干扰或故障。

某些损伤会使器件立即失效,称为硬损伤,比如pn结损伤或烧毁,金属层失效,氧化层击穿。

有些损伤是潜在的,随着时间增加才显现出来。

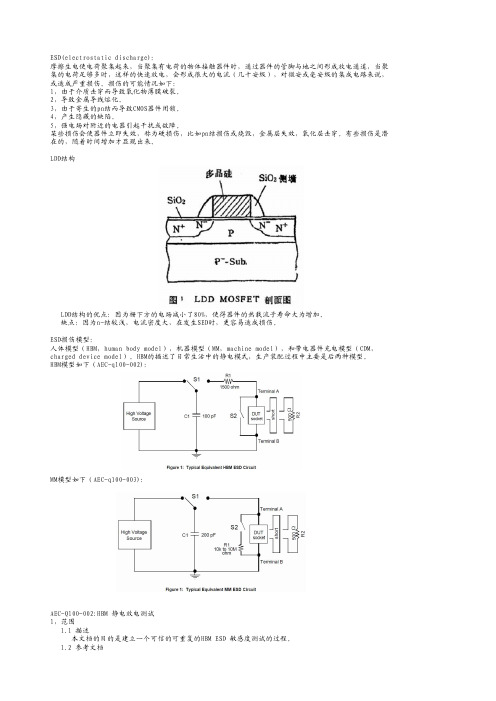

LDD结构LDD结构的优点:因为栅下方的电场减小了80%,使得器件的热载流子寿命大为增加。

缺点:因为n-结较浅,电流密度大,在发生SED时,更容易造成损伤。

ESD损伤模型:人体模型(HBM,human body model),机器模型(MM,machine model),和带电器件充电模型(CDM,charged device model)。

HBM的描述了日常生活中的静电模式,生产装配过程中主要是后两种模型。

HBM模型如下(AEC-q100-002):MM模型如下(AEC-q100-003):AEC-Q100-002:HBM 静电放电测试1,范围1.1 描述本文档的目的是建立一个可信的可重复的HBM ESD 敏感度测试的过程。

1.2 参考文档1.3 术语和定义1.3.1 器件失效在某条件下,器件不能完全满足第5节定义的可接受的标准,视为失效。

1.3.2 DUT被评价ESD敏感性的电子器件。

1.3.3 ESD在不同的静电势的物体之间的静电转移。

1.3.4 ESD敏感度导致器件失效的静电电势级别。

1.3.5 静电放电模拟器本文介绍的用于模拟HBM ESD脉冲的设备。

1.3.6 HBM ESD满足本文指定的波形的ESD脉冲。

1.3.7 非电源引脚所有的引脚,但是不仅限于,in,out,inout,Vref,Vpp,clock,和no connect引脚。

典型ESD防护器件失效机理

Abstract: Transient voltage suppression ( TVS) is used commonly in electronic circuit design as the ESD protection device,and its reliability would greatly impact on the safety of the whole circuit. The bidirectional TVS device PESD5V0U1BA is researched,the short - circuit failure mechanism of the device and its effects were researched by experiment and simulation. The results show that while the TVS device is applied high voltage,the SiO2 with defects would occur selfhealing punch - through; when the pn junctions of the device is punchthroughed,the TVS device would failure. After the two pn junctions of the TVS device are both punchthroughed,its IV characteristic would performance as the resistance characteristic. While the TVS device is failure,its clamp function can still be observed,and the clamp voltage is even lower,but the leakage current of the device has increased and it would influence the normal working of the protected circuit. Key words: transient voltage suppression ( TVS ) ; failure model; leakage current; second breakdown EEACC: 2000

ESD失效分析FA及案例介绍

• 在CDM ESD冲击下,有类似的DS silicon filament defect,但较 HBM少,特点是振荡较少

(3)成分观察: EDAS、电子微探针显微分析(EPMA)、俄歇电子能谱(AES)

、x射线光电子能谱(xPS)、二次离子质谱(SIMs)等方法

信息产业部软件与集成电路促进中心 ZJU-UCF联合ESD实验室

典型的失效形式

• 1、D-S silicon filament defect due to high ESD stress field

信息产业部软件与集成电路促进中心 ZJU-UCF联合ESD实验室

信息产业部软件与集成电路促进中心 ZJU-UCF联合ESD实验室

(1)一般的失效机理

失效分析的手段: (1)形貌观察: • 光学显微镜:最常用,观察器件的表面和逐层剥除的次表面。对于光学显

微镜放大倍数是500倍,使用冶金显微镜可以达到1000倍,使用特殊的液 体透镜技术,可以达到1500倍,1000-1500可以观察到1微米线宽缺陷。 • SEM:更高倍数15000倍,使用背散射二次电子和样品倾斜台还可以获得 一定的三维图像),存在电荷积累,可以使用扫描离子显微镜SIM,TEM :更高的解析度。可以观察缺陷位错。不需要真空的可以用AFM:会受到 表面电荷等的影响。 • 对于需要透视观察的,平面的可以用SAM(电声显微镜,特别是铝钉) ,三维的可以用X射线显微镜,或者使用RIE:反应离子刻蚀,逐层剥除 观察。 • FIB:聚焦离子束,用离子束代替电子束观察显微结构,可以透视剥除金 属或者钝化层观察,所以FIB也可用于VLSI的纠错(可以加装能谱)

ESD

ESD测试及原理介绍BYD Microelectronics ConfidentialMenu-11 2 3 4ESD基本介绍 ESD失效模式和失效机理 ESD测试模式,原理及测试方法 常见ESD保护结构及原理BYD Microelectronics Confidential一 ESD的基本介绍BYD Microelectronics Confidential背景在人们的日常工作生活中, 静电放电(ESD)现象可谓无处不在, 瞬间产生的上 升时间低于纳秒(ns)、持续时间可达数百纳秒且高达数十安培的电流, 会对手 机、 笔记本电脑等电子系统造成损伤。

对于电子系统设计人员而言, 如果没有采取适 当的ESD 保护措施, 所设计的电子产品就会有遭到损伤的可能。

静电放电( ESD, Electrostatic Discharge) 给电子器件环境会带来破坏性的后 果。

它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,互补 金属氧化物半导体( CMOS, ComplementaryMetal- Oxide Semiconductor) 的特 征尺寸不断缩小,金属氧化物半导体(MOS, Metal- Oxide Semiconductor)的栅氧 厚度越来越薄,MOS 管能承受的电流和电压也越来越小, 因此要进一步优化电路 的抗ESD 性能, 需要从全芯片ESD 保护结构的设计来进行考虑。

BYD Microelectronics ConfidentialESD的产生及影响一般来讲,一个充电的导体接近另一个导体时,就可能发生ESD。

首先,两个导 体之间会建立一个很强的电场,产生由电场引起的击穿。

两个导体之间的电压超 过它们之间空气和绝缘介质的击穿电压时,就会产生电弧。

在0. 7 ns~10. 0 ns 的时间里,电弧电流会达到几十安培,有时甚至超过100 A。

电弧将一直维持直到 两个导体接触短路或者电流低到不能维持电弧为止。

IC卡封装中的ESD影响及对策

IC卡封装中的ESD影响及对策1、引言ESD对整个半导体产业具有非常大的影响,每年半导体工业因为ESD造成的经济损失以数十亿美元计。

随着金卡工程和IC卡国产化在中国的逐步深入推广,ESD对IC卡模块封装这种集成电路封装形式的影响成为一个研究课题。

ESD的产生机理是什么?它对IC卡模块封装的影响体现在哪些方面?对这些影响应该采取什么措施去改善或消除?本文对上述问题进行了初步的探讨,并结合上海斯伦贝谢智能卡技术有限公司的实际例子提出了几点控制ESD影响的简单措施。

2、ESD及产生原因组成物质的原子包含电子和质子。

物质获得或者损失电子时,物质表现为带有正电或负电。

静电是正电荷或负电荷在物质表面积累的结果。

电荷积累通常由物质的接触、分离或者摩擦引起,通常称为摩擦生电。

影响电荷积累的因素很多,包括物体的接触程度、摩擦系数和分离速率等。

在影响因素消除之前,电荷会持续积累,随后释放,或者一直积累到周围物质的绝缘属性或绝缘保护失效为止。

一旦绝缘属性被改变,会迅速实现静电平衡。

ESD(Electrostatic Storage Deflection,静电积聚转移)是电荷的快速平衡,电荷的迅速平衡被称为静电放电。

研究表明,人走在地毯上由于摩擦产生的电荷,可引发高达20KV的静电压。

由于电荷是在阻力很小的情况下迅速释放的,因此释放时的等效电流可以超过20安培。

如果是通过集成电路或者其它对ESD敏感的元器件放电,那么大电流很可能会严重损坏原本只能传导微安级或毫安级电流的线路。

3、ESD对IC卡模块封装的影响ESD的影响存在于晶圆片生产、集成电路封装、器件测试、装配和使用的集成电路整个生命周期。

不管什么原因,只要在器件表面或周围区域积累电荷,就会产生ESD。

ESD每年造成的半导体工业经济损失高达数十亿美元。

集成电路器件对ESD非常敏感。

集成电路器件应该工作在一定的电压、电流和功耗限定范围内。

大量聚集的静电荷在条件适宜时就会产生高压放电(如空气湿度高于65%,或操作人员的接触等),静电放电通过器件引线的高压瞬时传送,可能会使氧化层(即绝缘体)断开,造成器件功能失常。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二阶段是指在热、电正反馈作用下,迅速使氧化层击穿的过程。栅氧寿命主要由第一阶段中的建立时间所决定。对电应力下氧化层中及界面处产生的缺陷,一般多认为是电荷引起的,对电荷的性质,主要有二种理论模型:负电荷积累模型和正电荷积累模型[2]。

人体与被放电体之间的放电有两种:接触放电和电弧放电。接触放电时人体与被放电体之间的电阻值是一个恒定值。电弧放电是在人体与放电体之间有一定的距离时,他们之间空间的电场强度大于其介质(如空气)的介电强度,介质电离时产生电弧放电。电弧放电的特点是放电回路在放电初期,由于介质电离,放电回路电阻值较小,随着静电电荷的减少,静电电压减小,介质不再电离放电。有关HBM的ESD已有工业测试的标准,JEDEC EIA/JESD22~A114,MIL—STD883E等。

ESD保护电路的作用在于将出现在芯片管脚上的高电荷按照预先设计好的路径泄放掉,进而防止静电对内部电路的损坏。所以通过对ESD引起失效的器件进行物理失效分析,将有利于改善ESD电路性能和提高ESD防护等级。本文将对静电产生的危害及相关静电模型和ESD失效机理以及失效特征和如何进行预防进行阐述。

1

1.1静电产生的物理原理

(2)机器模型(Machine Model--MM),在日本和欧洲应用相当厂泛,被称为“第二种ESD模型”

当IC在制造和使用过程中,机器本身累积了静电,当此机器接触到IC时,静电便经由管脚放电。这种ESD用机器模型来描述。该模型的测试标准常见的为国际电子行业标准:EIAJ-IC-121中的方法20。由于大多数机器都是用金属制造的,其等效电阻为0Ω,但其等效电容定为20pF。其放电过程短,在几ns到几十ns之内会有数安培的瞬间放电电流产生。MM是判断器件对机器(包括SMT、测试平台等)触碰器件的静电放电的防护能力,所用判断标准是标准为JESD22一A1。

(4)电荷陷阱

静电放电产生的高压瞬时脉冲会破坏器件上的电荷平衡,从而形成电荷陷阱。大量的电荷积聚在器件表面形成反型层,该反型层提供了电流泄漏通路,反型层泄漏是一个与时间和温度有关的退化现象,它会导致器件完全失效。

(5)PN结衰减

通过观察硅 PN 结的 I-V 特性曲线就可以发现它是否已经损伤。瞬时的局部加热或电应力都会使铝硅合金丝状化,这些丝状物构成了一个并行分流器,在反偏 I-V特性曲线上形成一个尖锐的拐点。铝硅合金熔融需要很高的温度。在ESD引起损伤的事件中,PN 结丝状横截面积变得很小,以至于在使用过程中产生局部加热,从而导致失效。静电放电熔断如此小的细丝是非常可能的,从而使器件虽然可以使用但却不再可靠。

静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时产生的一种现象。静电现象是指电荷在产生与消失过程中所表现出的现象的总称,如摩擦起电就是一种静电现象。静电产生原因有接触分离起电、摩擦起电、感应起电和传导起电等。

1.2静电放电危害

由于物体间的接触分离(如摩擦、剥离、撕裂和搬运中的碰撞等)或电场感应,都会因物体之间或物体内部带电粒子的扩散、转移或迁移而形成物体表面电荷的积聚,即呈现带电现象。这种现象的存在,有可能导致物体表面电荷对空气中带异性电荷的微粒子尘埃的吸引造成电子敏感元器件绝缘性能的降低、结构腐蚀或破坏。当外界条件适宜时,这种积聚电荷还会产生静电放电,使元器件局部破损或击穿,严重时,还会引起火灾、爆炸等。曾报道某厂在修理程控交换机上的半导体集成电路时因静电引起爆炸事故的文章[1]。应当指出,静电引起电子元器件局部结构破损和性能降低,是对元器件使用寿命的一种潜在威胁,因为它难于检验,故造成事故的随机性更大,并且易于与其他失效原因混淆而被掩盖。

集成电路中esd失效机理分析

摘

静电放电对微电子器件的危害越来越受到人们的重视。本文简介了静电的产生及静电释放的危害,介绍了人体模型、机器模型和带电器件模型等模型。然后通过对静电放电过程的研究建立放电模型,分析了静电放电的失效模式和失效机理和其对半导体器件的损坏机理。其中从理论角度突出对ESD失效机理和失效位置的研究;通过借助仪器分析的结果对ESD失效案例的ESD放电模型做了合理推断,这种通过失效分析推断放电路径的方法对于改善ESD保护电路性能和提高ESD防护等级有着重要参考作用。最后论述ESD失效的预防措施,分别从外部措施和内部措施提出预防静电放电的方法。

ThenThispaper tries to start with thephysical theory of electrostatic toexplore the progress of ESD and set up the model of ESD. The paper analysesin details the process of ESD and several ESD models and the mechanism ofESD damage semiconductor devices.

Key words:

ESDMicroelectronic DevicesFailure ModeFailure Mechanism

0

环境中存在静电,这种静电电压从几百伏到几千伏甚至更高,如果没有任何静电保护结构,集成电路在存储、运输以及使用工程中很容易被静电损伤。静电放电(ESD)是两个靠近的带电体之间电荷再次平衡的过程,当带静电的人或物体与MOS器件的引脚接触,并通过器件向地或者其他物体放电时,高电压及其产生的大电流可能造成器件的损伤。ESD保护结构能将高压静电转化成瞬态低压大电流,最终将电流泄放,从而达到保护集成电路的目的。ESD保护结构的特征和要求主要有:具有迅速的泄放静电的能力,在静电泄放过程中,保护结构本身不会被损伤。

基于ESD产生的原因及其对集成电路放电的不同方式,通常将静电放电事件分为以下几类模型:人体模型(HBM)、机器模型(MM)、带电器件模型(CDM)、传输线脉冲模型(TLPM)等。

(1)人体模型(Human Body Mode--HBM)

当带有静电的人体或其他物体与IC管脚接触,储存于人体之中的电荷将转移到IC上,使其带电,或通过IC对地放电,这种ESD用人体放电模型来描述。该放电过程会在几百ns时间内产生数安培的瞬间放电电流,将IC内的器件烧毁。

• 硅片局部区域熔化

•PN结损伤与热破坏短路

• 扩散电阻与多晶电阻损伤(包括接触孔损伤)

•ESD可触发CMOS 集成电路内部寄生的可控硅(SCR)“闩锁”(Latch-up)效应,导致器件被过大电流烧毁。

2.潜在性失效

如果带电体的静电势或存储的静电能量较低,或ESD回路有限流电阻存在,一次 ESD 脉冲不足以引起器件发生突发性完全失效。但它会在器件内部造成轻微损伤,这种损伤又是积累性的。随着 ESD脉冲次数增加,器件的损伤阈值电压逐渐下降,器件的电参数逐渐劣化,这类失效称为潜在性失效。潜在性失效的表现形式往往是器件的使用寿命缩短,或者一个本来不会使器件损伤的小脉冲却使该器件失效。潜在性失效降低了器件抗静电的能力,降低了器件的使用可靠性。半导体器件潜在性失效主要表现为:

(a)典型I/O接口

(b)I-V曲线

图1典型I/O电路及其I-V曲线

2.1.2突发性完全失效和潜在性失效

1.突发性完全失效

突发性完全失效是器件的一个或多个电参数突然劣化,完全失去规定功能的一种失效。通常表现为开路、短路以及电参数严重漂移。

半导体器件ESD损伤失效现象主要表现为:

• 介质击穿

• 铝互连线损伤与烧熔

2.1.3静电损伤的特点

静电放电损伤未充分认识之前,人们常常将一些失效归因于早期失效或原因不明的失效。这种情况的出现是由于人们对静电放电损伤的特点缺少了解。静电放电损伤具有以下四大特点:

1.隐蔽性

人体不能直接感知静电除非发生静电放电,但是发生静电放电人体也不一定能有电击的感觉,这是因为人体能感知的静电放电电压为 2-3 KV,所以静电具有隐蔽性。

(1)栅氧化层损伤

MOS 栅氧化层受到 ESD 的作用,会产生细微损伤,有时会导致栅极泄漏电流少量增加。这种情况的发生可能是由于放电时形成丝状铝硅合金,该合金尚不能跨接整个栅氧化物,使得受损的氧化层击穿电压降低,在使用时就可能由于低能量EOS 或者 ESD 使得已经受损的氧化层击穿,从而使器件失效。栅氧化层的击穿机理,目前认为可分为两个阶段:

关键词:

静电放电 微电子器件echanismOf ESD

Abstract:

Electrostatic discharge (ESD) damage to IC(Integrated Circuit) has been paid more attention than ever. This paper introduces generation of static electricity, three kinds of ESD models and test methods, and ESD protection circuit. ESD failure mode,failure mechanism, experiment plan and results, and failure signature ofsomeESD models are discussed.

2

2.1失效模式

2.1.1失效问题

工业调查表明由ESD造成的IC失效占现场失效器件总数的50%左右,所以近年来对ESD保护问题的研究逐渐被业界所重视。

以一个典型的I/O接口电路为例,(图1(a))对输出管脚施以交流电压,测量I/V曲线,正常、短路、开路、漏电等情况均如(图1(b))所示。ESD一般会造成短路和漏电失效模式的产生。

(2)栅氧化物愈合/短路

形成的丝状铝硅合金也可能在后续的静电放电作用下被烧毁,从而使氧化栅得到“自愈”。但“自愈”的氧化栅会由于不可靠而降级,它会在后续的工作中遇到过应力或是低能量的ESD脉冲时,容易使缺陷扩大或使氧化栅发生短路。