数字电子钟设计报告,完整版.doc

数字电子钟设计报告

数字电子钟一.摘要数字电子钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。

它的计时周期为24小时,显示满刻度为23时59分59秒。

因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路和振荡器组成。

主电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态用七段显示译码器译码,通过七段显示器显示出来。

校时电路时用来对“时”、“分”、“秒”显示数字进行校对调整。

采用74160,74393实现24进制和60进制,从而实现计数功能。

目录一.正文 (3)1.1系统设计 (3)1.11设计原理(数字电子钟结构框图): (3)1.12石英晶体振荡器 (3)1.2单元电路设计 (4)1.21时、分、秒计数器的设计: (4)1.2.1.1 元器件的选择:74LS160 同步十进制计数器、与非门 (4)1.2.1.2 二十四进制计数器电路图 (5)1.2.1.3 六十进制计数器电路图 (6)1.2.1.4 秒脉冲谐振电路: (6)1.3系统的测试 (8)1.3.1 N进制级联 (8)1.3.2分频器电路 (8)1.3.3.调校电路 (9)1.4 总结 (10)参考文献 (10)附录 (11)1.元器件的明细表 (12)一.正文1.1系统设计1.11设计原理(数字电子钟结构框图):数字电子钟是一个典型的数字电路系统,其由直流稳压电源,秒脉冲发生器,时、分、秒计数器以及校时和显示电路组成结构框图如下:图表 11.12石英晶体振荡器:石英晶体振荡器的特点是振荡频率准确,电路结构简单,频率易调节。

基于PLC的数字电子钟毕业设计完整版.doc

基于PLC的数字电子钟毕业设计完整版.doc 本文是关于基于PLC的数字电子钟毕业设计完整版的介绍,下面将为大家详细阐述。

一、选题背景随着现代社会的发展,数字电子钟成为了人们生活中不可缺少的物品之一。

数字电子钟可以直观地显示时间,并且具有定时、闹钟、铃声等功能,受到了广泛的青睐。

本文选题基于PLC的数字电子钟,旨在运用数字电子技术和现代化工业控制技术,设计制作一款具有高精准度、稳定性、可靠性的数字电子钟。

二、选题目的本文选题的目的是设计制作一款基于PLC的数字电子钟,该产品具有以下优点:1、高精度计时功能:该数字电子钟采用高第二振荡器,具有秒级精度。

2、多功能组合:该数字电子钟可以实现闹钟和定时功能,并且具有3种铃声选择。

3、PLC可编程控制:采用PLC技术进行控制,可实现电子钟的编程控制和调试。

4、良好的稳定性和可靠性:数字电子钟的硬件部分采用高质量的元器件,具有良好的稳定性和可靠性。

三、技术路线本文的数字电子钟主要由显示模块、控制模块和电源模块组成。

显示模块:显示模块采用4位7段数码管,通过PLC输出控制信号,实现数字时钟的显示功能。

控制模块:控制模块采用PLC进行控制,信号处理电路通过采集各种外部信号控制数码管的显示和闹铃的启停。

另外,该数字电子钟还具有闹钟、定时等功能,可实现按键控制。

电源模块:电源模块采用变压器降压、稳压电路进行变压、稳压,以保证电子钟的正常工作。

四、设计思路1、数字显示功能的实现显示模块采用4位7段数码管,通过PLC输出控制信号,实现数字时钟的显示功能。

以公共阳极方式接线,通过PLC输出控制信号,选择要显示的数字,在输出控制信号后,使其中的1位7段数码管上显示相应的数字。

2、实现外部信号采集3、 PL C可编程控制实现功能数字电子钟的编程控制和调试可以通过PLC技术来实现,用户可根据需要编制相应的程序来实现不同的功能。

例如,对不同的闹钟周期进行设置、调整铃声大小等。

四、实验结果与分析本文设计制作的基于PLC的数字电子钟具有高精准度、稳定性、可靠性等优点,通过实验测定,数字电子钟的时钟计时误差在1s以内,稳定性好,可靠性高,其功能实现较为完善。

课程设计_数字电子钟设计报告 -终

数字闹钟设计报告目录1. 设计任务与要求 (2)2. 设计报告内容2.1实验名称 (2)2.2实验仪器及主要器件 (2)2.3实验基本原理 (3)2.4数字闹钟单元电路设计、参数计算和器件选择…………………………3-72.5数字闹钟电路图 (8)2.6数字闹钟的调试方法与过程 (8)2.7设计与调试过程的问题解决方案 (8)3.实验心得体会……………………………………………………………………9、101. 设计任务与要求数字闹钟的具体设计任务及要求如下:(1) 有“时”、“分”十进制显示, “秒”使用发光二极管闪烁表示。

(2) 以24小时为一个计时周期。

(3) 走时过程中能按预设的定时时间(精确到小时)启动闹钟, 以发光二极管闪烁表示, 启闹时间为3s~10s。

2. 设计报告内容2.1实验名称数字闹钟2.2实验仪器及主要器件(1)CD4511( 4片)、数码管(4片)(2)74LS00(6片)(3)74LS138(2片)(4)74LS163(6片)(5)LM555(1片)(6)电阻、电容、导线等(若干)(7)面包板(2片)、示波器等2.3数字闹钟基本原理要想构成数字闹钟, 首先应选择一个标准时间源——即秒信号发生器。

可以采用LM555构成多谐振荡器, 通过改变电阻来实现频率的变化, 使之产生1HZ的信号。

计时的规律是: 60秒=1分, 60分=1小时, 24小时=1天, 就需要对计数器分别设计为60进制和24进制的, 并发出驱动信号。

各计数器输出信号经译码器到数字显示器, 按“时”、“分”顺序将数字显示出来, 秒信号可以通过数码管边角的点来显示。

数字闹钟要求有定时响闹的功能, 故需要提供设定闹时电路和对比起闹电路。

设时电路应共享译码器到数字显示器, 以便使用者设定时间, 并可减少电路的芯片数量;而对比起闹电路提供声源, 应具有人工止闹功能, 止闹后不再重新操作, 将不再发生起闹等功能。

数字电子钟的逻辑框图如图所示。

电子数字时钟课程设计报告(数电)

电子数字时钟课程设计报告(数电)第一篇:电子数字时钟课程设计报告(数电)数字电子钟的设计1.设计目的数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

因此,我们此次设计数字钟就是为了了解数字钟的原理,从而学会制作数字钟。

而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。

且由于数字钟包括组合逻辑电路和时叙电路。

通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。

1.1设计指标1.时间以12小时为一个周期;2.显示时、分、秒;3.具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间; 1.2 设计要求1、电路设计原理说明2、硬件电路设计(要求画出电路原理图及说明)3、实物制作:完成的系统能达到题目的要求。

4、完成3000字的课程设计报告2.功能原理2.1 数字钟的基本原理数字电子钟由信号发生器、“时、分、秒”计数器、LED数码管、校时电路、整点报时电路等组成。

工作原理为时钟源用以产生稳定的脉冲信号,作为数字种的时间基准,要求震荡频率为1HZ,为标准秒脉冲。

将标准秒脉冲信号送入“秒计数器”,该计数器采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计数器,可以实现24小时的累计。

LED数码管将“时、分、秒”计数器的输出状态显示。

校时电路是来对“时、分、秒”显示数字进行校对调整。

2.2 原理框图3.功能模块3.1 振荡电路多谐振荡器也称无稳态触发器,它没有稳定状态,同时无需外加触发脉冲,就能输出一定频率的矩形波形(自激振荡)。

数字电子钟设计报告,完整版

一、任务技术指标设计一个数字电子钟(1)能显示小时、分钟和秒;(2)能进行24小时和12小时转换;(3)具有小时和分钟的校时功能。

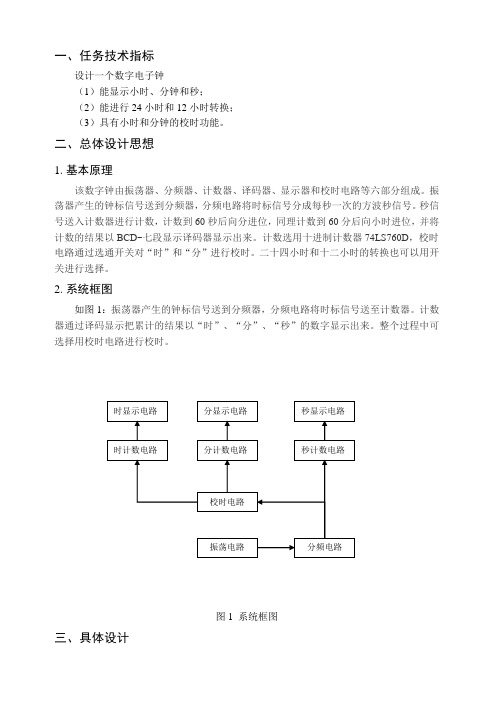

二、总体设计思想1.基本原理该数字钟由振荡器、分频器、计数器、译码器、显示器和校时电路等六部分组成。

振荡器产生的钟标信号送到分频器,分频电路将时标信号分成每秒一次的方波秒信号。

秒信号送入计数器进行计数,计数到60秒后向分进位,同理计数到60分后向小时进位,并将计数的结果以BCD-七段显示译码器显示出来。

计数选用十进制计数器74LS760D,校时电路通过选通开关对“时”和“分”进行校时。

二十四小时和十二小时的转换也可以用开关进行选择。

2.系统框图如图1:振荡器产生的钟标信号送到分频器,分频电路将时标信号送至计数器。

计数器通过译码显示把累计的结果以“时”、“分”、“秒”的数字显示出来。

整个过程中可选择用校时电路进行校时。

图1 系统框图三、具体设计1.总体设计电路该数字钟由振荡器、分频器、计数器、显示器和校时电路组成。

振荡器产生的钟标信号送到分频器,分频电路将时标信号分成每秒一次的方波秒信号。

秒信号送入计数器进行计数,计数到60秒后向分进位,同理分计数器计数到60分后向小时进位,并将计数的结果以BCD-七段显示译码器显示出来。

计数选用十进制计数器74LS760D,校时电路通过选通开关对“时”和“分”进行校时。

二十四小时和十二小时的转换可以用开关进行选择。

图2 总体电路图2.模块设计(1)振荡器的设计振荡器是数字钟的核心。

振荡器的稳定度及频率的精确度决定了数字钟计时的准确程度,通常选用石英晶体构成振荡器电路。

石英晶体振荡器的作用是产生时间标准信号。

因此,一般采用石英晶体振荡器经过分频得到这一时间脉冲信号。

电路中采用的是将石英晶体与对称式多谐振荡器中的耦合电容串联起来,就组成了如图3所示石英晶体多谐振荡器。

图3振荡器电路图和仿真波形图(2)分频器的设计对于分频器的设计选定74LS90集成芯片。

数字钟的设计报告完整版

电子技术课程设计(数电部分)——简易数字钟专业____________姓名____________班级____________学号____________二〇一三年四月基于EDA的简易数字钟设计第一章设计背景与要求 (1)一.设计背景 (1)二.设计要求 (1)第二章系统概述 (1)2.1设计思想与方案选择 (1)2.2各功能块的组成 (2)第三章单元电路设计与分析 (2)3.1各单元电路的选择 (2)3.2基本计时电路子模块的设计及工作原理分析 (3)(1)脉冲发生电路(分频模块) (3)(2)60进制计数器模块 (5)(3)24进制计数器模块 (6)(4)两片60进制计数器和一片24进制计数器联级构成24小时电路 (8)3.3外围子模块电路的设计及工作原理分析 (9)(1)4位显示译码模块 (9)(2)整点报时电路原理及模块设计 (12)(3)校正开关及脉冲按键消抖动处理模块 (14)(4)12小时制与24小时制的切换电路 (15)第四章电路的调试过程 (19)4.1遇到的主要问题 (19)4.2现象原因分析及解决措施及效果 (19)4.3功能的测试方法、步骤,记录的数据 (20)第五章结束语 (20)5.1对设计题目的结论性意见及进一步改进的意向说明 (20)5.2总结设计的收获与体会 (21)参考文献: (21)第一章设计背景与要求一.设计背景在公共场所,例如车站、码头,准确的时间显得特别重要,否则很有可能给外出办事即旅行袋来麻烦。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确度和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。

数字钟是一种典型的数字电路,包括了组合逻辑电路和时序电路。

二.设计要求设计一个简易数字钟,具有整点报时和校时功能。

(1)以四位LED数码管显示时、分,时为二十四进制。

(2)时、分显示数字之间以小数点间隔,小数点以1Hz频率、50%占空比的亮、灭规律表示秒计时。

数字电子钟设计实训报告

数字电子钟的设计【摘要】本系统由晶体振荡器、分频器、计数器、译码器、七段译码显示器和校准、报时电路组成,采用了CMOS或TTL系列(双列直插式)中小规模集成芯片。

总体方案设计由主体电路和扩展电路两大部分组成。

其中主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能,进行了各单元电路设计,总体安装、制作及调试。

数字钟是一种计时装置,不仅能替代指针式钟表,还可以运用到定时控制、自动计时及时间程序控制等方面,应用广泛。

【关键词】石英晶振、分频器、计数器、译码器、七段译码显示器、校准、整点报时。

第一章数字电子钟总体方案1.1数字电子钟总体方案的确定数字电子钟组成一般由振荡器、分频器、计数器、译码器及显示器等几部分组成。

石英振荡器产生的时标信号送到分频器,分频电路将时标信号分成秒脉冲,秒脉冲送入计数器进行计数,并把累计结果以“时”、“分”、“秒”的数字显示出来。

“秒”的显示由两级计数器和译码器组成的六十进制计数器电路实现,“分“的显示电路与“秒”相同。

“时”的显示由两极计数器和译码器组成的二十四进制计数器电路实现。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态0进行七段显示译码器译码,通过六位七段译码显示器显示出来。

整点报时电路根据计时系统的输出状态产生一脉冲信号,然后去触发一音频发生器实现报时。

校时电路时用来对“时”、“分”显示数字进行校对调整的。

数字电子钟总体方案框图图1.1.1 数字电子钟组成框图1.2数字电子钟电路组成数字电子钟组成一般由振荡器、分频器、计数器、译码器及七段译码显示器等几部分组成(如图1.2.1所示)。

课程设计_数字电子钟设计报告

课程设计_数字电子钟设计报告第一篇:课程设计_数字电子钟设计报告数字电子钟设计报告数字电子钟设计报告目录1.实验目的 (2)2.实验题目描述和要求 (2)3.设计报告内容...........................................................................2 3.1实验名称.................................................................................2 3.2实验目的.................................................................................2 3.3实验器材及主要器件..................................................................2 3.4数字电子钟基本原理..................................................................3 3.5数字电子钟单元电路设计、参数计算和器件选择..............................3-8 3.6数字电子钟电路图.....................................................................9 3.7数字电子钟的组装与调试............................................................9 4.实验结论.................................................................................9 5.实验心得 (10)参考文献 (10)数字电子钟设计报告一简述数字电子钟是一种用数字显示秒,分,时,日的计时装置,与传统的机械相比,它具有走时准确,显示直观,无机械传动装置等优点,因而得到了广泛的应用:小到人们日常生活中的电子手表,大到车站,码头,机场等公共场所的大型数显电子钟。

数字电子钟设计报告

数字电子钟设计报告摘要摘要:本系统采用小规模集成电路构成数字钟的硬件电路,由晶体振荡器产生脉冲,经过CD4060和双D触发器构成的T’触发器进行分频,利用74LS161作为计数器,显示器采用共阴极七段数码管。

配合显示译码器74LS248来显示计数器输出的数字。

本系统还有校时功能,通过经整形的尖脉冲对秒位、分位、时位进行校时。

最后用电路仿真软件protel dxp绘制出数字钟的完整电路图。

对数字电路的学习起到了良好的辅助作用。

关键词:数字钟、晶振器、分频器、计数器、译码器、显示器The system uses small-scale integrated circuit hardware constitutes digital clock, crystal oscillator generated by the pulse, through the CD4060, and dual D flip-flop composed of T 'flip-flops for frequency division, using 74LS161 as a counter, using common cathode seven-segment digital display tube. Decoder 74LS248 with the show to display the output of the digital counter. The system also features school hours, through the plastic of the sharp pulse of the second place points position, when the bit for the campus. Finally, circuit simulation software protel dxp draw a complete circuit digital clock. The study of digital circuits played a good supporting role.Keywords: digital clock, crystal oscillators, frequency divider, counter, decoder, display目录第一章概论 (1)1.1 数字电子钟电路设计的任务及要求 (1)1.2 设计思想与方案论证 (4)第二章选用硬件单元介绍 (5)2.1 集成电路CD4060简介 (5)2.2 共阴显示器LC5011-11简介 (6)2.3 集成电路74LS248简介 (6)2.4 集成电路74LS161简介 (7)2.5 集成电路74LS00简介 (8)第三章组成电路设计介绍 (8)3.1 秒脉冲发生器电路设计 (9)3.2 时、分、秒计数电路设计 (9)3.3 译码显示电路设计 (10)3.4 校时电路设计 (11)3.5 电路原理图 (11)3.6 电路连接图 (12)第四章焊接与调试 (12)4.1 焊接步骤 (12)4.2 调试方法 (13)4.3调试中出现的问题、原因分析及解决方法 (13)附录电路器材选用列表 (13)成果图 (14)个人心得 (15)第一章概论数字电子钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。

电子数字钟的设计报告

电子数字钟作者:王克翔王尔锋张伟余晓旭指导老师:任玲芝目录摘要 (2)1. 系统总图如下图所示 (3)2.方案设计 (3)2.1.控制模块 (3)2.2. 显示模块 (4)2.3. 电源模块 (4)3.软件设计 (5)4.系统误差测试 (6)5. 功能说明书 (6)6. 总结 (7)7. 参考文献 (7)附录一电子钟实际工作原图 (7)附录二元器件清单 (8)附录三软件实现程序 (9)摘要本设计是基于80C52单片机芯片软件控制功能而设计的电子数字钟。

本数字钟不但具有可调性好、准确度高等优点,而且是采用二十四小时制的计时方式。

本数字钟可以同时看到时钟、分钟、秒钟让人们更加准确的掌握时间,还添加整点提示、计时、计数功能等功能。

更为重要的本数字钟可塑性好,可以更改其计时方式和其它功能。

关键词:80C52 精确可塑性Abstract一.系统总图如下图所示:我们采用了比较成熟的80C52单片机控制数码管显示时间,其中数码管可以同时显示时钟、分钟、秒钟。

二.方案设计1. 控制模块方案一:直接采用数字电路控制时钟变化,其优点:电路简单、成本低。

但是它主要的缺点:时间误差较大、而且可塑性较差、无扩展。

方案二:我们采用的是比较成熟的ATMEL公司80C52单片机控制数码管显示时间,其中数码管可以同时显示时钟、分钟、秒钟。

我们设计的数字电子钟最要的优势就是精确度比较高、而且可塑性比较强、有扩展功能、价格便宜。

例如:整点音乐报时、可以作为计时器、计数器。

根据反复比较我们选择第二种方案。

2. 显示模块:方案一:采用单个数码管其优点:便宜。

缺点:焊接、连线比较麻烦。

方案二:采用连体的数码管优点:便宜、焊接、美观、连线方便。

经过比较我们选择第二种方案。

3. 电源模块:方案一::铅酸电池供电,优点电流大,缺点重量太沉。

方案二:电池组供电,可提供稳定电流,重量很轻。

经过比较我们选择方案二因为我们可以用一组三节干电池提供大概4.5V的电压而且比较稳定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、任务技术指标

设计一个数字电子钟

(1)能显示小时、分钟和秒;

(2)能进行24小时和12小时转换;

(3)具有小时和分钟的校时功能。

二、总体设计思想

1.基本原理

该数字钟由振荡器、分频器、计数器、译码器、显示器和校时电路等六部分组成。

振荡器产生的钟标信号送到分频器,分频电路将时标信号分成每秒一次的方波秒信号。

秒信号送入计数器进行计数,计数到60秒后向分进位,同理计数到60分后向小时进位,并将计数的结果以BCD-七段显示译码器显示出来。

计数选用十进制计数器74LS760D,校时电路通过选通开关对“时”和“分”进行校时。

二十四小时和十二小时的转换也可以用开关进行选择。

2.系统框图

如图1:振荡器产生的钟标信号送到分频器,分频电路将时标信号送至计数器。

计数器通过译码显示把累计的结果以“时”、“分”、“秒”的数字显示出来。

整个过程中可选择用校时电路进行校时。

图1 系统框图

三、具体设计

1.总体设计电路

该数字钟由振荡器、分频器、计数器、显示器和校时电路组成。

振荡器产生的钟标信号送到分频器,分频电路将时标信号分成每秒一次的方波秒信号。

秒信号送入计数器进行计数,计数到60秒后向分进位,同理分计数器计数到60分后向小时进位,并将计数的结果以BCD-七段显示译码器显示出来。

计数选用十进制计数器74LS760D,校时电路通过选通开关对“时”和“分”进行校时。

二十四小时和十二小时的转换可以用开关进行选择。

图2 总体电路图

2.模块设计

(1)振荡器的设计

振荡器是数字钟的核心。

振荡器的稳定度及频率的精确度决定了数字钟计时的准确程度,通常选用石英晶体构成振荡器电路。

石英晶体振荡器的作用是产生时间标准信号。

因此,一般采用石英晶体振荡器经过分频得到这一时间脉冲信号。

电路中采用的是将石英晶体与对称式多谐振荡器中的耦合电容串联起来,就组成了如图3所示石英晶体多谐振荡器。

图3振荡器电路图和仿真波形图

(2)分频器的设计

对于分频器的设计选定74LS90集成芯片。

74LS90本身就是一个2分频和5分频的

十进制计数器,自身可连成一个十个频的分频器。

控制端接地,电路进入计数状态。

将3片74LS90串接就可将振荡器的1KHZ转变为1HZ。

分频电路的仿真图如下:

图4分频器电路图和仿真波形图

(3)分计数器和秒计数器的设计

分计数器和秒计数器相同都是六十进制计数器。

选用教材中介绍过的中规模集成

74LS160十进制计数器。

接法是采用置数法将两片74LS160进行串行进位方式的连接。

图5秒计数器设计电路图

图6分计数器设计电路图

(4)时计数器的设计及安装

时计数器是24进制计数器。

实现这个计数器仍采用两片中规模集成计数器74LS160。

集成芯片的连接仍按串行进位方式进行。

任务要求能进行二十四进制和十二进制转换,所以利用一个开关进行切换。

图7十二进制时计数器设计电路图

图8二十四进制时计数器设计电路图

(5)译码显示电路

译码电路的功能是将“秒”“分”“时”计数器的输出代码进行编译,变成相应的数字。

选用BCD-七段显示译码器显示可减少译码器件的使用。

图9译码显示电路图

(6)校时电路

当时钟指示不准或停摆时,就需要校准时间。

如图,分计时器的校时电路由5个与非门构成,其中U4和U5构成了一个最简单的RS触发器。

U2的另一端接入秒的进位信号,U3的另一端接入秒信号也就是时标信号。

当S1接高电位,S2接地时,U4输出低电位,秒的进位信号有校,电路正常工作。

当S1接地S2接电源时U5输出低电位,秒信号有效,分的计数器进入快速计时状态,此时校分。

时计时器的校时同分计时器的校时相同,如下图所示。

图10校时电路图

3.仿真及仿真结果分析

图11 仿真结果电路图

电路运行后秒显示器开始计时,满60秒后进位至分,满60分后进位至时,通过开关可以进行二十四进制和十二进制的时钟显示转换,选通校时电路时可以通过开关分别对分和秒校时,因此仿真成功。

四、结论

在此次的数字钟设计过程中,更进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法,也在运用Protel软件的基础上学习了对Multisim10的使用。

使我对已学过的电路、数电、模电等电子技术的知识有了更深一步的了解,锻炼和培养了自己利用已学知识来分析和解决实际问题的能力。

对自己以后的学习和工作有很大的帮助。

刚开始做这个设计的时候感觉自己什么都不知道怎么下手,脑子里比较浮躁和零乱。

但通过一段时间的努力,通过重温数电,模电等电子技术的书籍,还有通过查看相关的设计技术以及一些参考文献,在老师的指导和周围同学的帮助下,使我对自己的设计大致上有了一个思路,再通过对各个模块的分别设计,最终设计出来这个电子钟。

通过不断的查阅期刊杂志和从网络上搜集资料,这次设计更让我熟悉了一些常用集成逻辑电路和其相应芯片的使用。

这个课程设计我发现了我好多知识都不熟悉甚至有的东西我根本就不知道,这让我感到了要学习的东西还有很多很多。

因此我认为作为电子信息工程专业的学生,我们不仅要从基本的电路设计学起,不断了解专业前沿的知识,利用各种资源来丰富充实自己的专业知识,还要有遇到困难不妥协的精神。

参考资料

[1]阎石.数字电子技术基础[M].北京:高等教育出版社,2001.

[2]彭介华.电子技术课程设计指导[M].北京:高等教育出版社,1997.

[3]孙梅生.电子技术基础课程设计[M].北京:高等教育出版社,1998.

[4]高吉祥.电子技术基础实验与课程设计[M].北京:电子工业出版社,2002.。