《计算机体系结构》第四次实验 Tomasulo方法实验

计算机体系结构试卷试题(答案全)

一填空题(每空1分,共30分)1、系列机是指具有相同的体系结构,但具有不同组织和实现的一系列不同型号的机器。

2、存储程序计算机结构上的主要特点之一是以运算器为中心。

3、从计算机系统结构的多级层次结构可知,通常情况下,第1、2、3级用解释方法实现,第4或更高级用翻译方法实现。

4、对于最常见的事件,通常赋予它优先的处理权和资源使用权,这是计算机体系结构设计中的大概率事件优先原则。

5、容量为64块的Cache采用组相联方式映像,字块大小为128字节,每4块为一组,若主存容量为4096块,且以字编址,那么主存地址为 19 位,主存区号为 6 位。

6、可改进比例的值总是小于等于1 。

7、一般有两种策略来保存寄存器的内容,即:调用者保存和被调用者保存。

8、DLX指令集提供了立即数寻址、寄存器寻址、偏移寻址和寄存器间接寻址4种寻址方式。

9、对某流水线处理器测试时发现其存在结构冲突,通常可采用资源重复和流水化功能单元方法解决该问题。

10、编译器通过重新组织代码顺序消除暂停的技术被称为指令调度。

11、按照流水的级别可以把流水线分为部件级流水线、处理机级流水线和处理机间流水线。

12、为解决流水线使用非流水数据通路的寄存器引起冲突,在流水线设计中采用寄存器文件技术解决该问题。

13、Cache的替换算法常见的有 FIFO 、LRU 和随机法。

14、改进Cache性能的方法主要有降低失效率、减少失效开销和减少Cache命中时间。

15、减少流水线处理分支暂停时钟周期数的途径包括尽早判断分支转移是否成功和尽早计算出分支成功转移的PC值。

二、选择题(1—15题,每题1分,共15分)1、下面的指令中, A 不属于RISC处理器指令集。

A.ADD R4,[1000] B.LD R3,(R4) C.SUB R4,R3 D.SD 0(R3),R42. 在其它部件性能保持不变的情况下,对CPU性能的不断改进并没有获得期望的结果,这主要是受到了 A 的影响。

计算机体系结构量化研究方法英文版第四版教学设计 (3)

Teaching Design for Quantitative Research Methods in Computer Architecture, 4th Edition IntroductionComputer architecture is the study of the design and organization of computer systems. As the field has evolved, so too have the tools and techniques used for research in computer architecture. This document outlines a teaching design for the fourth edition of the book Quantitative Research Methods in Computer Architecture, which provides an overview of the quantitative research methods most commonly used in the field.ObjectivesThe objectives of this teaching design are:1.To provide an overview of the fundamental concepts andprinciples of quantitative research methods in computerarchitecture.2.To enable students to design and perform experiments usingappropriate research methods.3.To help students develop critical thinking skills toevaluate research findings.Course OutlineThe course is divided into the following chapters:1.Introduction to Quantitative Research Methods in ComputerArchitecture2.Research Design and Experimental Design3.Sampling4.Measurement5.Data Analysis and Statistics6.Reporting Research FindingsChapter 1: Introduction to Quantitative Research Methods in Computer ArchitectureThis chapter provides an introduction to the course. It introduces the terminology and concepts commonly used in quantitative research, and the reasons for using quantitative research methods in computer architecture. It also reviews the different kinds of research questions that can be addressed using quantitative methods.Chapter 2: Research Design and Experimental DesignIn this chapter, students will learn about research design and experimental design. This chapter will cover topics such as identifying research questions, choosing experimental units, selecting the appropriate type of design, and choosing an experimental group and control group.Chapter 3: SamplingThis chapter covers the topic of sampling. Students will learn about different types of sampling methods, including random, stratified, and systematic sampling, and how to choose the appropriate sampling method based on their research questions.Chapter 4: MeasurementIn this chapter, students will learn about measurement and the different types of measurement scales used in quantitative research. They will also learn about the criteria for selecting appropriate measures and techniques for measuring different aspects of computer architecture.Chapter 5: Data Analysis and StatisticsIn this chapter, students will learn about data analysis and statistics. They will learn how to use statistical software to analyze data, conduct descriptive statistics, and use inferential statistics to test hypotheses.Chapter 6: Reporting Research FindingsThe final chapter of the course focuses on reporting research findings. Students will learn how to prepare reports, present findings to different audiences, and deal with ethical issues related to reporting research.Course RequirementsStudents will need to:1.Attend all lectures and participate in class discussions.plete all assigned readings before class.3.Participate in group discussions and group assignments.4.Write a final research paper on a topic related to thecourse.ConclusionThis teaching design provides a comprehensive overview of the quantitative research methods commonly used in computer architecture. Through this course, students will learn the theory and practical skills necessary to design and perform experiments using appropriate research methods. By the end of the course, students will be able to interpret, analyze, and report on research findings in a clear and concise manner.。

2022年北京航空航天大学计算机科学与技术专业《计算机系统结构》科目期末试卷B(有答案)

2022年北京航空航天大学计算机科学与技术专业《计算机系统结构》科目期末试卷B(有答案)一、选择题1、IBM360/91对指令中断的处理方法是()A.不精确断点法B.精确断点法C.指令复执法D.对流水线重新调度2、下列说法正确的是()A."一次重叠"是一次解释一条指令B."一次重叠"是同时解释相邻两条指令C.流水方式是同时只能解释两条指令D."一次重叠"是同时可解释很多条指令3、在系统结构设计中,提高软件功能实现的比例会( )。

A.提高解题速度B.减少需要的存贮容量C.提高系统的灵活性D.提高系统的性能价格比4、若输入流水线的指令既无局部性相关,也不存在全局性相关,则()。

A.可获得高的吞吐率和效率B.流水线的效率和吞吐率恶化C.出现瓶颈D.可靠性提高5、不同系列的机器之间,实现软件移植的途径不包括( )A.用统一的高级语言B.用统一的汇编语言C.模拟D.仿真6、"从中间开始"设计的"中间"目前多数是在( )。

A.传统机器语言级与操作系统机器级之间B.传统机器语言级与微程序机器级之间C.微程序机器级与汇编语言机器级之间D.操作系统机器级与汇编语言机器级之间7、直接执行微指令的是( )A.汇编程序B.编译程序C.硬件D.微指令程序8、浮点数尾数基值rm=8,尾数数值部分长6位,可表示的规格化最小正尾数为( )A.0.5B.0.25C.0.125D.1/649、在多用户机器上,应用程序员不能使用的指令是()A.“执行”指令B.“访管”指令C.“启动IO”指令D“测试与置定”指令10、浮点数尾数下溢处理时,最大误差最大,但下溢处理不需要时间,平均误差又趋于0的方法是( )。

A.截断法B.舍入法C.ROM查表法D.恒置"1"法11、对机器语言程序员透明的是( )。

A.中断字B.主存地址寄存器C.通用寄存器D.条件码12、下列关于标量流水机的说法不正确的是()A.可对标量数据进行流水处理B.没有向量数据表示C.不能对向量数据进行运算D.可以对向量、数组进行运算13、下列说法正确的是( )A.Cache容量一般不大,命中率不会很高B.Cache芯片速度一般比CPU的速度慢数十倍C.Cache本身速度很快。

《计算机体系结构》教学大纲

《计算机体系结构》教学大纲英文名称:Computer Architecture预修课程:计算机原理、数据结构、操作系统、编译原理、高级语言总学时数:45学时,其中讲授36学时,课内实验4学时。

学分:2.5教学对象:计算机科学与技术专业本科学员开课学期:第6学期一、课程的性质、地位和任务该课程是计算机专业一门非常重要的专业基础课。

课程系统介绍进行计算机系统设计所必须了解与掌握的专业知识,重点介绍计算机体系结构的基本思想、基本概念、设计原理、设计方法与评价分析方法。

本课程内容广、概念多、系统性强、实例多,涉及计算机体系结构技术领域前沿。

本课程的任务是要使学生能够系统全面正确理解和掌握计算机体系结构技术的基本思想,并培养学生按照定量分析的方法初步设计和评价计算机系统的能力。

二、教学内容和要求(一)计算机体系结构基础内容和要求:了解计算机系统设计的基本任务;了解计算机技术发展的趋势;了解计算机性能与成本的影响因素,以及性能的评价方法,掌握计算机体系结构基本概念和定量分析方法的基本原理。

重点:计算机设计的基本任务,计算机体系结构基本概念,定量分析方法基本原理(二)计算机指令集结构设计内容和要求:从计算机系统指令集结构设计出发了解典型指令集结构的技术特点及其发展,掌握计算机系统指令集结构的设计方法以及各种设计方案的优缺点;掌握一种RISC指令集结构实例。

重点:计算机系统指令集结构设计,RISC指令集结构实例(三)流水线技术内容和要求:掌握流水线技术的基本原理及其性能评价方法;掌握RISC指令集结构流水线的基本设计方法,并能够从数据相关与控制相关两个方面分析流水线性能,掌握提高流水线性能的软硬件方法。

掌握向量处理机原理;了解基本的向量处理机结构;掌握向量处理机性能改善和评价的基本方法。

重点:流水线的基本原理与设计、分析评价方法、向量处理机原理(四)指令级并行内容和要求:掌握指令级并行的基本概念、指令的动态调度技术,理解控制相关的动态解决技术,掌握多指令流出技术的基本原理。

tomasulo算法例题详解

tomasulo算法例题详解Tomasulo算法例题详解什么是Tomasulo算法?Tomasulo算法是一种用于计算机处理器中的动态调度算法,通过并行执行指令来提高处理器的效率。

它主要包含三个组成部分:寄存器重命名、数据缓冲器和指令调度。

寄存器重命名寄存器重命名是Tomasulo算法的关键步骤之一,它的目的是解决数据相关性问题,提高指令的并行执行能力。

通过给每个指令生成一个唯一的标记,并将其保存到重命名表中,可以实现在不同指令之间共享相同的寄存器。

这样就能够避免指令间的数据相关性,提高程序的并行度。

数据缓冲器数据缓冲器是Tomasulo算法的重要组成部分,它用于存储指令执行过程中需要的操作数和计算结果。

缓冲器使用队列的形式进行管理,可以实现指令的乱序执行。

通过缓存器重新排序指令的执行顺序,可以更高效地利用处理器的资源,提高指令的执行效率。

指令调度指令调度是Tomasulo算法的最后一步,它用于确定指令的执行顺序。

通过优化指令的调度顺序,可以最大程度地减少指令之间的冲突,并提高程序的并行度。

调度器根据指令的执行状态和数据依赖关系,动态地调整指令的执行顺序,从而提高程序的性能。

例题下面通过一个例题来说明Tomasulo算法的应用:1.ADD F4, F2, F62.MUL F8, F4, F23.SUB F6, F4, F104.DIV F12, F6, F85.ADD F2, F4, F6首先,我们需要将指令分解成操作码和操作数,并构建重命名表和数据缓冲器。

然后按照Tomasulo算法的步骤依次执行指令。

1.重命名寄存器:重命名F4为Qi,将ADD指令写入缓冲器。

2.执行ADD指令:将F2和F6的值从缓冲器中读取,并将结果保存到缓冲器中,同时将结果写回寄存器。

3.重命名寄存器:重命名F8为Qj,将MUL指令写入缓冲器。

4.等待ADD指令完成:MUL指令需要等待ADD指令的结果,因此暂时无法执行。

西安邮电大学体系结构Tomasulo算法实验报告

实验4 Tomasulo算法1 实验目的(1)加深对指令级并行性及开发的理解。

(2)加深对Tomasulo算法的理解。

(3)掌握Tomasulo算法在指令流出、执行、写结果各阶段对浮点操作指令以及load和store指令进行了什么处理。

(4)掌握采用了Tomasulo算法的浮点处理部件的结构。

(5)掌握保留站的结构。

(6)给定被执行的程序片段,对于具体某个时钟周期,能够写出保留站、指令状态表以及浮点寄存器状态表内容的变化情况。

2 实验平台采用Tomasulo算法模拟器。

3 实验内容和步骤首先要掌握Tomasulo算法模拟器的使用方法(见随附的ppt)。

1)、假设浮点功能部件的延迟时间为:加减法2个时钟周期,乘法10个时钟周期,除法40个时钟周期,Load部件2个时钟周期。

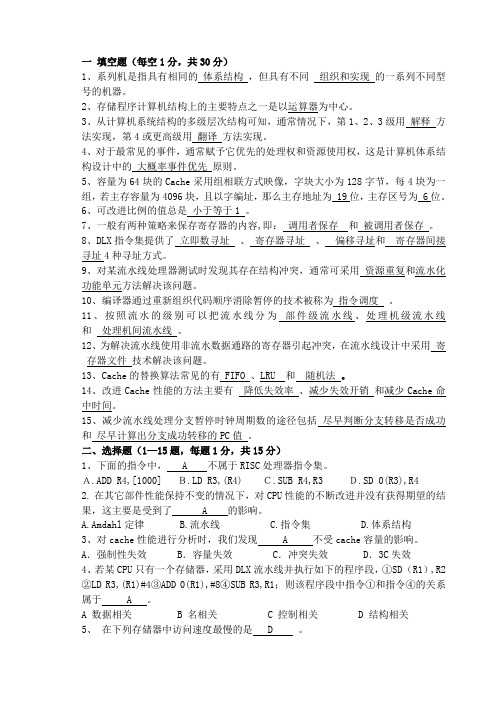

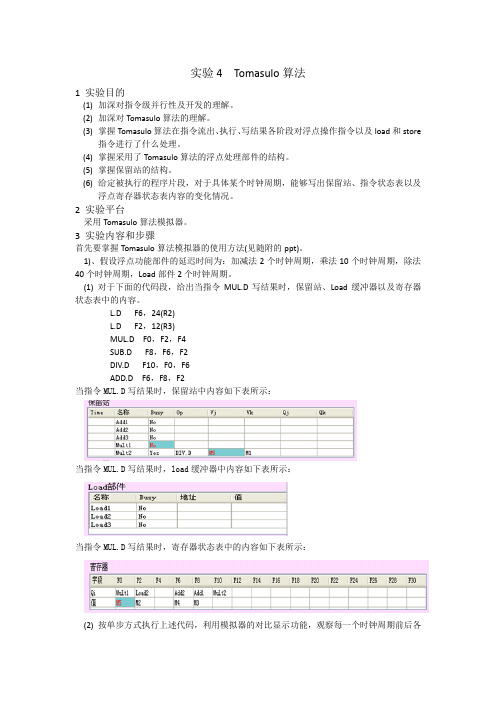

(1) 对于下面的代码段,给出当指令MUL.D写结果时,保留站、Load缓冲器以及寄存器状态表中的内容。

L.D F6,24(R2)L.D F2,12(R3)MUL.D F0,F2,F4SUB.D F8,F6,F2DIV.D F10,F0,F6ADD.D F6,F8,F2当指令MUL.D写结果时,保留站中内容如下表所示:当指令MUL.D写结果时,load缓冲器中内容如下表所示:当指令MUL.D写结果时,寄存器状态表中的内容如下表所示:(2) 按单步方式执行上述代码,利用模拟器的对比显示功能,观察每一个时钟周期前后各信息表中内容的变化情况。

观察分析:周期1:取出第一条指令L.D F6, 24(R2),地址偏移量24写入LOAD1,LOAD1名存入寄F6。

周期2:取出第二条指令L.D F2, 12(R3),地址偏移量12写入LOAD2,LOAD2名存入寄器F2,同时第一条指令开始执行,LOAD1上写入绝对地址。

周期3:取出第三条指令MUL.D F0, F2,F4,第一条指令完成,第二条指令开始执行,LOAD2上写入绝对地址。

保留站中存入待运算的操作数和操作。

《计算机体系结构》第四次实验tomasulo方法实验

《计算机体系结构》第四次实验T o m a s u l o方法实验-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KIITomasulo方法实验姓名:王宇航学号:09283020Tomasul o方法实验一、实验目的:通过本实验,理解指令流水化过程中乱序执行和寄存器重命名方法。

二、实验内容:1、用dlxView模拟器或Tomasulo算法模拟器执行浮点指令程序段。

2、指出指令乱序执行和寄存器重命名过程。

三、实验环境操作系统:Windows 7 旗舰版处理器:Intel(R) Core(TM) i3 双核内存:软件:Tomasulo算法模拟器四、实验过程:1、设置Tomasulo算法模拟器参数其中Load部件的执行时间不能设置为1,至少为2,故不作修改;加/减法部件的执行时间为4个时钟周期,乘法部件的执行时间为7个时钟周期,除法部件的执行时间为15个时钟周期。

2、分析Tomasulo算法模拟器中指令乱序执行过程Tomasulo算法模拟器中默认设置的指令下图所示:执行该指令序列,重点观察指令状态的写结果一栏,便会发现执行过程中存在乱序执行现象,共有两处乱序执行,分别如下列图所示:图中显示,在第10周期时,位于指令之后的指令经过4个周期已经执行完成并已经将结果写回寄存器,而指令仍在执行中。

在第13周期时,指令经过7个周期执行完毕,才将结果写回。

此外,还可以看到,位于指令之后的指令在第11周期时就已经开始执行,而指令直至现在都未开始执行。

在第15周期时,指令经过4个周期执行完毕,先于指令写回结果;而指令仍在执行中。

在第29周期时,指令经过15个周期终于执行完毕,将结果写回寄存器。

以上分析证明,在Tomasulo算法中存在乱序执行并且不会影响执行结果的正确性。

这是因为,Tomasulo算法采用分布的保留站,冲突检测和指令执行控制是分布的。

3、分析Tomasulo算法模拟器中寄存器重命名过程在Tomasulo算法中通过寄存器重命名来消除WAR冲突,这一过程是通过保留站来完成的。

计算机体系结构综合习题

计算机体系结构习题一、名词解释第一章:计算机组成:指的是计算机系统结构的逻辑实现,包含物理机器中的数据流和控制流的组成以及逻辑设计等。

它着眼于物理机器级内各事物的排序方式与控制方式、各部件的功能以及各部件之间的联系。

计算机实现:指的是计算机组成的物理实现,包括处理机、主存等部件的物理结构,器件的集成度和速度,模块、插件、底板的划分与连接,信号传输,电源、冷却及整机装配技术等。

它着眼于器件技术和微组装技术,其中器件技术在实现技术中起主导作用。

程序的局部性原理:指程序执行时所访问的存储器地址不是随机分布的,而是相对簇聚。

常用的经验规则:程序执行时间的90%都是在执行程序中的10%的代码。

数据访问也具有局部性。

第二章:RISC:即精简指令集计算机,它是尽可能地把指令系统简化,不仅指令的条数少,而且指令的功能比较简单。

(P36页)CISC:即复杂指令集计算机,它是增强指令功能,把越来越多的功能交由硬件实现,指令的数量也越来越多。

(P36页)寻址方式:指指令系统中如何形成所要访问的数据的地址。

第三章:流水线技术:(P53页)把一个重复的过程分解为若干个子过程(相当于上面的工序),每个子过程由专门的功能部件来实现,把多个处理过程在时间上错开,依次通过各功能段,这样,每个子过程就可以与其他的子过程并行进行,这就是流水线技术。

线性流水线:(见P57页)线性流水线是指各段串行连接、没有反馈回路的流水线。

数据通过流水线中的各段时,每个段最多只流过一次。

非线性流水线:(见P57页)非线性流水线是指各段除了有串行的连接外,还有反馈回路的流水线。

数据相关:(见P73页)考虑两条指令i和j,i在j的前面,如果下述条件之一成立,则称指令j与指令i数据相关:(1)指令j使用指令i产生的结果;(2)指令j与指令k数据相关,而指令k又与指令i数据相关。

系统级流水线(P55)是把多个处理机串行连接起来,对同一数据流进行处理,,每个处理机完成整个任务中的一部分。

西安交大计算机系统结构实验报告.

《计算机系统结构课内实验》实验报告第一次实验:记分牌算法和Tomasulo算法第二次实验:cache性能分析班级:物联网21姓名:李伟东学号:2120509011日期:2015.5.21第一次实验:记分牌算法和Tomasulo算法一、实验目的及要求1. 掌握DLXview模拟器的使用方法;2. 进一步理解指令动态调度的基本思想,了解指令动态调度的基本过程与方法;3. 理解记分牌算法和Tomasulo算法的基本思想,了解它们的基本结构、运行过程;4. 比较分析基本流水线与记分牌算法和Tomasulo算法的性能及优缺点。

二、实验环境DLXview模拟器三、实验内容1.用DLX汇编语言编写代码文件*.s(程序中应包括指令的数据相关、控制相关以及结构相关),以及相关的初始化寄存器文件*.i和数据文件*.d;2.观察程序中出现的数据相关、控制相关、结构相关,并指出三种相关的指令组合;四、实验步骤将自己编写的程序*.s、*.i、*.d装载到DLXview模拟器上,(1)分别用基本流水线、记分牌算法和Tomasulo算法模拟,针对每一种模拟做如下分析:①统计程序的执行周期数和流水线中的暂停时钟周期数;②改变功能部件数目重新模拟,观察并记录性能的改变;③改变功能部件延迟重新模拟,观察并记录性能的改变;论述功能部件数目、功能部件延迟对性能的影响。

(2)记录运行记分牌算法时的功能部件状态表和指令状态表;(3)记录运行Tomasulo算法时的指令状态表和保留站信息;五、实验结果1)基本流水线原始即加法延迟2,乘法延迟5,实验结果显示该段程序运行了11个时钟周期增加了一个除法器。

加法器延迟2,乘法器延迟5,除法器延迟19。

实验结果显示该段程序运行了11个时钟周期。

增加除法器对程序的执行无影响。

加法器延迟2,乘法器延迟6,无除法器。

实验结果显示该段程序运行了12个时钟周期乘法器的延迟对程序执行有有影响。

加法器延迟1,乘法器延迟5。

2022年东莞理工学院软件工程专业《计算机系统结构》科目期末试卷B(有答案)

2022年东莞理工学院软件工程专业《计算机系统结构》科目期末试卷B(有答案)一、选择题1、从计算机系统结构上讲,机器语言程序员所看到的机器属性是()A.计算机软件所要完成的功能B.计算机硬件的全部组成C.编程要用到的硬件组织D.计算机各部件的硬件实现。

2、在计算机系统的层次结构中,机器被定义为()的集合体A.能存储和执行相应语言程序的算法和数据结构B.硬件和微程序(固件)C.软件和固件D.软件和硬件3、系列机软件应做到( )。

A.向前兼容,并向上兼容B.向后兼容,力争向上兼容C.向前兼容,并向下兼容D.向后兼容,力争向下兼容4、对系统程序员不透明的应当是( )。

A.Cache存贮器XB.系列机各档不同的数据通路宽度C.指令缓冲寄存器D.虚拟存贮器5、CRAY-I的流水线是( )A.多条单功能流水线B.一条单功能流水线C.多条多功能流水线D.一条多功能流水线6、以下说法中,不正确的是,软硬件功能是等效的,提高硬件功能的比例会:( )A.提高解题速度B.提高硬件利用率C.提高硬件成本D.减少所需要的存贮器用量7、不同系列的机器之间,实现软件移植的途径不包括( )A.用统一的高级语言B.用统一的汇编语言C.模拟D.仿真8、与全相联映象相比,组相联映象的优点是( )A.目录表小B.块冲突概率低C.命中率高D.主存利用率高9、对机器语言程序员透明的是()A.中断字B.主存地址寄存器C.通用寄存器D.条件码10、下列关于标量流水机的说法不正确的是()A.可对标量数据进行流水处理B.没有向量数据表示C.不能对向量数据进行运算D.可以对向量、数组进行运算二、填空题11、三级存储系统是________、________、磁盘存储器。

12、先行控制(Look-ahead)技术的关键是缓冲技术和预处理技术,以及这两者的相结合,通过对________和数据流的预处理和缓冲,能够尽量使________和________独立地工作,并始终处于忙碌状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Tomasulo方法实验姓名:王宇航学号:09283020

Tomasulo方法实验

一、实验目的:

通过本实验,理解指令流水化过程中乱序执行和寄存器重命名方法。

二、实验内容:

1、用dlxView模拟器或Tomasulo算法模拟器执行浮点指令程序段。

2、指出指令乱序执行和寄存器重命名过程。

三、实验环境

操作系统:Windows 7 旗舰版

处理器:Intel(R) Core(TM) i3 双核

内存:2.00GB

软件:Tomasulo算法模拟器

四、实验过程:

1、设置Tomasulo算法模拟器参数

其中Load部件的执行时间不能

设置为1,至少为2,故不作修改;

加/减法部件的执行时间为4个时钟

周期,乘法部件的执行时间为7个

时钟周期,除法部件的执行时间为

15个时钟周期。

2、分析Tomasulo算法模拟器中指令乱序执行过程

Tomasulo算法模拟器中默认设置的指令下图所示:

执行该指令序列,重点观察指令状态的写结果一栏,便会发现执行过程中存在乱序执行现象,共有两处乱序执行,分别如下列图所示:

图中显示,在第10周期时,位于MULT.D指令之后的SUB.D指令经过4个周期已经执行完成并已经将结果写回寄存器,而MULT.D指令仍在执行中。

在第13周期时,MULT.D指令经过7个周期执行完毕,才将结果写回。

此外,还可以看到,位于DIV.D指令之后的ADD.D指令在第11周期时就已经开始执行,而DIV.D指令直至现在都未开始执行。

在第15周期时,ADD.D指令经过4个周期执行完毕,先于DIV.D指令写回结果;而DIV.D 指令仍在执行中。

在第29周期时,DIV.D指令经过15个周期终于执行完毕,将结果写回寄存器。

以上分析证明,在Tomasulo算法中存在乱序执行并且不会影响执行结果的正确性。

这是因为,Tomasulo算法采用分布的保留站,冲突检测和指令执行控制是分布的。

3、分析Tomasulo算法模拟器中寄存器重命名过程

在Tomasulo算法中通过寄存器重命名来消除WAR冲突,这一过程是通过保留站来完成的。

当指令流出到保留站时,若其操作数已经就绪,则将该指令中相应的寄存器号换为该数据本身;若其操作数还未计算出来,则将该指令中相应的寄存器号重命名为将产生这个操作数的保留站的标识,从而使得该指令与此寄存器不再有关系,后面指令对此寄存器的写入操作也不可能对该指令造成WAR冲突了。

(1)将指令中相应的寄存器号换为数据本身

执行Tomasulo算法模拟器中默认设置的指令序列,容易看出最后一条指令ADD.D和前一条指令DIV.D之间存在一个WAR冲突,即DIV.D指令要读寄存器F8中的值,ADD.D要写寄存器F8中的值,由于乱序执行,ADD.D指令会先于DIV.D指令完成;但是执行结果却不会发生错误,是因为Tomasulo算法通过寄存器重命名将这一冲突消除了。

可以看到在第5周期时,DIV.D指令流出到保留站中,此时F8中的值已经由前面的L.D 指令得出,为M1,但是模拟器并没有将相应的寄存器号R[F8]写入Vk字段中,而是将其换为了F8中数据本身M1,从而使得该指令与寄存器F8不再有关联,无论后面指令怎样改写F8也都不会影响该指令的正确执行了。

此外,由于前面的MULT.D指令还未得出F2的值,故DIV.D指令将寄存器F2重命名为MULT.D指令的保留站标识Mult1,写入Qj字段中。

如下图所示:

在这个周期中,ADD.D指令已经执行完毕,并且已经将寄存器F8中的值由M1改写成了M5,但此时DIV.D指令仍在正确执行着,并没有发生任何错误,并且经过15个执行周期可以正确完成执行过程,第15周期如下图所示:

由此说明了将指令中相应的寄存器号换为数据本身这一寄存器重命名的方法成功地消除了WAR冲突。

(2)将指令中相应的寄存器号重命名为将产生该操作数的保留站的标识

对Tomasulo算法模拟器中默认设置的指令进行重排,将第一条L.D指令后移两个位置,重排后的指令如下图所示:

可以看到,在该指令序列中,最后一条指令ADD.D和前一条指令DIV.D之间仍然存在一个WAR冲突。

执行该指令序列,观察执行过程。

可以发现在第5周期时,DIV.D指令流出到保留站中,而此时前面的L.D指令还未得出F8的值,但是模拟器并没有将相应的寄存器号R[F8]写入Vk字段中,而是将其换为了L.D指令的保留站标识Load2写入了Qk中,从而使得该指令与寄存器F8不再有关联,无论后面指令怎样改写F8也都不会影响该指令的正确执行了,如下图所示:

对寄存器F2的处理和前一种情况的相同。

在第6周期时,保留站Load2完成计算,得出F8的值M2,就会通过CBD将F8的值直接传送到DIV.D指令的保留站Mult2的Vk字段中,如下图所示:

在第12周期时,MULT.D指令得出F2的值后也会通过CDB将其直接送到DIV.D指令的保留站中,DIV.D指令便可以开始执行了。

(3)分析WAW冲突的消除方法

寄存器重命名方法不仅可以消除WAR冲突,还可以配合使用对目标寄存器的预约方法消除WAW冲突。

这一方法的思想是,在一条指令流出到保留站时,将结果寄存器的Qi字段设置为该指令的保留站标识,表示结果寄存器将要接收该指令的结果,这样其实相当于提前完成了写操作。

由于指令是按程序顺序流出的,当出现多条指令写同一个结果寄存器时,最后留下的预约结果必定是最后一条指令的,因此能够消除WAW冲突。

为了演示消除WAW冲突的过程,改写上述指令的最后一条指令,将目标寄存器由F8改为F12,如下图所示:

在该指令序列中,DIV.D指令和最后的ADD.D指令之间存在WAW冲突,即DIV.D指令要写寄存器F12,ADD.D指令也要写寄存器F12,由于乱序执行,ADD.D指令会先于DIV.D指令完成,写结果至寄存器F12。

若没有任何防范措施,当DIV.D指令完成后又会写其执行结果至寄存器F12,修改刚才的ADD.D指令的执行结果,导致结果错误。

但Tomasulo算法通过寄存器重命名和对目标寄存器的预约方法将这一冲突消除了。

执行修改后的指令序列,观察执行过程。

可以看到,在第5周期时,DIV.D指令流出到保留站中,同时将寄存器F12的Qi字段中设为DIV.D指令保留站的标识Mult2,完成预约工作。

如下图所示:

在第6周期时,ADD.D指令流出到保留站中,同时将寄存器F12的Qi字段中改写为该指令保留站的标识Add2,这样就表示寄存器F12最后接收的是ADD.D指令的执行结果,即使DIV.D指令在ADD.D指令之后执行完,也无法再改写寄存器F12了,从而保证了F12中结果的正确性。

如下图所示:

为了验证这一方法的有效性,可以看一下第16周期和第28周期。

在第16周期,ADD.D 指令先于DIV.D指令完成执行过程,将结果写入寄存器F12中,值为M5;在第29周期,DIV.D 指令也完成执行过程,但是再也无法写寄存器F12了,F12中的值仍然为ADD.D指令的执行结果M5,如下图所示:

第16周期

第28周期

由此说明寄存器重命名和对目标寄存器的预约方法成功地消除了WAW冲突。

五、实验总结:

本次实验主要是借助Tomasulo算法模拟器理解指令流水化过程中乱序执行和寄存器重命名方法。

通过在Tomasulo算法模拟器执行存在WAR冲突或者WAW冲突的浮点指令程序段,分析其中的乱序执行现象和寄存器重命名过程,我理解了Tomasulo算法消除WAR冲突和WAW冲突的方法,理解并掌握了寄存器重命名的原理及过程。