数字系统设计与verilog HDL 第6章

数字电路与系统设计

目录分析

1.2数制

1.1数字信号与数 字电路概述

1.3码制

1.5 HDL

1.4算术运算与逻 辑运算

习题

2.1逻辑代数中的运 算

2.2逻辑运算的电路 实现

2.3逻辑运算的公式

2.4逻辑运算的基本 规则

2.5逻辑函数的标准 形式

2.6逻辑函数的化简

2.7 VHDL描述逻辑 门电路

习题

3.2常用中规模集 成组合逻辑电路

程逻辑器件 (CPLD)

3 6.6现场可编

程门阵列 (FPGA)

4

6.7 HDPLD应 用举例

5

习题

1

7.1概述

2

7.2数字系统 的描述工具

3

7.3控制器设 计

4 7.4数字系统

设计及VHDL实 现

5

习题

8.2模数转换(A/D)

8.1数模转换(D/A)

习题

作者介绍

这是《数字电路与系统设计》的读书笔记模板,暂无该书作者的介绍。

(MSI)

3.1 SSI构成的组 合电路的分析和设

计

3.3竞争和冒险

3.4 VHDL描述 组合逻辑电路

习题

4.1概述 4.2基本SRFF

4.3钟控电位触发器 4.4边沿触发器

4.5集成触发器的参 数

4.6触发器应用举例

4.7 VHDL描述触发 器

习题

5.1概述 5.2寄存器

5.3计数器 5.4序列信号发生器

数字电路与系统设计

读书笔记模板

01 思维导图

03 目录分析 05 读书笔记

目录

02 内容摘要 04 作者介绍 06 精彩摘录

思维导图

本书关键字分析思维导图

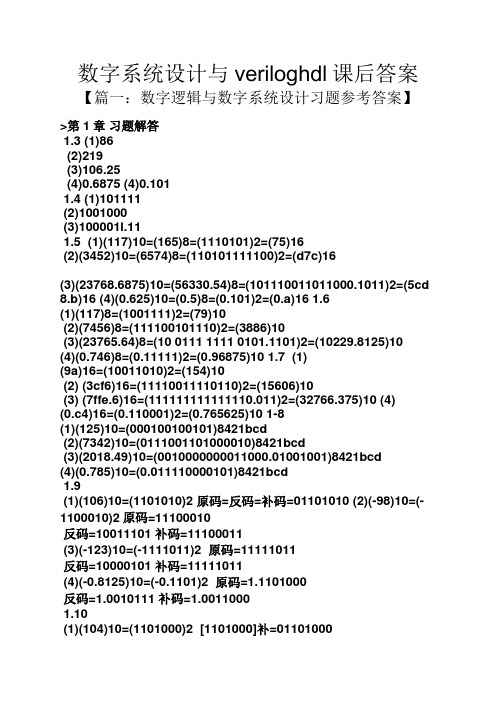

数字系统设计与veriloghdl课后答案

数字系统设计与veriloghdl课后答案【篇一:数字逻辑与数字系统设计习题参考答案】>第1章习题解答1.3 (1)86(2)219(3)106.25(4)0.6875 (4)0.1011.4 (1)101111(2)1001000(3)100001l.111.5 (1)(117)10=(165)8=(1110101)2=(75)16(2)(3452)10=(6574)8=(110101111100)2=(d7c)16(3)(23768.6875)10=(56330.54)8=(101110011011000.1011)2=(5cd 8.b)16 (4)(0.625)10=(0.5)8=(0.101)2=(0.a)16 1.6(1)(117)8=(1001111)2=(79)10(2)(7456)8=(111100101110)2=(3886)10(3)(23765.64)8=(10 0111 1111 0101.1101)2=(10229.8125)10(4)(0.746)8=(0.11111)2=(0.96875)10 1.7 (1)(9a)16=(10011010)2=(154)10(2) (3cf6)16=(11110011110110)2=(15606)10(3) (7ffe.6)16=(111111*********.011)2=(32766.375)10 (4)(0.c4)16=(0.110001)2=(0.765625)10 1-8(1)(125)10=(000100100101)8421bcd(2)(7342)10=(0111001101000010)8421bcd(3)(2018.49)10=(0010000000011000.01001001)8421bcd(4)(0.785)10=(0.011110000101)8421bcd1.9(1)(106)10=(1101010)2 原码=反码=补码=01101010 (2)(-98)10=(-1100010)2原码=11100010反码=10011101 补码=11100011(3)(-123)10=(-1111011)2 原码=11111011反码=10000101 补码=11111011(4)(-0.8125)10=(-0.1101)2 原码=1.1101000反码=1.0010111 补码=1.00110001.10(1)(104)10=(1101000)2 [1101000]补=01101000(-97)10=(-1100001)2 [-1100001]补=1001111101101000 + 10011111 0000011110000011 + 01001111 11010010[104-97]补=01101000+10011111=00000111, 104-97=(00000111)2=7 (2) (-125)10=(-1111101)2(79)10=(01001111)2[-1111101]补=10000011 [01001111]补=0100111101111000 [-125+79]补=10000011+01001111=11010010,-125+79=(-0101110)2=-46 (3) (120)10=(1111000)2[01111000]补=01111000(-67)10=(-1000011)2[-1000011]补=10111101[120-67]补=10000011+01001111=00110101,-125+79=(00110101)2=53 (4) (-87)10=(-1010111)2[-1010111]补=10101001(12)10=(1100)2[1100]补=00001100[-87+12]补=10101001+00001100=10110101,-125+79=(-1001011)2=-75+ 10111101 0011010110101001+ 00001100 10110101第2章习题解答2.3 解:根据逻辑图可直接写出逻辑表达式:(a) f=ab?bc;(b)f=abbcac解:设3个输入变量分别为a、b、c,输出为f,按题意,其中有奇数个为1,则输出f=1,因此可写出其逻辑表达式为f=abc?abc?abc?abc。

精品课件-硬件描述语言与FPGA设计技术(肖闽进)-第6章 宏功能模块与IP应用

f sin_o[9..0] f cos_o[9..0]

out_v alid

inst

OUTPUT OUTPUT

FS[9..0] FC[9..0]

嵌入式逻辑分析仪测试波形

6.6 LPM嵌入式锁相环设计

Altera 的FPGA器件CycloneII/III/IV及 StraixII/III/IV等系列中含有高性能的嵌入式模拟锁相 环,其性能远优于普通数字锁相环。这些锁相环PLL可以 与一输入的时钟信号同步,并以其作为参考信号实现锁 相,从而输出一至多个同步倍频或分频的片内时钟,以 供逻辑系统应用。与直接来自外部的时钟相比,这种片 内时钟可以减少时钟延时和时钟变形,减少片外干扰; 还可以改善时钟的建立时间和保持时间,是系统稳定工 作的保证。

aclr

8 bits 128 words

OUTPUT

CLKOUT

OUTPUT OUTPUT

ADDR[6..0] Q[7..0]

sin2_rom

address[6..0]

q[7..0]

inclock

inst2 Block ty pe: AUTO

OUTPUT

COUT

6.6.2锁相环仿真测试和硬件特性 锁相环仿真波形

加入NCO授权文件和Quartus II授权文件。这里设授权文 件位置路径:C:\altera\90\license.DAT。有了授权文 件,在Option对话框的Licensed AMPP/MegaCore functions 栏中可以看到FIR、PCI、NCO等IP的授权码, 这样就可以编译出能够写Flash的SOF文件。也可以先转 变为间接配置编程文件写入EPCS Flash。

6.1 LPM存储器设计 6.1.1 ROM模块设计

verilogHDL培训教程华为

verilogHDL培训教程华为近年来,随着人工智能、物联网和5G等新兴技术的快速发展,数字电路设计和FPGA开发方面的需求也越来越迫切。

而Verilog HDL已成为数字电路设计中最受欢迎和广泛使用的硬件描述语言之一。

因此,华为公司推出了一系列的Verilog HDL培训教程,帮助从业人员快速获得这个技能。

华为Verilog HDL培训教程的特点华为Verilog HDL培训教程主要针对初学者和中级学员,旨在让学生掌握Verilog HDL基础和应用。

教程内容科学、系统,结合了中国实际情况,给人耳目一新的感觉。

华为Verilog HDL培训教程遵从"理论与实践相结合"的原则,保证学生能够灵活应用所学知识。

在理论教学方面,华为Verilog HDL培训教程先后介绍和讲解了Verilog HDL的基础概念、语法、数据类型、运算符、模块等。

在实践操作方面,华为Verilog HDL培训教程采用基于FPGA芯片的开发板完成实验,让学生能够真正体验到数字电路设计的工程化过程。

此外,华为Verilog HDL培训教程融合了多元化的教学形式,通过讲解PPT、操作演示视频、实验文档等多种形式进行教学。

教材编制过程中对各章节的课程设计进行了充分的考虑,让学生可以从基础入手,系统性、完整性地掌握Verilog HDL语言。

总之,华为Verilog HDL培训教程尽力使学习过程严谨、声音,减少因知识不足而带来的错误和困惑。

华为Verilog HDL培训教程的课程设置华为Verilog HDL培训教程旨在让学员了解数字电路设计中最常用的硬件描述语言-- Verilog HDL,并在FPGA开发板上完成一些典型实验。

华为Verilog HDL培训教程包含以下章节:第一章:Verilog HDL基础概念在本章中,学生将学习Verilog HDL的起源、产生背景、基本概念、Verilog HDL的体系结构、Verilog HDL模块体系结构等知识。

数字系统设计与Verilog HDL

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

fpga数字系统设计课程设计

fpga数字系统设计课程设计一、课程目标知识目标:1. 掌握FPGA数字系统设计的基本原理,理解数字系统的组成及功能;2. 学会使用硬件描述语言(HDL)进行数字电路设计和描述;3. 了解FPGA器件的结构、编程原理以及配置方法;4. 熟悉数字系统的测试与验证方法,掌握基本故障排查技巧。

技能目标:1. 能够运用所学知识,独立完成简单的数字系统设计;2. 掌握使用FPGA开发工具进行代码编写、仿真和调试;3. 学会使用示波器、逻辑分析仪等仪器进行数字电路测试与分析;4. 提高团队协作能力,学会在项目中分工合作,共同解决问题。

情感态度价值观目标:1. 培养学生对数字系统设计的兴趣,激发创新意识;2. 培养学生严谨的科学态度,养成良好的实验习惯;3. 增强学生的自信心和自主学习能力,培养面对挑战的勇气;4. 提高学生的团队合作意识,学会尊重他人,共同进步。

本课程针对高年级学生,结合学科特点,注重理论与实践相结合,旨在培养学生的实际操作能力和创新能力。

课程要求学生在掌握基本理论知识的基础上,通过实际操作,提高数字系统设计能力,为今后从事相关领域工作打下坚实基础。

课程目标的设定,既符合学生特点,又满足了教学要求,为后续教学设计和评估提供了明确的方向。

二、教学内容1. 数字系统设计基础:包括数字逻辑基础、组合逻辑设计、时序逻辑设计等,对应教材第1章至第3章内容。

- 数字逻辑基础:逻辑门、逻辑表达式、逻辑函数化简;- 组合逻辑设计:编码器、译码器、多路选择器、算术逻辑单元;- 时序逻辑设计:触发器、计数器、寄存器、状态机。

2. 硬件描述语言(HDL):以Verilog HDL为例,学习语法、数据类型、运算符、过程语句等,对应教材第4章内容。

- 语法基础:模块定义、端口声明、信号声明;- 数据类型和运算符:基本数据类型、运算符及其优先级;- 过程语句:顺序语句、并行语句、赋值语句。

3. FPGA器件结构与编程:介绍FPGA器件的结构、编程原理、配置方法等,对应教材第5章内容。

数字系统设计与VerilogHDL第五版教学设计

数字系统设计与VerilogHDL第五版教学设计数字系统设计与VerilogHDL是计算机专业的一门重要课程。

在本教学设计中,我们将以第五版数字系统设计与VerilogHDL为教材,为学生提供全面深入的理论学习和实践训练,帮助他们掌握数字系统设计的基本概念、数制转换、逻辑代数、组合逻辑设计和时序逻辑设计,并能够运用VerilogHDL进行数字系统的设计和仿真。

课程目标本课程的主要目标是让学生:1.熟练掌握数字系统设计的基本概念和原理,了解数制转换、逻辑代数、组合逻辑设计和时序逻辑设计等知识点。

2.熟悉VerilogHDL的语法和使用,能够进行数字系统的设计和仿真。

3.具备分析和解决数字系统设计中常见问题的能力,能够进行数字系统的优化和调试。

4.掌握团队协作和沟通能力,能够与他人合作完成数字系统设计的任务。

教学内容与安排教学内容本课程的教学内容包括以下几个部分:1.数字系统设计的基本概念和原理。

2.数制转换、逻辑代数、组合逻辑设计和时序逻辑设计的理论与实践。

3.VerilogHDL的语法和使用,数字系统的设计和仿真。

4.数字系统设计的优化和调试。

5.案例分析与实践项目。

教学安排本课程将采用理论课与实验课相结合的方式进行教学,具体安排如下:1.第1-2周:课程介绍,数字系统设计的基本概念和原理。

2.第3-5周:数制转换、逻辑代数、组合逻辑设计和时序逻辑设计的理论与实践。

3.第6-12周:VerilogHDL的语法和使用,数字系统的设计和仿真。

4.第13-14周:数字系统设计的优化和调试。

5.第15-16周:案例分析与实践项目。

教学方法本课程将采用以下教学方法:1.理论讲解:通过课堂讲解、课件展示等方式,向学生介绍数字系统设计的相关知识点和原理。

2.实验操作:通过实验课方式,让学生亲自操作数字系统设计软件,进行数字系统的设计和仿真,加深对知识点的理解和掌握。

3.课程设计:通过案例分析和实践项目,让学生综合运用所学知识,进行数字系统设计的设计和优化,培养实际操作能力和团队协作能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.关系运算符(Relational operators) < 小于 <= 小于或等于 > 大于 >= 大于或等于

5.等式运算符(Equality Operators) == 等于 != 不等于 === 全等 !== 不全等

例:对于A=2'b1x和 B=2'b1x,则 A==B结果为x, A===B结果为1

关键字(Keywords)

Verilog语言内部已经使用的词称为关键字或

保留字,这些保留字用户不能作为变量或节点

名字使用。

关键字都是小写的。

6.2 常量

程序运行中,值不能被改变的量称为 常量(constants),Verilog中的常量主 要有如下3种类型:

◆ 整数 ◆ 实数

◆ 字符串

整数(integer)

字符串(Strings)

字符串是双引号内的字符序列。 字符串不能分成多行书写。例如:

"INTERNAL ERROR"

字符串的作用主要是用于仿真时,显示一些 相关的信息,或者指定显示的格式。

6.3 数据类型

数据类型(Data Type)是用来表示数字电路中的 物理连线、数据存储和传输单元等物理量的。

空白符和注释

空白符(White space) 空白符包括:空格、tab、换行和换页。空白符使 代码错落有致,阅读起来更方便。在综合时空白符 被忽略。 注释(Comment) ◆ 单行注释:以“//”开始到本行结束,不允许续 行 ◆ 多行注释:多行注释以“/*”开始,到“*/”结 束

标识符(Identifiers)

第6章 Verilog HDL语法与要素

主要内容

6.1 Verilog语言要素 6.2 常量 6.3 数据类型 6.4 参数 6.5 向量 6.6 运算符

6.1 Verilog语言要素

Verilog 程序由符号流构成,符号包括 空白符(White space) 注释(Comments) 操作符(Operators) 数字(Numbers) 字符串(Strings) 标识符(Identifiers) 关键字(Keywords)等

6.缩位运算符(Reduction operators) & 与 ~& 与非 | 或 ~| 或非 ^ 异或 ^~,~^ 同或

7.移位运算符(shift operators) >> 右移 << 左移

例:A=4‘b0111,则 A>>2为4'b0001, A<<2为4'b1100

8.条件运算符(conditional operators)

实数(Real)

实数(Real)有下面两种表示法。 ◆ 十进制表示法。例如: 2.0 0.1 //以上2例是合法的实数表示形式 2. //非法:小数点两侧都必须有数字 ◆ 科学计数法。例如: 43_5.1e2 //其值为43510.0 9.6E2 //960.0 (e与E相同) 5E-4 //0.0005

2.位选择和域选择

在表达式中可任意选中向量中的一位或相邻几位,分别称为 位选择和域选择,例如:

A=mybyte[6]; B=mybyte[5:2];

//位选择 //域选择

再比如: //位选择 //域选择

reg[7:0] a,b; reg[3:0] c; reg d; d=a[7]&b[7]; c=a[7:4]+b[3:0];

Verilog中的变量分为如下两种数据类型: ◆ net型 ◆ variable型 net型中常用的有wire、tri;

variable型包括reg、integer等。 注意:在Verilog-1995标准中,variable型变量称为 register型;在Verilog-2001标准中将register一词改为 了variable,以避免初学者将register和硬件中的寄存器概 念混淆起来。

{4{w}} 等同于 {w,w,w,w}

{b,{3{a,b}}} 等同于 {b,a,b,a,b,a,b}

例:

wire [7:0] Dbus; assign Dbus={Dbus[3:0], Dbus[7:4]}

运算符 (Operators)

在书写程序时建议用括号()来控制运算的优先级

习

题

6.1 下列标识符哪些是合法的,哪些是错误的? Cout, 8sum, \a*b, _data, \wait, initial, $latch 6.2 下列数字的表示是否正确? 6'd18, 'Bx0, 5'b0x110, 'da30, 10'd2, 'hzF 6.3 定义如下的变量和常量: (1)定义一个名为count的整数; (2)定义一个名为ABUS的8位wire总线; (3)定义一个名为address的16位reg型变量,并将该变量 的值赋为十进制数128; (4)定义参数Delay_time, 参数值为8; (5)定义一个名为DELAY的时间变量; (6)定义一个32位的寄存器MYREG; (7)定义一个容量为128,字长为32位的存储器MYMEM;

6.5 向量

1.标量与向量 宽度为1位的变量称为标量,如果在变量声明中没有指定 位宽,则默认为标量(1位)。举例如下:

wire a; //a为标量 reg clk; //clk为标量reg型变量 线宽大于1位的变量(包括net型和variable型)称为 向量(vector)。向量的宽度用下面的形式定义: [msb : lsb] 比如: wire[3:0] bus; //4位的总线

9.位拼接运算符(concatenation operators) {} 该运算符将两个或多个信号的某些位拼接起来。 使用如下: {信号1的某几位,信号2的某几位,……,信号 n的某几位}

普通拼接 重复法 嵌套法

{a,b[3:0],w,3’b101} -〉 {a,b[3],b[2],b[1],b[0],w,3’b101}

整数按如下方式书写: +/-<size> '<base><value> 即 +/-<位宽>'<进制><数字> size 为对应二进制数的宽度;base为进制;value是 基于进制的数字序列。 进制有如下4种表示形式: ◆ 二进制(b或B) ◆ 十进制(d或D或缺省) ◆ 十六进制(h或H) ◆ 八进制(o或O)

6.6 运算符

1.算术运算符(Arithmetic operators) 常用的算术运算符包括: + 加 减 * 乘 / 除 % 求模

2.逻辑运算符(Logical operators) && 逻辑与 || 逻辑或 ! 逻辑非

例:A=3'b110, B=3'b0 A||B 结果为1

3.位运算符(Bitwise operators) 位运算,即将两个操作数按对应位分别进行逻 辑运算。 ~ 按位取反 & 按位与 | 按位或 ^ 按位异或 ^~,~^ 按位同或(符号^~与~^是等价的)

整数(integer)

Examples: 8'b11000101 //位宽为八位的二进制数11000101 8'hd5 //位宽为八位的十六进制数d5; 5'O27 //5位八进制数 4'D2 //4位十进制数2 4'B1x_01 //4位二进制数1x01 5'Hx //5位x(扩展的x),即xxxxx 4'hZ //4位z,即zzzz 8□'h□2A /*在位宽和'之间,以及进制和数值 之间允许出现空格,但'和进制之间,数值间是不允许出 现空格的,比如8'□h2A、8'h2□A等形式都是不合法的 写法 */

Variable型

variable型变量必须放在过程语句(如initial、always)中 ,通过过程赋值语句赋值;在always、initial等过程块内被 赋值的信号也必须定义成variable型。 注意:variable型变量并不意味着一定对应着硬件上的一个 触发器或寄存器等存储元件,在综合器进行综合时, variable型变量会根据具体情况来确定是映射成连线还是映 射为触发器或寄存器。 reg型变量是最常用的一种variable型变量。定义格式如下: reg 数据名1,数据名2,……数据名n; 例如:reg a,b; //定义了两个reg型变量a,b Examples:

reg[7:0] reg[8:1] qout; qout; //定义qout为8位宽的reg型向量

寄存器类型在赋新值以前保持原值 寄存器类型大量应用于行为模型描述及激励描述。在下 面的例子中,reg_a、reg_b、reg_sel用于施加激励 给2:1多路器。 用行为描述结构给寄存器类型赋值。给reg类型赋值是 在过程块中。

net型

Net型数据相当于硬件电路中的各种物理连接,其特点是 输出的值紧跟输入值的变化而变化。对连线型有两种驱 动方式,一种方式是在结构描述中将其连接到一个门元 件或模块的输出端;另一种方式是用持续赋值语句assign 对其进行赋值。 wire是最常用的Net型变量。 wire型变量的定义格式如下: wire 数据名1,数据名2,……数据名n; 例如: wire a,b; //定义了两个wire型变量a和b Examples:

Verilog有下面四种基本的逻辑状态。 ◆ 0:低电平、逻辑0或逻辑非 ◆ 1:高电平、逻辑1或“真” ◆ x或X:不确定或未知的逻辑状态 ◆ z或Z:高阻态 Verilog中的所有数据类型都在上述4类逻辑状态 中取值,其中x和z都不区分大小写,也就是说, 值0x1z与值0X1Z是等同的。