第三章集成逻辑门

数字电子技术第七章数字电子技术第三章ch5

二、 连线的检查

调试前,还需认真检查电路的接线是否正确,以 避免接错线、少接线和多接线。多接线一般是因为接 线时看错引脚,或在改接线时忘记去掉原来的接线而 造成的。这种情况在实验中经常发生,而查线又很难 被发现,调试中则往往会给人造成错觉,以为问题是 元器件故障造成的。如把输出电平一高一低的 两个 TTL 门的输出端无意中连在一起而引起输出电平下降 时,则很容易错误地认为是元器件损坏了。

整机联调一般只观察结果,将测得的参数与设计指标 逐一对比,找出问题,然后进行电路参数的修改,直到完 全符合要求为止。

3.5.3 调试注意事项

一、 熟悉仪器的使用

调试前,先要熟悉仪器的使用方法,并仔细加以检查,以避 免由于仪器使来自不当或出现故障而作出错误判断。

二、 将仪器和被测电路的地线连在一起

分块调试的一般步骤如下:

1. 静态测试

不加输入信号,测试调整模拟电路的静态工作点。对 于数字电路,则加入固定电平,再根据器件的逻辑功能测 试电路各点电位,以判断电路的工作是否正常。这样,可 发现电路存在的问题和找出损坏的元器件。静态测量时, 应选用高内阻 ( 2×104Ω/V ) 万用表或数字万用表进行测量。 对于 A / D 转换器和运算放大器,则需要内阻更高的仪器 (如数字电压表)进行测量。

二、 分块调试

在数字电路中,逻辑值 0 和 1 不是一个固定不变的 值,而是一个数值范围。

数字集成电路的逻辑电平标准

电路类型 参数名称

电源电压 / V

UOH / V UOL / V UIH / V UIL / V

HTTL

5 ≥2.4 ≤0.4 ≥2 ≤0.8

STTL

5 ≥2.7 ≤0.5 ≥2 ≤0.8

三、 调试前的准备

数字电路第三章习题与答案

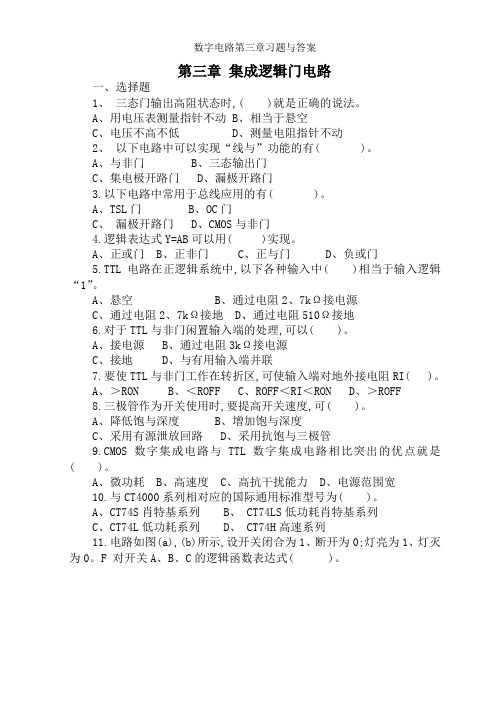

第三章集成逻辑门电路一、选择题1. 三态门输出高阻状态时,()是正确的说法。

A.用电压表测量指针不动B.相当于悬空C.电压不高不低D.测量电阻指针不动2. 以下电路中可以实现“线与”功能的有()。

A.与非门B.三态输出门C.集电极开路门D.漏极开路门3.以下电路中常用于总线应用的有()。

A.TSL门B.OC门C. 漏极开路门D.CMOS与非门4.逻辑表达式Y=AB可以用()实现。

A.正或门B.正非门C.正与门D.负或门5.TTL电路在正逻辑系统中,以下各种输入中()相当于输入逻辑“1”。

A.悬空B.通过电阻2.7kΩ接电源C.通过电阻2.7kΩ接地D.通过电阻510Ω接地6.对于TTL与非门闲置输入端的处理,可以()。

A.接电源B.通过电阻3kΩ接电源C.接地D.与有用输入端并联7.要使TTL与非门工作在转折区,可使输入端对地外接电阻RI()。

A.>RONB.<ROFFC.ROFF<RI<ROND.>ROFF8.三极管作为开关使用时,要提高开关速度,可( )。

A.降低饱和深度B.增加饱和深度C.采用有源泄放回路D.采用抗饱和三极管9.CMOS数字集成电路与TTL数字集成电路相比突出的优点是()。

A.微功耗B.高速度C.高抗干扰能力D.电源范围宽10.与CT4000系列相对应的国际通用标准型号为()。

A.CT74S肖特基系列B. CT74LS低功耗肖特基系列C.CT74L低功耗系列D. CT74H高速系列11.电路如图(a),(b)所示,设开关闭合为1、断开为0;灯亮为1、灯灭为0。

F 对开关A、B、C的逻辑函数表达式()。

F1F 2(a)(b)A.C AB F =1 )(2B A C F += B.C AB F =1 )(2B A C F +=C. C B A F =2 )(2B A C F += 12.某TTL 反相器的主要参数为IIH =20μA ;IIL =1.4mA ;IOH =400μA ;水IOL =14mA ,带同样的门数( )。

数电习题解答_杨志忠_第三章练习题_部分

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第三章 集成逻辑门电路练习题P112【题3.1】在图P3.1所示的电路中,发光二极管正常发光的电流范围是8mA ≤I D ≤12mA ,正向压降为2V ,TTL 与非门输出高电平U OH =3V ,输出高电平电流I OH =-300uA ,输出低电平U OL =0.3V ,输出低电平电流I OL =20mA 。

分别求出图P3.1(a )和(b )中电阻RL1和RL2的取值范围。

解题思路:选择限流电阻R 的原则是既保证发光二极管正常工作又要保证门的输出电流不超载。

解:(a )、电路采用输出低电平驱动发光管;此时流过发光管的电流1CC D OL D L V V V I R −−=;根据发光管的工作条件:8mA ≤I D ≤12mA (最大电流小于门的最大输出电流I OL =20mA ),所以可以得到:1225337.5L R Ω≤≤Ω,门电路输出高电平时发光管熄灭电流为零。

(b )、电路采用输出高电平驱动发光管;此时流过发光管的电流2CC D D OH L V V I I R −=+;根据发光管的工作条件:8mA ≤I D ≤12mA ,所以可以得到:2256.4389.6L R Ω≤≤Ω,同时门电路输出低电平时,门的最大灌入电流要小于I OL =20mA ,由此得到2 4.723520CC OL L OL V V V R I mA−≥==Ω,所以综上所述限流电阻应该为:2256.4389.6L R Ω≤≤Ω。

【3.2】、在图P3.2(a )~(g )所示的TTL 门电路中,已知开门电阻R ON =3K Ω,关门电阻R OFF =0.8K 。

试判断哪些门电路能正常工作?哪些门电路不能正常工作?并且写出能正常工作电路的输出逻辑函数表达式。

解题思路:了解各类门电路的逻辑功能,明白TTL 门的开门电阻R ON ≥3K Ω时相当于在输入端得到高电平“1”,关门电阻R OFF ≤0.8K Ω时相当于在输入端得到低电平“0”。

第三章逻辑门电路

4.74S系列——为肖特基TTL系列,进一步提高了速度。如图示。

5.74LS系列——为低功耗肖特基系列。 6.74AS系列——为先进肖特基系列,

它是74S系列的后继产品。

7.74ALS系列——为先进低 功耗肖特基系列,

t

50%

主要取决于存储时间ts, 5管门电路 tpd=40ns

o tpHL tpLH

t

4、功耗

静态功耗:当电路的输出没有状态转换时的 功耗。 例如:便携计算机、手机和PDA等。 动态功耗:CMOS电路在输出发生状态转换时的 功耗。

5、延时——功耗积

Dp tpdPD

tpd=(tPLH+tPHL)/2用平均传输延迟时间, tPLH---由低电平转换到高电平所花的时间.

SN (1)

74 (2)

S (3)

195 (4)

J 封装的4位并行移位寄存器 (5)

司制造的采用陶瓷双列直插

封装形式 J:陶瓷双列直插封装 器件种类:4位并行移位寄存器 器件系列:肖特基74TTL电路系列 产品系列 74系列 制造厂商 SN:美国TEXAS公司制造

TTL集成逻辑门电路系列简介

1.74系列——为TTL集成电路的早期产品,属中速TTL器件。

输入电压在3.5V~5.0V范围对应高电平逻辑1 输入电压在0~1.5V范围对应低电平逻辑0

输入低电平上限VIL、输入高电平下限VIH、 输出低电平上限VOL、输出高电平下限VOH、

2.噪声容限

1

VOH(min) VNH VIH(min) VIL(max) VNL

1

在保证输出高、低电平基本不变 的条件下,输入电平的允许波动 范围称为输入端噪声容限。

数电第三章讲解

起低阻通道,形成较大的 脉冲电流。 不仅增加了CMOS电路的 功耗,而且也成为CMOS 电路的内部干扰源。

22

3. CMOS反相器的输入特性

由于信号从栅极输入, 输入电阻很大,又有一个小的寄生电容, 如果输入端没有保护电路, 输入端可能被静电感应充电至高压, 造成绝缘栅击穿,使器件永久损坏。 为避免造成栅极击穿, 实际的CMOS集成电路的每一个输入端都设有输入保

第3章 集成逻辑门电路

3.1 概述

逻辑门电路(门电路): 用来实现基本逻辑关系的电子电路 集成逻辑门电路: 将若干个逻辑门电路集成在一块半导体材料基片上

1

集成逻辑门电路有两种类型器件:

(1)由三极管组成的双极型集成电路

例如:晶体管-晶体管逻辑电路 (简称TTL:Transistor-Transistor Logic)

和增强型NMOS驱动管(TN) 串联组成

11

TP的开启电压VGS(th)P < 0 TN的开启电压VGS(th)N > 0 电路正常工作的条件: VDD >∣VGS(th)P∣+ VGS(th)N,

且VGS(th)N =∣VGS(th)P∣, TN和TP具有相同的导通电阻

Ron和截止电阻Roff。

12

2.工作原理

当输入为低电平时: TN的VGSN = 0 v < VGS(th)N 管子截止。 TP的∣VGSP ∣= VDD 管子导通, 输出为高电平VOH vO =VOH≈VDD

13

当输入为高电平VDD时

TN的VGSN = VDD >VGS(th)N, 管子导通。 TP的VGSP = 0 v > VGS(th)P 负载管截止。 输出为低电平VOL, vO =VOL≈0 v。

第 三 章 逻辑门电路

是构成数字电路的基本单元之一

CMOS 集成门电路 用互补对称 MOS 管构成的逻辑门电路。

TTL 集成门电路 输入端和输出端都用 三极管的逻辑门电路。

CMOS 即 Complementary Metal-Oxide-Semiconductor TTL 即 Transistor-Transistor Logic 按功能特点不同分 普通门 输出 三态门 CMOS (推拉式输出) 开路门 传输门 EXIT

CE(sat) CE

B

C

uI 增大使 uBE > Uth 时,三极管开始导通, iB > 0,三极管工作于放 大导通状态。

uBE < Uth E

三极管 截止状态 等效电路

EXIT

iC 临界饱和线 M T IC(sat) + uBE S Q

放大区

IB(sat)

uI=UIH

饱 和 区

O UCE(sat)

t

uI 负跳变到 iC 下降到 0.1IC(sat) 所需的时间 toff 称 为三极管关断时间。 通常 toff > ton

UCE(sat) O

开关时间主要由于电 通常工作频率不高时, 荷存储效应引起,要提高 可忽略开关时间,而工作 开关速度,必须降低三极 频率高时,必须考虑开关 管饱和深度,加速基区存 速度是否合适,否则导致 储电荷的消散。 不能正常工作。 EXIT t

iB 0,iC 0,C、E 间相当 于开关断开。

三极管 截止状态 等效电路

E

Uth为门限电压 EXIT

iC u S 为放大和饱和的交界点,这时的临界饱和线I 增大使 iB 增大, 放大区 从而工作点上移, iC 增 iB 称临界饱和基极电流,用 IB(sat) 表示; M T 相应地,IC(sat) 为临界饱和集电极电流; S 大,uCEI减小。 IC(sat) B(sat) UBE(sat) 为饱和基极电压; 饱 Q UCE(sat) 为饱和集电极电压。对硅管, 和 截止区 UBE(sat) 0.7V, UCE(sat) 0.3V。在临 A 区 界饱和点三极管仍然具有放大作用。 U O N u

第三章集成逻辑门电路例题补充

第三章集成逻辑门电路例题补充第2章 逻辑门电路2.1解题指导【例2-1】 试用74LS 系列逻辑门,驱动一只V D =1.5V ,I D =6mA 的发光二极管。

解:74LS 系列与之对应的是T4000系列。

与非门74LS00的I OL 为4mA ,不能驱动I D =6mA 的发光二极管。

集电极开路与非门74LS01的I OL 为6mA ,故可选用74LS01来驱动发光二极管,其电路如图所示。

限流电阻R 为Ω=--=--=k V V V R OL D CC 5.065.05.156【例2-2】 试分析图2-2所示电路的逻辑功能。

解:由模拟开关的功能知:当A =1时,开关接通。

传输门导通时,其导通电阻小于1k Ω,1k Ω与200k Ω电阻分压,输出电平近似为0V 。

而A =0时,开关断开,呈高阻态。

109Ω以上的电阻与200k Ω电阻分压,输出电平近似为V DD 。

V V V 020011DDF≈+=DDDD44DD599F210101021010V V V V ≈+≈⨯+=故电路实现了非逻辑功能。

【例2-3】试写出由TTL门构成的逻辑图如图2-3所示的输出F。

&≥1F ≥1AB图2-3 例2-3门电路解:由TTL门输入端悬空逻辑上认为是1可写出【例2-4】试分别写出由TTL门和CMOS 门构成的如图2-4所示逻辑图的表达式或逻辑值。

&&B F10kΩ图2-4 例2-4门电路解:由TTL门组成上面逻辑门由于10kΩ大于开门电阻R ON,所以,无论A、B为何值。

由CMOS门组成上面逻辑门由于CMOS无开门电阻和关门电阻之说,所以,。

2.2 例题补充2-1 一个电路如图2-5所示,其三极管为硅管,β=20,试求:ν1小于何值时,三极管T截止,ν1大于何值时,三极管T饱和。

解:设v BE=0V时,三极管T截止。

T截止V CCv Iv O +10VABAF=++⋅=11≡FABF=时,I B =0。

数字电路第三章习题与答案

第三章集成逻辑门电路一、选择题1、三态门输出高阻状态时,( )就是正确的说法。

A、用电压表测量指针不动B、相当于悬空C、电压不高不低D、测量电阻指针不动2、以下电路中可以实现“线与”功能的有( )。

A、与非门B、三态输出门C、集电极开路门D、漏极开路门3.以下电路中常用于总线应用的有( )。

A、TSL门B、OC门C、漏极开路门D、CMOS与非门4.逻辑表达式Y=AB可以用( )实现。

A、正或门B、正非门C、正与门D、负或门5.TTL电路在正逻辑系统中,以下各种输入中( )相当于输入逻辑“1”。

A、悬空B、通过电阻2、7kΩ接电源C、通过电阻2、7kΩ接地D、通过电阻510Ω接地6.对于TTL与非门闲置输入端的处理,可以( )。

A、接电源B、通过电阻3kΩ接电源C、接地D、与有用输入端并联7.要使TTL与非门工作在转折区,可使输入端对地外接电阻RI( )。

A、>RONB、<ROFFC、ROFF<RI<ROND、>ROFF8.三极管作为开关使用时,要提高开关速度,可( )。

A、降低饱与深度B、增加饱与深度C、采用有源泄放回路D、采用抗饱与三极管9.CMOS数字集成电路与TTL数字集成电路相比突出的优点就是( )。

A、微功耗B、高速度C、高抗干扰能力D、电源范围宽10.与CT4000系列相对应的国际通用标准型号为( )。

A、CT74S肖特基系列B、 CT74LS低功耗肖特基系列C、CT74L低功耗系列D、 CT74H高速系列11.电路如图(a),(b)所示,设开关闭合为1、断开为0;灯亮为1、灯灭为0。

F 对开关A、B、C的逻辑函数表达式( )。

F1F 2(a)(b)A.C AB F =1 )(2B A C F +=B.C AB F =1 )(2B A C F +=C. C B A F =2 )(2B A C F +=12.某TTL 反相器的主要参数为IIH =20μA;IIL =1、4mA;IOH =400μA;水IOL =14mA,带同样的门数( )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2、动态特性

uD

VD

0

uD

iD

R

上升时间

当uD 为一矩形电压时

二极管VD的电流的变化过程

iD

0

电流波形的不够陡峭(不理想)

存储时间

上升时间:二极管从截止到导通所需的时间。

t

渡越时间

t

漏电流

反相恢复时间:二极管从导通到截止所需要的时间,等于存储 时间+渡越时间,其值远远大于上升时间,二极管的速度主要 取决于反相恢复时间。

D1

A

D2

B

D

C

3

R 3kΩ

P D4

D5 1

R1 4.7kΩ

+VCC(+5V)

Rc 1kΩ

3

L

2T

二、TTL与非门

1、TTL与非门的基本结构

输入级由多发射极晶体管 T1 R b1

和基极电组Rb1组成。

4k Ω

1

多发射极三极管 在功能上相当于 三个三极管的并 联运用。

输入级

A B C

31

T1

b

b

Rc2 1. 6kΩ

Vc2

1

3

2T 2

Ve2

1

R e2 1k Ω

5V + VC C(

R c4 13 0Ω

3

T2 4

D

Vo

3

2T 3

eA eB eC

c eA

输 入级

eB eC c

中 间级

输 出级

中间级是放大级,由T2、Rc2 和Re2组成.

R b1 4k Ω

Rc2 1. 6kΩ

Vc2

1

+ VC C( + 5 V ) R c4 13 0Ω

iC

0

ton

toff

引起的,内部载流子的运动过程比较

复杂。

UCC

Ucc

截止到饱和i所C 需的R时c 间称为开启时间 uO

UCES

ton,它R基B 本上由三极管uO自身决定。 T

饱和uI到截止所iB 需的时间称uCE为关闭时间toff,它与饱和深度S有直 接关系,S越大toff越长。

3.2 TTL集成逻辑门

IBS U CC

RC

ui

iB

uO

T

uo

定义饱和深度: 三极管开关等效电路

S iB I BS

ube ≥ 0.7V S闭合

ube < 0.7V S断开

S

2、三极管的动态开关特性

UIL

当基极施加一矩形电压uI时

uI UIL

iC、uO波形不够陡峭, iC、uO滞后于uI,

ICS

即三极管在截止与饱和状态转换需要 一定的时间。这是由三极管的结电容

3

T2 4 截 止

D 截止

Vo

3 0.3V

2T 3 饱和

(2)输入有低电平0.3V 时。

该发射结导通,VB1=1V。T2、T3都截止。 忽略流过RC2的电流,VB4≈VCC=5V 。

由于T4和D导通,所以:

VO≈VCC -VBE4 -VD

= 5 -0.7 -0.7 = 3.6(V)

实现了与非门的逻辑

端。多射极管工作放大状态。 - i b2 是T2管的反向驱动

i c1 = βi b1 = - i b2

电流。使T2管快速截止, 缩短了开关时间。

多射极管的优点:对T2管提供很大的反向驱散电流,

使T2 管很快由饱和转变为截止。

前一页 下一页

退出

(2)采用了推拉式输出级

当T4、D导通时,射极输

出,输出阻抗小;

二、三极管的开关特性

1、三极管的开关特性

在数字电路中工作在饱和区或截止区——开关状态。 UCC 下面以NPN硅管为例进行分析

ui = uiL≈0 iB = 0 ic≈0

uo≈ ucc

iC Rc

ui = uiH iB > iC /β Uo= ucES ≈0

RB

临界饱和基极电流:

可靠饱和条件为:iB≥IBS

3

T2 4

1

3

31

A

2T 2

B

T1

C

Ve2

R e2

1k Ω

输出级:由T3、T4和Rc4、D组成 T3、T4在输入信号的输 作入 级用下,轮流中 导间 级 通,一个导通,另一个截止。叫中做间推级 拉输出级。

D

Vo

3

1

2T 3

输 出级

输出级

2.TTL与非门的逻辑关系

(1)输入全为高电平3.6V时。 由于T3饱和导通,输出电压为:

第三章 集成逻辑门

3.1 晶体管的开关特性 3.2 TTL集成逻辑门 3.3 CMOS电路 3.4 VHDL描述逻辑门电路

前一页 下一页

退出

3.1 晶体管的开关特性

前一页 下一页

退出

一、二极管的开关特性

1、静态特性 伏安特性

iD

+-

导通时的等效电路

截止时的等效电路

0

uD -

+

二极管加正向电压时导通,伏安特性很陡,压降很小(硅管: 0.7V,锗管0.3V),可以近似看作是一个闭合的开关 二极管加反向电压时截止,截止后的伏安特性具有饱和特性 (反向电流几乎不随反向电压的增大而增大)且反向电流很 小(nA级),可以近似看作是一个断打开的开关

由于T2饱和导通,VC2=1V。

VO=VCES3≈0.3V

T4和二极管D都截止。

实现了与非门的 逻辑功能之一:

输入全为高电平

时,输出为低电

A B

平。

C

1

R b1 4k Ω

2.1V

31 . 4 V1

T1 倒置状态

3.6V

Rc2 1. 6k Ω

1V 1

3

2T 2 饱 和

0 . 7 V1

R e2 1K

+ VC C( + 5 V ) R c4 13 0Ω

一、DTL与非门

工作原理:

(1)当A、B、C全接为高电平5V时,二极管D1~D3都截止,而D4、

D5和T导通,且T为饱和导通, VL=0.3V,即输出低电平。 (2)A、B、C中只要有一个为低电平0.3V时,则VP≈1V,从而使D4、 D5和T都截止,VL=VCC=5V,即输出高电平。

所以该电路满足与非逻辑关系,即: LABC

4.3V

D 导通

Vo

3 3.6V

2T 3 截止

3、TTL与非门提高工作速度的原理

(1)采用多发射极三极管加快了存储电荷的消散过程。

当输入全接3.6V时:

VCC

Vb1=1.4V时: T1管集电结,

R1

RC

T2管发射结导通。正向驱动电

流很大,T2管快速饱和。

1

T1

T2

当输入中有一个由

3.6V

0

基极电流i b1流向低电平输入

功能的另一方面:

输入有低电平时, 输出为高电平。

R b1 4kΩ

1

综合上述两种情况, 3.6V 1V

该电路满足与非的

0.4V

31

A

逻辑功能,即: B

T1

C

饱和

LABC

0.3V

前一页 下一页

退出

Rc2 1.6 kΩ

5V 1

3

2T 2 截 止

1

R e2 1kΩ

+ VC C R c4 130 Ω

3

T2 4 导 通

T4

1

当T3导通时,T3为 导 通

深度饱和,输3

TTL 电 路 的 负 载

1

截止

能力强,当遇到

+ VC C( + 5V ) R c4

3 2

充电

3 2

Vo CL

+ VC C( + 5V ) R c4

T4

1

截止

D

截止

T3

1

导通

3 2

3 2

放电

Vo CL

容性负载是,其

冲放电速度快。 另当T2截止时,T4饱和,这样导致T3上