xilinx的prom配置经验

Xilinx FPGA 中文手册-《Platform Flash PROM User Guide》中文版

《Platform Flash PROM User Guide》中文版FPGA的配置分为主串行和从串行两种,差别在于时钟源不同。

nCF为高时PROM的DO数据有效,nCE和OE使能。

P24和26介绍了接线图和引脚功能。

原型开发优势每写一次可以有4套不同的程序进行测试。

板子测试配置或安全升级设计的版本中写有诊断程序,如果发现原程序不满足要求,可以调用符合要求的程序重新执行,节省了调试时间。

PlatForm具有备份程序的功能。

防止不完整或损坏数据FPGA的所有IO口在DONE为低电平时均不可用,PlatForm满足这个要求。

为什么使用内部解压或晶振Platform PROM片上解压使得用户可以多存储50%的数据。

Platform PROM提供20MHz或者40MHz(默认)的时钟用于将配置数据从PROM送入FPGA。

内部晶振,特别是40MHz的操作只应用于解压模式。

否则,FPGA的CCLK或者外部晶振会用于驱动。

PROM的解压输出数据速率为内部时钟的一半,换言之,解压数据流配置时间是非压缩数据流的两倍。

如果需要快速配置,FPGA的BitGen-g compress方式可以作为压缩模式。

时钟CLKOUT信号在配置过程中,且在nCE低、OE/nRESET高时有效;无效时呈高组态并且需要外部上拉以避免不确定状态。

时钟速率可以配置,默认为1MHz,可以为1,3,6,12等,XCFxxS最大为33MHz。

PROM文件生成和烧写.bit(Bitstream)文件为输入数据流,.mcs文件为输出数据,.cfi文件为配置格式信息文件。

.bit文件为FPGA使用的二进制数据,.mcs文件为PROM运行文件,.cfi(Configuration format information)文件名字与前两者根目录相同。

标准的PROM文件为前两者。

在XCFxxP系列PROM使用多版本程序设计、CLKOUT、解压缩等功能时还需要使用.cfi文件。

Xilinx-FPGA配置的一些细节

Xilinx-FPGA配置的一些细节Xilinx FPGA配置的一些细节2010年07月03日星期六 14:260 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录下有。

(2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005在Xilinx网站上有,链接/bvdocs/appnotes/xap p138.pdf(3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007在Xilinx网站上有,链接/bvdocs/appnotes/xap p502.pdf注:此外xapp139和xapp151也是和配置相关的。

(4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007(5) Tell me about the .BIT file format.链接:/FAQ_Pages/0026_Tell_me_about_bit_files.htm1 Xilinx配置过程主要讲一下Startup Sequence。

Startup Sequence由8个状态组成.除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。

其中默认顺序如下:这些在ISE生成bit文件时通过属性页设定。

这几个状态的具体含义如下:Release_DONE : DONE信号变高GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态GTS : 激活用户IO,之前都是高阻。

prom下载方式

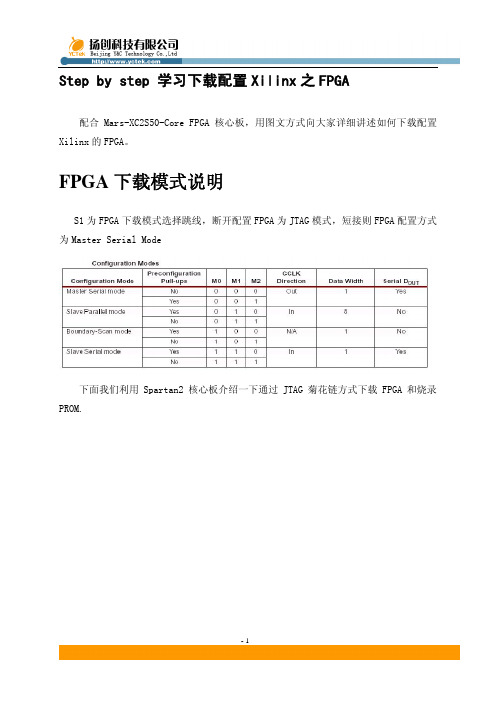

Step by step 学习下载配置Xilinx之FPGA配合Mars-XC2S50-Core FPGA核心板,用图文方式向大家详细讲述如何下载配置Xilinx的FPGA。

FPGA下载模式说明S1为FPGA下载模式选择跳线,断开配置FPGA为JTAG模式,短接则FPGA配置方式为Master Serial Mode下面我们利用Spartan2核心板介绍一下通过JTAG菊花链方式下载FPGA和烧录PROM.硬件跳线选择1. 跳线S1: 此时要求M0 M1 M2 = 100, 断开即可设置FPGA的下载方式为Boundary-scan mode。

2. 将Xilinx下载线和核心板上JTAG mode接口J2相连,连接到计算机并口。

3. 目标板上电。

软件操作一、产生PROM配置文件在烧写PROM之前,需要将ISE生成的*.bit文件转换成prom格式的文件才能下载Xilinx 专用的配置PROM中。

1. 启动iMPACT2. 出现下面画面选择Prepare Configuration Files,点击下一步。

3.出现如下界面,选择PROM File,点击下一步。

4.界面如下,选择PROM类型,和文件格式,填写生成文件名称路径,下一步5.指定使用的PROM类型,并添加,下一步。

6.下一步7点击Add File按钮。

8.选上需要转换的*.bit文件打开。

9.出现如下对话框,提示要不要添加另外的.bit文件。

选择否10界面如下,点击完成11.出现要不要现在生成配置文件,选择是,至此,PROM的文件已经生成。

12.OK.二.菊花链方式下载配置FPGA和PROM 1.打开iMPACT配置2.出现如下界面,选择Configure Device, 下一步。

3.选择Boundary-Scan Mode,下一步。

4.选自动监测扫描链,完成。

5.出现如下界面,检测到两个器件:xc2s50和xcf01s,并提示是否为每个器件添加配置文件。

XILINX ROM 使用教程

打开XILINX的ISE,右键点击选择NEW SOURCENEW SOURCE中选择IP,写好NAME,点击下一步。

在下图中选择你要的IP核。

第一个是Block Memory生成设置向导;第二个是分布式 Memory生成设置向导;第四个是双口BLOCK RAM;是使用分布式ROM-如果你的ROM不是很大的话,而且内部BLOCK RAM 资源有限的情况下,使用分布式ROM可以为你节约不少BLOCK RAM,但是它会占用一些逻辑资源。

. 第五个是单口BLOCK RAM.选择你想要使用的IP核,(以选择向导为例)点击NEXT选择使用的Memory类型:如图设置Memory位宽和深度这里比较关键,要导入ROM的值。

这个文件就是你要放在ROM中的数据,文件的后缀名是.COE。

你可以自己建一个空的文本文件,然后把后缀名该为.COE即可。

文件内容的格式如下:MEMORY_INITIALIZATION_RADIX=10;MEMORY_INITIALIZATION_VECTOR=32767,32766,32766,32765,32764,32763,32761,32759,32757,……32754;注意:第一行定义文件中的数据采用什么进制。

可以使用10进制,2进制,16进制,数据大小不能超过你定义的数据宽度。

第二行照抄。

第三行开始就是数据了,每个数据用逗号","隔开,可以不分行,建议分行写,便于统计个数。

最后一个数据后用分号";"结束。

数据的个数必须和你定义的数据深度相同,否则会出错。

写好这个文件后,保存。

导入.coe文件后,如果没有错误,可以点击旁边的show查看数据。

点击next,最后查看设置的信息现在,可以点击finishi,产生IP。

产生的代码中有个.MIF文件,就是ROM的数据的二进制文件。

其中的.V 文件或.VHD就是生成的可综合的代码。

如上图的ROM_COS.XCO,选择它,双击VIEW HDL FUNCTIONAL MODEL就可查看Verilog代码。

从配置PROMFLASH读取用户数据

从配置PROM/FLASH读取用户数据时间:2022-02-03 来源:******************作者:freehardman 点击:147 字体大小:【大中小】前沿在FPGA 设计中,配置FLASH (XCF00 系列)主要的功能是存储FPGA 设计,然后在上电之后,自动将设计装载到FPGA 之中。

在有些时候,FPGA 设计并未全部将配置FLASH 的存储单元全部占用,因此,未被占用的单元就被浪费掉了。

在某些应用中,用户需要在片外 (FPGA 外)存储自己定义的数据,这个时候就要单独挂FLASH 芯片到FPGA 上,这样不仅增加了设计难度(用户需要专门编写存储控制接口)、增加成本、增加布板难度、增加FPGA 管脚使用数量等,从而给设计者带来不少不便。

如果用户自定义的数据量不是很大,而且正好可以放到FLASH 的未被占用的存储单元中,那末将极大减轻设计者的负担,减少成本,增加系统可靠性。

下面将详细介绍如何将用户自定义数据存储到PROM/FLASH 中,以及如何读取这些数据。

具体实现原理要想实现将用户自定义数据写入FLASH 以及从它们之中读出来,首先要明确以下几个问题:. FPGA 设计数据如何被写入到FLASH 之中. FLASH 中的数据如何被读到FPGA 之中(配置FPGA 过程)理解了以上两个问题,我们就能从总体上知道是什么原理使用户数据能写入到FLASH 当中,并被读出来。

看FIG1:(注:以下所有的讨论都是认为FPGA 的配置模式是主-串模式)在FIG1 中,有几个关键信号:CCLK,CE/,OE_RESET/,INIT/ (INIT/在FPGA 上)。

在主-串模式配置过程中,上电之后,由FPGA 的CCLK 引脚发出时钟,驱动FLASH 的CLK,而FLASH 根据CE/、OE_RESET/的状态来确定是否地址增加(此地址是FLASH 内部数据存储单元的地址) 。

如果FPGA 将所有的设计数据读取完毕,则住手产生CCLK 时钟。

PROM的设计修订功能

利用Platform Flash PROM 实现多重启动功能2007-09-12 11:19:34 作者:Jameel Hussein 来源:赛灵思公司关键字:动态配置时钟周期提要一些应用利用Xilinx FPGA 在每次启动时可改变配置的能力,根据所需来改变FPGA 的功能。

Xilinx Platform Flash XCFxxP PROM 的设计修订(Design Revisioning) 功能,允许用户在单个PROM 中将多种配置存储为不同的修订版本,从而简化了FPGA 配置更改。

在FPGA 内部加入少量的逻辑,用户就能在PROM 中存储的多达四个不同的修订版本之间进行动态切换。

多重启动或从多个设计修订进行动态重新配置的能力,与Spartan-3E FPGA 和第三方并行flash PROM 一起使用时所提供的MultiBoot 选项相似。

本应用指南将进一步说明Platform Flash PROM 如何提供附加选项来增强配置失败时的安全性,以及如何减少引脚数量和板面积。

此外,Platform Flash PROM 还为用户提供其他优势:iMPACT 编程支持、单一供应商解决方案、低成本板设计和更快速的配置加载。

本应用指南还详细地介绍了一个包含VHDL 源代码的参考设计。

简介与FPGA 少量的内部逻辑结合,Platform Flash PROM 可方便地支持需要动态选择多种FPGA配置或修订版本(即多重启动)的应用。

利用Xilinx Platform Flash 的设计修订功能和FPGA少量的内部逻辑,即可实现多重启动。

该示例为需要多重启动功能的应用,此时FPGA 需要同时支持一般功能和诊断功能(图1)。

在这种情况下,FPGA 使用诊断应用启动以进行板级测试。

如果测试成功,FPGA 就通过第二个包含正常工作所需的一般功能配置镜像的比特流触发重配置。

一般的FPGA 应用设计用于进行重配置,以便随时按需重新加载诊断应用。

XilinxISE软件使用过程新(含PROM下载)

Xilinx ISE 13.4软件使用方法本章将以实现一个如图所示的4为加法器为例,来介绍Xilinx ISE13.4开发流程,并且最终下载到实验板BASYS2中运行。

4位加法器C0C 1A0A1A2A B0B1B2B3S0S 1S2S331.建立工程运行Xilinx ISE Design Suite 13.4,初始界面如图F2所示所示F1软件初始状态表软件初始状态表选择File->New Project ,该对话框显示用向导新建工程所需的步骤。

,该对话框显示用向导新建工程所需的步骤。

在Name 栏中输入工程名称(注意:以下所有不能含有中文字符或空格),如“test”。

在Location 栏中选择想要存放的工程位置,如“E:“E:\code\Xilinx\\code\Xilinx\\code\Xilinx\test”test”。

顶层语言选项栏中选择“HDL”语言。

设置向导最终设置效果如图F2所示所示F2路径信息设置表路径信息设置表点击“Next”,进入芯片型号选择界面。

进入芯片型号选择界面。

在本界面中,在本界面中,根据BASYS2实验板上的芯片型号进行相关设置,设置效果如图F3所示。

所示。

F3芯片信息选择表芯片信息选择表点击“Next Next””,出现如图F4所示工程信息汇总表格。

所示工程信息汇总表格。

F4工程信息汇总表工程信息汇总表点击“Finish”完成设置。

完成设置。

2新建V erilog文件在F5所示界面中,如图所示的区域内右击鼠标,选择“New Source”,出现F6对话框。

对话框。

F5在File name栏中键入verilog文件的名称,如“test”。

F6Next””,在本界面中将设置加法器的输入输出引脚数量,如图F1所示点击“Next的加法器共有A、B、C0、S和C1,5组引脚,其中A、B和S为4位总线形式,所示。

因此设置结果如图F7所示。

F7点击“Next”,出现V erilog 新建信息汇总表。

【配置知识】Virtex-5 FPGA 的配置

【配置知识】Virtex-5 FPGA的配置配置方案Xilinx 为终端用户提供了配置Virtex-5 FPGA 所需的灵活性。

Virtex-5 FPGA 支持以下方案:串行最简单的配置方案,串行吞吐量。

主串行Xilinx FPGA 驱动Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

从串行Xilinx PROM 的内部振荡器驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

从串行外部时钟驱动Xilinx PROM CLK,Xilinx PROM 驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xil inx FPGA 提供了串行(x1)配置数据。

返回页首从串行外部时钟驱动Xilinx FPGA CLK 和Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

主SPIVirtex-5 FPGA 驱动SPI PROM 时钟,因为SPI PROM 为Virtex-5 FPGA 提供了串行(x1)配置数据。

并行并行配置,可以实现最快速的吞吐量主并(Master-SelectMap)Xilinx FPGA 驱动Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了字节宽的(x8)配置数据。

返回页首从并(slave-SelectMAP)Xilinx PROM 的内部振荡器驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xilinx FPGA 提供了字节宽的(x8)配置数据。

从并(slave-SelectMAP)外部时钟驱动Xilinx PROM CLK,Xilinx PROM 驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xil inx FPGA 提供了字节宽的(x8)配置数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

复位和上电复位

1 在上电时,这器件要求VCCINT在精确的上升时间内,单调的上升到标准工作电压值。

2 如果电压没满足要求,这器件就不能执行合适的上电复位。

3 上电运行的顺序:先PROM的OE/RESET保持低电平,在配置开始以前要求电源能达到它们各自的POR(上

电复位电压)门限,OE/RESET被定时释放后对稳定电源的应用有更多的余地。

4 在系统利用慢上升电源时,另外增加一个电源监控电路能被用做延时配置直到系统电源达到最小的操作

电源在OE/RESET一直为低电平。

5 当OE/RESET被释放,INIT就被上拉为高电平,允许FPGA有次序的配置。

6 如果电压低于POR门限时,PROM复位,OE/RESET再为低,直到达到POR 门限。

7 对于PROM电压正常时,只要OE/RESET=0或CE=1,复位就开始,当地址计数器复位时,CEO输出高电平,其

它的数据输出脚为高阻态。

8 XCFXXS PROM 只要求OE/RESET被释放以前,VCCINT上升到POR门限就行了。

9 XFCXXP PROM 在OE/RESET被释放以前,不但要求VCCINT上升到POR 门限,而且还要求VCCO达到被推荐的

正常工作电压。

配置

1 当JTAG配置指令在PROM里被更新时,PROM暂时给CF一个低电平,接着就给CF一个高电平。

结合CF脚在外

部加了上拉电阻,此时在CF脚输出一个‘高-低-高’的脉冲个FPGA的PROGRAM 脚。

此次FPGA就依次的开始

配置。

2 在CF脚外部必须加个上拉电阻,防止CF脚产生一个浮动到低电平的值而引起复位。

3 当XCFXXP的PROM存有多重设计文件时,CF脚必须连接到FPGA的PROGRAM_B脚去保证重新安放那些被选中

的设计文件(配置有效)。

4 对于XCFXXS的PROM,CF脚只是个输出,如果没有由于的功能的话,可以

不用连接FPGA。

在SPARTAN FPGA系列中,INIT_B脚使用内部下拉有典型的补偿,外部上拉电阻在INIT_B脚时,能产生一个

不明确的信号给PROM的OE/RESET脚,鉴别一个错误的配置,CRC错误在INIT_B脚。