Xilinx FPGA的PROM配置

Nexys2 开发板手册

NEXYS 2开发板参考手册Digilent的Nexys2电路板是基于Xilinx的Spartan-3E FPGA芯片的电路开发平台,该板包含有高速的USB2端口,16MB的RAM和ROM,一些串行I/O设备和端口,使得该平台成为设计各种数字系统的理想平台,并且可以实现基于Xilinx的MicroBlaze处理器的片上系统的设计。

USB2提供了板上的电源和编程接口,所以Nexys2板和笔记本一起使用来建立一个真正的便携式的设计平台。

4个12针的外设模块(Pmod)接口能连接低成本的Pmod模块,比如:电机控制,A/D和D/A转换器、音频电路和传感器。

所有用户可访问的Nexys2板上信号都有ESD和短路保护。

Nexys2板可以使用任何版本的Xilinx的ISE工具。

图1.1给出了该开发平台的结构图,该开发平台的特性主要包括:使用Xilinx 1200K门的Spartan 3E FPGA器件基于USB2的FPGA配置和高速数据传输(使用Digilent提供的免费的Adept Suite软件工具)USB 供电(也可使用外接电源)Micron的16MB的PSDRAM和Intel的16MB的StrataFlash ROM芯片⎫Xilinx的平台存储器用于非易失性配置高效的开关电源供电⎫50MHz的晶振和晶振的扩展插槽⎫60个FPGA的I/O口连接到扩展连接器(一个高速的Hirose FX2连接器和4个6针的插头)8个LED,4个的7段数码管,4个按钮,8个拨码开关1.平台电源Nexys2板的输入电源可以来自USB电缆,或者5VDC-15VDC的外接电源插孔,板上的跳线用来选择输入电源的来源。

图1.2给出了Nexys2开发平台的电源分布图。

输入电源总线驱动3.3伏的电源管理器。

一些设备要求2.5V,1.8V和1.2V的电源。

主电源由高效的开关管理器提供。

板上消耗的电流取决于板上FPGA的配置,时钟频率和外部的连接。

prom下载方式

Step by step 学习下载配置Xilinx之FPGA配合Mars-XC2S50-Core FPGA核心板,用图文方式向大家详细讲述如何下载配置Xilinx的FPGA。

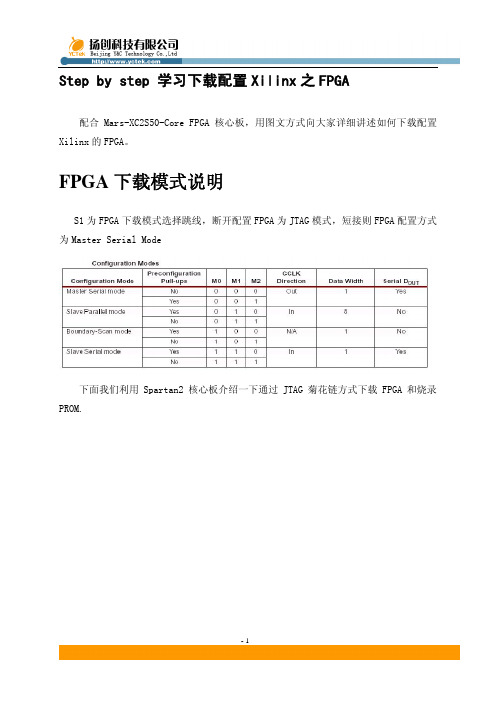

FPGA下载模式说明S1为FPGA下载模式选择跳线,断开配置FPGA为JTAG模式,短接则FPGA配置方式为Master Serial Mode下面我们利用Spartan2核心板介绍一下通过JTAG菊花链方式下载FPGA和烧录PROM.硬件跳线选择1. 跳线S1: 此时要求M0 M1 M2 = 100, 断开即可设置FPGA的下载方式为Boundary-scan mode。

2. 将Xilinx下载线和核心板上JTAG mode接口J2相连,连接到计算机并口。

3. 目标板上电。

软件操作一、产生PROM配置文件在烧写PROM之前,需要将ISE生成的*.bit文件转换成prom格式的文件才能下载Xilinx 专用的配置PROM中。

1. 启动iMPACT2. 出现下面画面选择Prepare Configuration Files,点击下一步。

3.出现如下界面,选择PROM File,点击下一步。

4.界面如下,选择PROM类型,和文件格式,填写生成文件名称路径,下一步5.指定使用的PROM类型,并添加,下一步。

6.下一步7点击Add File按钮。

8.选上需要转换的*.bit文件打开。

9.出现如下对话框,提示要不要添加另外的.bit文件。

选择否10界面如下,点击完成11.出现要不要现在生成配置文件,选择是,至此,PROM的文件已经生成。

12.OK.二.菊花链方式下载配置FPGA和PROM 1.打开iMPACT配置2.出现如下界面,选择Configure Device, 下一步。

3.选择Boundary-Scan Mode,下一步。

4.选自动监测扫描链,完成。

5.出现如下界面,检测到两个器件:xc2s50和xcf01s,并提示是否为每个器件添加配置文件。

一种基于SPI配置模式FPGA在线升级方案

• 37•的难度。

所以,应发挥导频实际应用性,加强对导频财务支出方面内容的研究,在分析该方面内容时应了解其资金的支出情况与运行情况,使用导频服用技术设计导频信号,进而可以确保导频财支出财务的有效性,此外,在校正信道标准时,应遵守互异性原则。

针对大规模天线系统来说,如果基站天线用户量增加,会导致用户获得信息速度带来阻碍。

因此,从获取信息的角度出发,控制对导频资金方面的投入。

如果开发导频的开销比用户的数量大很多,这会对用户获取信息带来阻碍。

因此,为了能够有效的减少导频的投入,应将已开发的导频资源功能发挥出来。

导频的内容主要包括设计信号、复用手段等内容,以下介绍判断信道互异性的两个标准:(1)第一,电路的判断。

其主要是针对硬件电路,应用多路方式,并采用耦合器与信道天线进行关联,确保信道线路的接收与发送工作可以有效的进行;(2)第二,校准与判断空间信号。

对校准的信息与数据进行计算与判断,进而达到对现代化数据与信息获取的目的。

3.2 5G网络大规模天线无线的理论传输方法实际上该技术是在广播与接入信道的基础上所设计出的一种传输性渠道,从理论的角度来看,通过对接入信道通的检测,可以满足容量的基本要求。

其中广播信道,可以采用污纸编码的方式达到目的。

随着天线和使用该系统数量的增加,难以实现对该系统的传输功能。

从理论角度通过对该系统进行分析与讨论,如果MIMO技术的天线数量最多时,为了能够保障其达到接近容量的目的,其上行应使用最大比进行合并,而下行可以使用MRT。

此外,如果使用规模大的天线时,能够减少上行和下行之间信息难度,但由于受到多种因素的影响,增加了其复杂性;因此,针对这一现象,应采用适当的解决方式,例如,采用空分多址等传输方式。

3.3 系统的资源配置该系统中,为了可以更好的提升资源利用率;因此,应合理的优化该系统资源,做好资源配置工作,为了能将该系统的优势作用发挥出来,应采用优化和分配资源的方式进行,这种方式属于一种较为高和较为简单的设计方案,以下笔者分析与探讨该系统中的MIMO技术的空域资源的实际分配情况得出以下结论:(1)采用统计空分复用的方式可有效降低MIMO技术的难度,并在其进行使用过程中用户分簇会产生一定的影响;(2)要实现将容量最大化的目的,可以合理的对信道信息进行统计,此外为了达到用户分簇的目的,可以采用统计信道信息和贪婪算法,井将一些存在相似信道的用户分配于同簇内;(3)由于相关工作人员对分簇方法的具体实施与其性能有着一定的影响,所以,其传输方法会对其性能产生极大影响;所以应适当的调整分族度量,可以使用弦距离代替,并指出分簇算法,以达到合理分配资源的目的;(4)5G大规模天线无线传输理论和技术,属于目前重要的研究题目,对该方面的研究虽已获得明显的效果,但是该技术在降低其复杂性的方面,还需要进行深入研究,并找出合理的应对措施,深入研究无线系统的资源分配方案的设计,进而推动该技术的可持续发展。

Xilinx_FPGA中文教程

Spartan-3E Starter Kit Board User GuideChapter 1: Introduction and OverviewChapter 2: Switches, Buttons, and KnobChapter 3: Clock SourcesChapter 4: FPGA Configuration OptionsChapter 5: Character LCD ScreenChapter 6: VGA Display PortChapter 7: RS-232 Serial PortsChapter 8: PS/2 Mouse/Keyboard PortChapter 9: Digital to Analog Converter (DAC)Chapter 10: Analog Capture CircuitChapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial FlashChapter 13: DDR SDRAMChapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion ConnectorsChapter 16: XC2C64A CoolRunner-II CPLDChapter 17: DS2432 1-Wire SHA-1 EEPROMChapter 1:Introduction and OverviewSpartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。

设备支持设备支持::Spartan-3E 、CoolRunner-II关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner™-II (XC2C64A-5VQ44C)与Platform Flash(XCF04S-VO20C)时钟时钟::50 MHz 晶体时钟振荡器存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器显示器: VGA 显示端口,16 字符- 2 线式 LCD电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。

IMPACT软件使用解读

IMPACT软件使用解读Xilinx IMPACT工具使用IMPACT5.4.1 iMPACT综述与基本操作1. iMPACT简介iMPACT支持4种下载模式:边界扫描,从串模式、SelectMap 模式以及Desktop配置模式。

从串模式是一种常用配置电路,可用USB口或并口完成配置。

SelectMap模式是一种并行配置模式,速度快,但需要使用多个信号管脚。

Desktop模式是一种高速配置模式,可配置FPGA、PROM以及SystemACE,但需要专用的硬件设备。

在实际中,由于边界扫描模式标准统一、设备简单,且可通过JTAG链路配置FPGA、CPLD以及PROM,使用最为广泛。

因此本节主要基于边界扫描模式来介绍IMPACT的使用方法。

当设计完成后,ISE调用BitGEN程序把布局布线后的.ncd文件转化成.bit文件,包括了配置数据和配置指令。

如果使用JTAG模式,可直接将.bit文件通过iMPACT文件配置到FPGA芯片中。

如果要用其它模式配置FPGA,则需要通过iMPACT进行格式转化,生成.mcs、.exo以及.hex等文件格式,表M对常用的配置文件进行比较和说明。

对于FPGA器件,iMPACT能够直接将.bit位流文件下载到芯片中,或者将其转换为PROM 器件的EXO/MCS文件格式,并下载到PROM 芯片中。

2. iMPACT用户界面有两种方法可以启动iMPACT软件,一种是在ISE过程管理区中,点击Generate Programming File前面的“+”号,再双击“Configure Device”,在ISE环境下运行;另一种是通过点击“开始程序ISE9.1 Accessories iMPACT”,在Windows环境下单独运行。

iMPACT的用户界面主要由File、Edit、View、Operations、Options、Output、Debug、Window、Help菜单栏和常用工具栏组成。

XilinxFPGA介绍

目前FPGA芯片仍是基于查找表技术的,但其概念和性能已经远远超出查找表技术的限制,并且整合了常用功能的硬核模块(如块RAM、时钟管理和DSP)。

图1-1所示为Xilinx公司FPGA的内部结构示意图(由于不同系列的应用场合不同,所以内部结构会有一定的调整),从中可以看出FPGA芯片主要由 6部分组成:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

图1-1 FPGA芯片的内部结构每个模块的功能如下:1.可编程输入输出单元(IOB)可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求,提供输入缓冲、输出驱动、接口电平转换、阻抗匹配以及延迟控制等功能,其一般示意结构如图1-2所示。

FPGA内的I/O按组分类,每组都能够独立地支持不同的I/O标准。

通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。

目前,I/O口的频率也越来越高,一些高端的FPGA 通过DDR寄存器技术可以支持高达2Gbps的数据速率。

外部输入信号可以通过IOB模块的存储单元输入到FPGA的内部,也可以直接输入FPGA 内部。

当外部输入信号经过IOB模块的存储单元输入到FPGA内部时,其保持时间(Hold Time)的要求可以降低,通常默认为0。

为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。

只有相同电气标准的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

2.可配置逻辑块(CLB)CLB是FPGA内的基本逻辑单元。

CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都包含一个可配置开关矩阵,此矩阵由4或6个输入、一些选型电路(多路复用器等)和触发器组成。

xilinx的prom配置经验

复位和上电复位1 在上电时,这器件要求VCCINT在精确的上升时间内,单调的上升到标准工作电压值。

2 如果电压没满足要求,这器件就不能执行合适的上电复位。

3 上电运行的顺序:先PROM的OE/RESET保持低电平,在配置开始以前要求电源能达到它们各自的POR(上电复位电压)门限,OE/RESET被定时释放后对稳定电源的应用有更多的余地。

4 在系统利用慢上升电源时,另外增加一个电源监控电路能被用做延时配置直到系统电源达到最小的操作电源在OE/RESET一直为低电平。

5 当OE/RESET被释放,INIT就被上拉为高电平,允许FPGA有次序的配置。

6 如果电压低于POR门限时,PROM复位,OE/RESET再为低,直到达到POR 门限。

7 对于PROM电压正常时,只要OE/RESET=0或CE=1,复位就开始,当地址计数器复位时,CEO输出高电平,其它的数据输出脚为高阻态。

8 XCFXXS PROM 只要求OE/RESET被释放以前,VCCINT上升到POR门限就行了。

9 XFCXXP PROM 在OE/RESET被释放以前,不但要求VCCINT上升到POR 门限,而且还要求VCCO达到被推荐的正常工作电压。

配置1 当JTAG配置指令在PROM里被更新时,PROM暂时给CF一个低电平,接着就给CF一个高电平。

结合CF脚在外部加了上拉电阻,此时在CF脚输出一个‘高-低-高’的脉冲个FPGA的PROGRAM 脚。

此次FPGA就依次的开始配置。

2 在CF脚外部必须加个上拉电阻,防止CF脚产生一个浮动到低电平的值而引起复位。

3 当XCFXXP的PROM存有多重设计文件时,CF脚必须连接到FPGA的PROGRAM_B脚去保证重新安放那些被选中的设计文件(配置有效)。

4 对于XCFXXS的PROM,CF脚只是个输出,如果没有由于的功能的话,可以不用连接FPGA。

在SPARTAN FPGA系列中,INIT_B脚使用内部下拉有典型的补偿,外部上拉电阻在INIT_B脚时,能产生一个不明确的信号给PROM的OE/RESET脚,鉴别一个错误的配置,CRC错误在INIT_B脚。

ISE软件使用说明

说明这个说明主要介绍了使用开发板可能使用到的3个工具,主要以串口功能的实现作为例子,讲述了ISE, Plantform和EDK的使用方法以及操作的基本流程。

ISE的使用一.启动Xilinx ISE:开始Æ所有程序ÆXilinx ISE 7.1iÆProject Navigator二.新建/打开一个工程:如果已经有了工程,则在FileÆOpen Project弹出的对话框里面选择你的工程。

如果没有合适的工程就需要通过FileÆNew Project来新建一个工程。

具体操作步骤如下:分别在Project Name和Project Location里面填写您想要创建的工程的名称和路径。

在Top-Level Module Type的下拉菜单里面选择您的工程的顶层模块的类型。

本次串口通信的实验的顶层为原理图,所以选择Schematic。

然后点击下一步:在这个对话框的上半部分选择您使用的芯片的族(Spartan3),型号(xc3s400),封装(pq208)和速度(-4)。

下面选择您要使用编译和综合的软件,建议使用ISE自带的软件,一是使用简便,二是Xilinx公司对自己的FPGA了解程度比第三方要高很多,所以使用Xilinx公司自己的软件有的时候会获得意想不到的收获。

具体参数选择如图,然后单击下一步:在这个对话框里面新建工程里面的文件,这步也可以放到后面来实现,这里我们先选择下一步:这一步用来添加已经存在的文件,同样,我们在后面实现这步。

点击下一步:在最后这个对话框里面显示了我们即将建立的工程的详细信息,确认无误以后点击完成,ISE将为您创建一个名字为uart_test的工程:三.为刚创建的工程添加源文件:1.添加已经存在的源文件:选中屏幕右上的xc3s400-4pq208,单击ProjectÆAdd Source,在弹出的对话框里面选择您已经存在的程序文件(.v .vhd)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx FPGA的PROM配置

作者:枪手2007年8月16号

1.建立工程,假如VHDL,UCF文件,综合,执行。

2.生成PROM文件。

在图中选择Prepare a PROM file,然后点next.

3,

在上图中做图所显示的选择,点NEXT

4

在上图中选择所用开发板上的PROM,SP3E用XCF04S,点ADD,添加到列表中。

然后点next,出现file generation summary!

5.

确定是不是和所选择的一致,点finish。

6.

出现上面对话框的时候,点OK。

7.

在上面图中,选择bit文件。

8.

在出现上面对话框的时候,点NO。

9.然后,出现下面对话框,点OK。

10.在左边的impact modes 中,点Generate file

11.生成PROM FILE 文件成功。

12.在左边flows下,选择boundary scan。

13.点boundary scan后,出现下面界面。

14.点鼠标右键,选择initialize chain

15.出现下面下面界面。

对于XC3S500E,点cancel。

16.对XCF04S,选择刚才生成的led_flow.mcs文件.

17,对第三个,点cancel.

18.上面选择后,出现下面界面,在XCF04S,点右键,出现一个菜单,选择Program.

19,点PROGRAM后,出现如下界面,按图中选择各项.

20,点OK 后,开始配置,

21.成功界面如下,然后,拨掉JTAG,关掉电源,过一会再上电.。