makefile 中 .dep 用法

makefile中的特殊符号及关键字

makefile中的特殊符号及关键字1.常见⾃动变量和含义* :表⽰⽬标⽂件的名称,不包含⽬标⽂件的扩展名。

+ :表⽰所有的依赖⽂件,这些依赖⽂件之间以空格分开,按照出现的先后为顺序,其中可能包含重复的依赖⽂件。

< :表⽰依赖项中第⼀个依赖⽂件的名称:依赖项中,所有⽬标⽂件时间戳晚的⽂件(表⽰修改过),依赖⽂件间以空格分开@ :⽬标项中⽬标⽂件的名称^ :依赖项中,所有不重复的依赖⽂件,以空格分开。

2.预定义变量Makefile中常⽤的变量及含义AR⽣成静态库库⽂件的程序名称arAS汇编编译器的名称asCC C语⾔编译器的名称ccCPP C语⾔预编译器的名称$(CC) -ECXX C++语⾔编译器的名称g++FC FORTRAN语⾔编译器的名称f77RM删除⽂件程序的名称rm -fARFLAGS⽣成静态库库⽂件程序的选项⽆默认值ASFLAGS汇编语⾔编译器的编译选项⽆默认值CFLAGS C语⾔编译器的编译选项⽆默认值CPPFLAGS C语⾔预编译器的编译选项⽆默认值CXXFLAGS C++语⾔编译器的编译选项⽆默认值FFLAGS FORTRAN语⾔编译器的编译选项⽆默认值3.设置搜索路径 指定需要搜索的⽬录, make 会⾃动找到指定⽂件的⽬录并添加到⽂件上。

VPATH = path1:path2:...4.递归make对于规模⽐较⼤的程序,需要多个⼈在多个⽬录下进⾏开发。

如果只⽤⼀个 Makefile 来维护就会⽐较⿇烦,因此可以在每个⽬录下建⽴⾃⼰的 Makefile ,然后在总控 Makefile 中调⽤⼦⽬录的 Makefile ⽂件。

⽬录结构如下:.├── add│├── add_float.c│├── add.h│├── add_int.c│└── Makefile├── main.c├── Makefile└── sub├── Makefile├── sub_float.c├── sub.h└── sub_int.c1.递归调⽤的⽅式add:cd add && $(MAKE)它等价于add:$(MAKE) -C add2.总控MakefileCC = gccCFLAGS = -O2TARGET = cacuexport OBJSDIR = $(shell pwd)/objs$(TARGET):$(OBJSDIR) main.o$(MAKE) -C add$(MAKE) -C sub$(CC) -o $(TARGET) $(OBJSDIR)/*.o$(OBJSDIR):mkdir -p $@main.o:%.o:%.c$(CC) -c $< -o $(OBJSDIR)/$@ $(CFLAGS) -Iadd -Isubclean:-$(RM) $(TARGET)-$(RM) $(OBJSDIR)/*.o如果总控 Makefile 中的⼀些变量需要传递给下层的 Makefile,可以使⽤ export 命令。

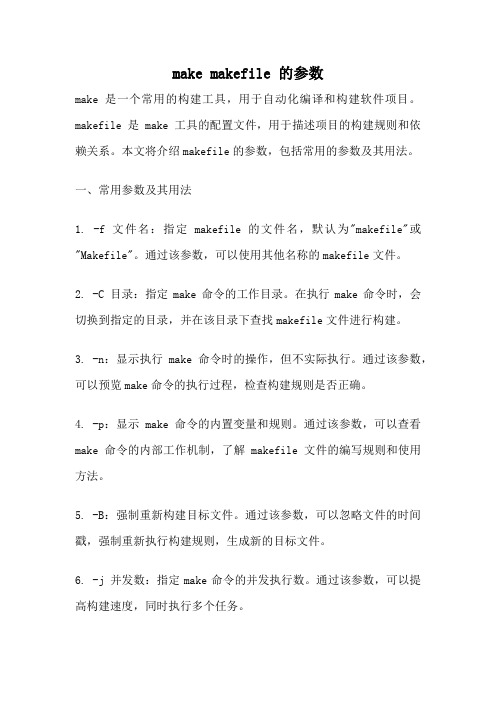

make makefile 的参数

make makefile 的参数make是一个常用的构建工具,用于自动化编译和构建软件项目。

makefile是make工具的配置文件,用于描述项目的构建规则和依赖关系。

本文将介绍makefile的参数,包括常用的参数及其用法。

一、常用参数及其用法1. -f 文件名:指定makefile的文件名,默认为"makefile"或"Makefile"。

通过该参数,可以使用其他名称的makefile文件。

2. -C 目录:指定make命令的工作目录。

在执行make命令时,会切换到指定的目录,并在该目录下查找makefile文件进行构建。

3. -n:显示执行make命令时的操作,但不实际执行。

通过该参数,可以预览make命令的执行过程,检查构建规则是否正确。

4. -p:显示make命令的内置变量和规则。

通过该参数,可以查看make命令的内部工作机制,了解makefile文件的编写规则和使用方法。

5. -B:强制重新构建目标文件。

通过该参数,可以忽略文件的时间戳,强制重新执行构建规则,生成新的目标文件。

6. -j 并发数:指定make命令的并发执行数。

通过该参数,可以提高构建速度,同时执行多个任务。

7. -s:静默模式,不显示执行的命令。

通过该参数,可以减少输出信息,使构建过程更加清晰。

二、makefile的构建规则makefile由一系列构建规则组成,每个规则定义了目标文件、依赖文件和构建命令。

make命令根据构建规则,自动判断需要更新的文件,并执行相应的构建命令。

构建规则的基本格式如下:目标文件: 依赖文件构建命令其中,目标文件是要生成的文件,依赖文件是目标文件依赖的文件,构建命令是生成目标文件的命令。

构建规则中的目标文件和依赖文件可以是文件名,也可以是变量。

通过使用变量,可以提高makefile的可维护性和灵活性。

构建命令可以是任意的Shell命令,包括编译、链接、拷贝等操作。

c语言makefile编写规则(一)

c语言makefile编写规则(一)C语言Makefile编写规则1. Makefile介绍Makefile是一种文件,其中包含了一组规则(rules)用于编译和构建项目。

它的作用是告诉系统如何编译代码,生成可执行文件。

2. Makefile规则基本结构Makefile规则由以下几部分组成:目标(Target)目标是一个文件,可以是源代码文件、中间文件或最终生成的可执行文件。

依赖(Dependencies)依赖指的是生成目标所需要的文件或其他目标。

当某个依赖文件发生变化时,目标就需要重新生成。

命令(Commands)命令是指执行编译、链接等操作的具体命令。

当目标需要重新生成时,Makefile会执行相应的命令。

规则示例以下是一个简单的示例,展示了一个C语言源文件的编译过程:target: dependenciescommand其中, - target表示目标文件; - dependencies表示生成目标所需要的文件或其他目标; - command表示具体的编译命令。

例如,假设有一个名为`的C语言源文件,我们想要生成一个名为hello`的可执行文件。

那么对应的Makefile规则可以定义如下:hello:gcc -o hello3. Makefile变量Makefile中还可以定义变量,以提高代码的可读性和重用性。

变量可以存储命令、文件名、路径等信息。

变量定义变量的定义采用变量名 = 值的方式进行,例如:CC = gcc其中,CC是变量名,gcc是变量的值。

变量引用使用变量时,需要在变量名前加$符号进行引用。

例如,使用上述定义的CC变量可以这样写:$(CC) -o hello4. Makefile示例以下是一个完整的Makefile示例,展示了多个目标之间的依赖关系和命令定义:CC = gccall: hellohello:$(CC) -o hello:$(CC) -cclean:rm -f hello在上述示例中,共定义了3个目标:all、hello和。

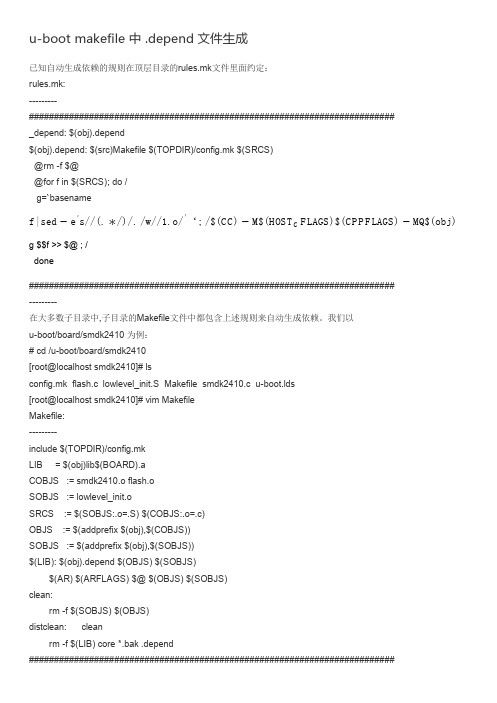

u-boot makefile中.depend 文件生成

u-boot makefile 中 .depend 文件生成已知自动生成依赖的规则在顶层目录的rules.mk 文件里面约定:rules.mk:#########################################################################_depend: $(obj).depend$(obj).depend: $(src)Makefile $(TOPDIR)/config.mk $(SRCS)@rm f $@@for f in $(SRCS); do /g=`basenameg $$f >> $@ ; /done#########################################################################在大多数子目录中,子目录的Makefile 文件中都包含上述规则来自动生成依赖。

我们以uboot/board/smdk2410 为例:# cd /uboot/board/smdk2410[root@localhost smdk2410]# lsconfig.mk flash.c lowlevel_init.S Makefile smdk2410.c uboot.lds[root@localhost smdk2410]# vim MakefileMakefile:include $(TOPDIR)/config.mkLIB = $(obj)lib$(BOARD).aCOBJS := smdk2410.o flash.oSOBJS := lowlevel_init.oSRCS := $(SOBJS:.o=.S) $(COBJS:.o=.c)OBJS := $(addprefix $(obj),$(COBJS))SOBJS := $(addprefix $(obj),$(SOBJS))$(LIB): $(obj).depend $(OBJS) $(SOBJS)$(AR) $(ARFLAGS) $@ $(OBJS) $(SOBJS)clean:rm f $(SOBJS) $(OBJS)distclean: clean rm f $(LIB) core *.bak .depend#########################################################################f|sed −s//(.∗/)/./w//1.o ‘;/$(CC)−M$(HOS FLAGS)$(CPPFLAGS)−MQ$(obj)e ′/′T C# defines $(obj).depend targetinclude $(SRCTREE)/rules.mksinclude $(obj).depend#########################################################################已知:$(obj)实际上为空,所以上面任何文件加上这个前缀实际上都没有用,表示在当前目录下面。

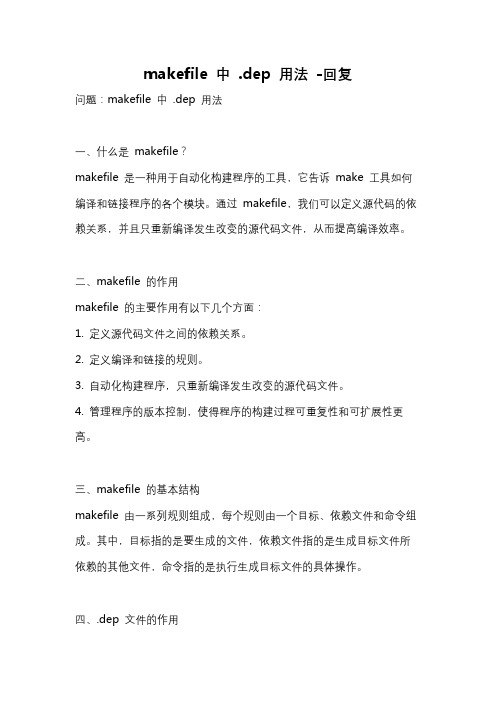

makefile 中 .dep 用法 -回复

makefile 中 .dep 用法-回复问题:makefile 中 .dep 用法一、什么是makefile?makefile 是一种用于自动化构建程序的工具,它告诉make 工具如何编译和链接程序的各个模块。

通过makefile,我们可以定义源代码的依赖关系,并且只重新编译发生改变的源代码文件,从而提高编译效率。

二、makefile 的作用makefile 的主要作用有以下几个方面:1. 定义源代码文件之间的依赖关系。

2. 定义编译和链接的规则。

3. 自动化构建程序,只重新编译发生改变的源代码文件。

4. 管理程序的版本控制,使得程序的构建过程可重复性和可扩展性更高。

三、makefile 的基本结构makefile 由一系列规则组成,每个规则由一个目标、依赖文件和命令组成。

其中,目标指的是要生成的文件,依赖文件指的是生成目标文件所依赖的其他文件,命令指的是执行生成目标文件的具体操作。

四、.dep 文件的作用.dep 文件是makefile 中一个重要的文件,它用于记录源代码文件之间的依赖关系。

在makefile 构建程序时,会根据 .dep 文件中的内容判断哪些源代码文件需要重新编译。

五、.dep 文件的生成过程1. 定义 .dep 依赖文件的生成规则。

常用的规则有以下两种:.dep: .cpp(CPP) (CPP_FLAGS) -MM < -MF @或.cpp.dep:(CPP) (CPP_FLAGS) -MM < -MF @2. 定义 .dep 文件的依赖规则。

sources := (wildcard *.cpp)deps := (patsubst .cpp,.dep,(sources))all: (deps)(deps): .dep: .cppinclude (deps)3. 执行makefile 生成 .dep 文件。

在命令行中执行`make` 命令,make 工具会根据 .dep 文件的规则和源代码文件的依赖关系生成 .dep 文件。

makefile 语句解释

makefile 语句解释Makefile语句解释Makefile是一种用于自动化构建和管理软件项目的工具。

它包含一系列规则和指令,用于描述项目中的文件依赖关系和构建过程。

在这篇文章中,我将解释一些常见的Makefile语句。

1. `target: dependencies`这是最基本的Makefile规则语句。

它指定了一个目标(target),以及该目标所依赖的文件(dependencies)。

当目标的依赖文件发生变化时,Make工具将会执行后续的指令来更新目标。

2. `command`这是Makefile中的指令,用于执行具体的操作。

指令可以是任何可执行的命令,比如编译程序、复制文件、运行脚本等。

在Makefile中,每行指令都需要以一个Tab键开头。

3. `.PHONY: target`这是一个特殊的目标声明语句。

它告诉Make工具,目标并不是一个真实的文件名,而是一个伪目标(phony target)。

伪目标通常用于定义一些特殊的操作,比如清理文件、运行测试等。

4. `$(variable_name)`这是一个变量引用语句。

Makefile中可以定义变量,以便在后续的指令中使用。

变量可以包含字符串、文件名、目录名等信息。

$(variable_name)会被替换成对应变量的值。

5. `ifdef variable_name`这是一个条件判断语句,用于检查变量是否被定义。

如果变量已被定义,则执行后续的指令;否则跳过。

6. `$(wildcard pattern)`这是一个通配符表达式,用于匹配文件名。

这个表达式可以用于查找满足特定条件的文件,比如所有以.c结尾的文件,或者某个目录下的所有文件。

7. `ifeq ($(variable_name), value)`这是一个条件判断语句,用于检查变量的值是否等于某个特定的值。

根据判断结果,可以执行不同的指令或者设置不同的变量值。

这些是一些常用的Makefile语句和语法。

makefile文件语法

makefile文件语法Makefile是一种用于自动化构建过程的工具,它使用一种特定的语法来定义构建规则和依赖关系。

下面是一些Makefile的基本语法规则:1. 目标(Target):目标是指要构建的程序或文件。

它通常以冒号(:)开头,后面跟着一个或多个依赖项(dependencies)。

```makefiletarget: dependenciescommands```2. 依赖项(Dependencies):依赖项是指要构建目标所必需的文件或目标。

在Makefile中,依赖项以空格分隔。

3. 命令(Commands):命令是指在构建目标时执行的命令行指令。

这些命令可以是编译、链接或其他任何必要的操作。

4. 变量(Variables):Makefile允许使用变量来存储值,以便在构建过程中重复使用。

变量以符号开头,后面跟着变量名。

```makefileVAR = value```5. 模式规则(Pattern Rules):模式规则允许根据文件模式匹配来构建目标。

它们使用通配符来匹配文件名,并在匹配的文件上执行相应的命令。

```makefiletargets : patterncommands```6. 条件语句(Conditionals):Makefile支持条件语句,可以根据条件执行不同的命令或规则。

条件使用ifdef、ifndef、ifeq等关键字定义。

7. 注释(Comments):Makefile使用井号()作为注释标记,任何在该符号之后的内容都会被视为注释,并被忽略。

8. 自动变量(Automatic Variables):Makefile提供了一些自动变量,可以在命令中使用,以获取有关目标、依赖项或文件名的信息。

例如,$表示当前目标,$<表示第一个依赖项等。

这些是Makefile的一些基本语法规则,但还有更多高级特性和用法,可以参考Make工具的文档或相关教程进行深入学习。

makefile debug编译

makefile debug编译摘要:1.编译的概述2.Makefile 的作用3.debug 编译的流程4.Makefile debug 编译的具体步骤5.debug 编译的优点与局限性正文:编译的概述编译是将源代码转换为目标代码的过程,通常由编译器完成。

在软件开发过程中,编译是一个重要的环节,用于检查代码的正确性和实现软件的功能。

根据不同的需求,编译过程可以分为多种类型,如调试编译、优化编译等。

本文将介绍一种常见的编译类型:debug 编译,并说明如何使用Makefile 进行debug 编译。

Makefile 的作用Makefile 是一个文本文件,用于描述软件项目的编译过程。

它包含了编译所需的命令、依赖关系和编译选项等信息。

通过Makefile,开发者可以方便地管理编译过程,自动化地完成源代码到目标代码的转换。

在debug 编译中,Makefile 可以帮助开发者配置编译选项,以便于调试代码。

debug 编译的流程debug 编译的流程通常包括以下几个步骤:1.配置编译选项:根据开发者的需求,为编译器添加调试相关的选项,如-g(生成调试信息)、-O0(不优化)等。

2.编译源代码:使用编译器,按照Makefile 中指定的编译选项,编译源代码。

3.生成目标代码:编译成功后,会生成目标代码(如可执行文件、库文件等)。

4.运行调试器:使用调试器运行目标代码,以便于开发者检查代码的运行状态和调试错误。

Makefile debug 编译的具体步骤使用Makefile 进行debug 编译的具体步骤如下:1.创建Makefile:在项目根目录下创建一个名为Makefile 的文本文件。

2.编写Makefile:在Makefile 中,编写编译规则和依赖关系。

例如:```all: main.o -o mainmain.o: main.ct$(CC) $(CFLAGS) -c main.cmain: main.ot$(CC) $(LDFLAGS) -o main main.o```在这个例子中,我们使用GCC 编译器(CC)进行编译,并添加了-g 和-O0 选项,用于生成调试信息和不优化目标代码。

makefile debug编译

makefile debug编译【最新版】目录1.Makefile 概述2.debug 编译的含义3.Makefile 中的 debug 编译4.如何进行 Makefile debug 编译5.总结正文1.Makefile 概述Makefile 是一种用于自动化构建和编译软件的脚本文件,通常用于Unix 和类 Unix 系统中。

它由一系列的规则和指令组成,用于指定源代码文件、编译器、链接器和其他工具,以便构建可执行文件。

2.debug 编译的含义debug 编译是一种编译方式,用于在编译过程中添加调试信息,以便于开发者在运行程序时能够追踪代码的执行过程,找出程序中的错误和问题。

3.Makefile 中的 debug 编译在 Makefile 中,要进行 debug 编译,需要使用一定的指令和规则。

通常,需要使用“CFLAGS”变量来指定编译器选项,其中包括添加调试信息的选项,例如“-g”。

同时,还需要使用“DEBUG”变量来指定是否进行debug 编译,例如,“DEBUG=on”表示进行 debug 编译,“DEBUG=off”表示不进行 debug 编译。

4.如何进行 Makefile debug 编译具体进行 Makefile debug 编译的步骤如下:(1) 在 Makefile 中设置“DEBUG”变量为“on”,例如,“DEBUG=on”;(2) 在 Makefile 中设置“CFLAGS”变量,添加调试选项“-g”,例如,“CFLAGS=-g”;(3) 保存 Makefile 文件;(4) 在命令行中,进入到 Makefile 所在的目录;(5) 执行“make”命令,进行编译。

这样,编译器就会在编译过程中添加调试信息,生成的可执行文件可以在运行时进行调试。

5.总结Makefile 是一种重要的构建工具,能够帮助开发者自动化构建和编译软件。

debug 编译是开发过程中常用的一种编译方式,可以帮助开发者找出程序中的错误和问题。

makefile写法

makefile写法Makefile 是代码构建和自动化构建的重要工具,它可以帮助我们高效、准确地管理和构建程序。

在本文中,我将和大家分享几种常见的Makefile 写法,以及一些有用的技巧和注意事项。

1. Makefile 的基本结构Makefile 中包含了以下基本结构:```target: dependencies<tab> command```其中,target 表示目标文件或目标任务名称;dependencies 表示该目标文件或任务所依赖的文件或任务;command 表示需要执行的命令。

比如,下面是一个简单的 Makefile 例子:```all: testtest: main.o func.o<tab> gcc main.o func.o -o testmain.o: main.c<tab> gcc -c main.c -o main.ofunc.o: func.c func.h<tab> gcc -c func.c -o func.o```其中,目标文件 all 是 Makefile 的默认目标,执行 make 命令时会自动执行 all 目标中所列出的任务。

在本例中,all 的唯一任务是test。

test 任务需要依赖 main.o 和 func.o,如果这两个文件不被更新,则 test 任务不会被重新构建。

2. Makefile 的变量在 Makefile 中,我们可以定义变量来方便地管理代码中的重复部分。

变量可以在任何位置使用,使得代码更加清晰易读,同时也方便了维护。

变量的定义格式是:```变量名 = 值```例如:```CC = gccCFLAGS = -Wall -g```在 Makefile 内使用变量的格式是 $+变量名。

例如:```all: testtest: main.o func.o<tab> $(CC) main.o func.o -o test $(CFLAGS)main.o: main.c<tab> $(CC) -c main.c -o main.o $(CFLAGS)func.o: func.c func.h<tab> $(CC) -c func.c -o func.o $(CFLAGS)```在本例中,我们定义了两个变量,CC 和 CFLAGS。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

makefile 中 .dep 用法

Makefile是一种常用的自动化构建工具,用于管理软件项目的编译和链接过程。

在Makefile中,.dep是一个特殊的文件,用于记录编译过程中生成的目标文件、依赖关系等信息。

下面介绍Makefile

中.dep的用法。

一、.dep文件的作用

.dep文件是Makefile自动生成的,用于记录编译过程中的依赖关系和目标文件信息。

在Makefile中,目标文件(target)依赖于源文件(source),当源文件发生变化时,目标文件需要重新编

译。

.dep文件记录了这些依赖关系,方便后续的构建过程。

二、.dep文件的生成

Makefile会根据源文件和目标文件的依赖关系自动生成.dep文件。

当源文件发生变化时,Makefile会重新编译目标文件,并生成新的.dep文件。

在Makefile中,可以使用$(wildcard)函数和$(if)函数来检查源文件的变动情况,并生成相应的.dep文件。

三、.dep文件的用法

在Makefile中,可以使用$(.FORCE)规则来强制执行某些目标文件的构建,并自动生成.dep文件。

$(.FORCE)规则会在目标文件未被构建或依赖的.dep文件不存在时触发执行。

通过使用$(.FORCE)规则,可以确保目标文件的正确构建,并自动生成所需的.dep文件。

四、注意事项

在使用.dep文件时,需要注意以下几点:

1..dep文件只记录了源文件和目标文件的依赖关系,不包含具体的编译指令。

Makefile会根据源文件和目标文件的依赖关系自动生成编译指令。

2.在使用.dep文件时,需要确保源文件的变动会被正确检测到,否则.dep文件可能不准确。

可以使用$(wildcard)函数和$(if)函数来检测源文件的变动情况。

3.在Makefile中使用$(.FORCE)规则时,需要确保目标文件的构建顺序正确,否则可能会导致构建失败。

综上所述,.dep文件是Makefile中一个重要的工具,用于记录编译过程中的依赖关系和目标文件信息。

通过正确使用.dep文件,可以方便地管理软件项目的构建过程,提高构建效率和质量。