哈工大-电工电子实验-EDA实验报告

EDA实验报告正文

实验一单级放大电路的设计与仿真一、实验目的1.掌握放大电路静态工作点的调整与测试方法;2.掌握放大电路动态参数的测试方法;3.观察动态工作点的选择对输出波形及放大倍数的影响。

二、实验要求1.设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz(峰值10mV) ,负载电阻5.1kΩ,电压增益大于50。

2.调节电路静态工作点(调节偏置电阻),观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3.调节电路静态工作点(调节偏置电阻),使电路输出信号不失真,并且幅度最大。

在此状态下测试:①电路静态工作点值;r、ce r值;②三极管的输入、输出特性曲线和 、be③电路的输入电阻、输出电阻和电压增益;f、H f值。

④电路的频率响应曲线和L三、实验步骤1.单级放大电路的原理图:2.a.电路的饱和失真:静态工作点参数:图表3 饱和失真时静态工作点参数数据分析:Ib=12.90259uA Ic=2.07754mA Uce=0.20717V此时电位器为0%,基极静态电流过大而导致三极管达到饱和,使得电路出现失真。

b.电路的截止失真:图表4 截止失真时输出电压波形图静态工作点参数:图表5 截止失真时静态工作点参数数据分析:Ib=3.87579uA Ic=834.27745uA Uce=6.07513V此时电位器为100%,使得基极电位减小,三极管截止导致电路出现失真。

c.电路的最大不失真输出:图表6 最大不失真时输出电压波形图静态工作点参数:图表7 最大不失真时输出时静态工作点参数数据分析:Ube=0.64415V IC=1.87602mA IB=9.05731uA Uce=1.23723V β=207 此时电位器为20%3.a.三极管的输入特性:图表8 输入特性测试电路图表9 最大不失真时输入特性曲线从上图数据可以得出rbe=2.8353kΩb.三极管的输出特性:电路图及曲线:图表10 输出特性测试电路图表11 最大不失真时输出特性曲线从上图数据可以得出rce=10.793kΩ4.输入电阻的测量:图表12 输入电阻测量电路及数据从上图数据可以得出测试输入电流i=3.864uA 电阻Ri=2.588kΩ理论输入电阻Ri=2.483 kΩ误差4.1%5.输出电阻的测量:图表13 输出电阻测量电路及数据从上图数据可以得出测试输出电阻Ro=2.097kΩ理论输出电阻Ro=2.030 kΩ误差3.2%6.电压增益:图表14 电压增益测量电路及数据Au=110.557.电路的频率特性:图表15 波特图及数据最大输出增益41.25dB图表15 波特图及数据fL=229Hz fH=14.470MHz四、实验小结从以上测量的数据与理论计算值比较可以发现存在一定的误差,误差产生的原因可能包括:a.本次试验中的器件均选用实际器件,它们自身存在随机误差,例如:实验所用三极管的输出特性曲线放大区并非理想的水平平行线,而是发散的,只就导致正常放大的波形出现不对称行,仿佛截止失真。

eda技术实验报告

EDA技术实验报告1. 背景介绍EDA(Exploratory Data Analysis)是指探索性数据分析,是数据科学和机器学习中一项重要的任务。

通过EDA技术,我们可以对数据集进行可视化和统计分析,从而深入了解数据的特征和结构,为后续的数据处理和建模提供指导。

2. 实验目的本实验旨在通过使用EDA技术来分析一个给定的数据集,并从中获取有价值的信息。

通过实践,我们将深入了解EDA技术的应用和优势。

3. 实验步骤步骤1:导入数据首先,我们需要将实验所需的数据导入到Python的数据分析库中。

我们可以使用pandas库读取数据集,并将其存储为DataFrame对象,以便后续的分析和处理。

import pandas as pd# 读取数据集data = pd.read_csv('data.csv')步骤2:数据概览在进行数据分析之前,我们先要对数据进行整体的了解。

我们可以通过以下几个步骤来获取数据的概览信息:1.查看数据的前几行,了解数据的结构和格式。

data.head()2.查看数据的基本统计信息,包括均值、标准差、最小值、最大值等。

data.describe()3.检查数据中是否存在缺失值或异常值。

data.isnull().sum()步骤3:数据可视化EDA技术的核心之一是数据可视化。

通过可视化数据,我们可以更直观地理解数据的分布和关系。

下面是几种常用的数据可视化方法:1.直方图:用于展示数值型数据的分布情况,可以帮助我们了解数据的集中趋势和离散程度。

data['column'].plot.hist()2.散点图:用于展示两个数值型变量之间的关系,可以帮助我们发现数据的相关性。

data.plot.scatter(x='column1', y='column2')3.条形图:用于展示类别型数据的分布情况,可以帮助我们比较不同类别之间的差异。

EDA实验报告(12份).pdf

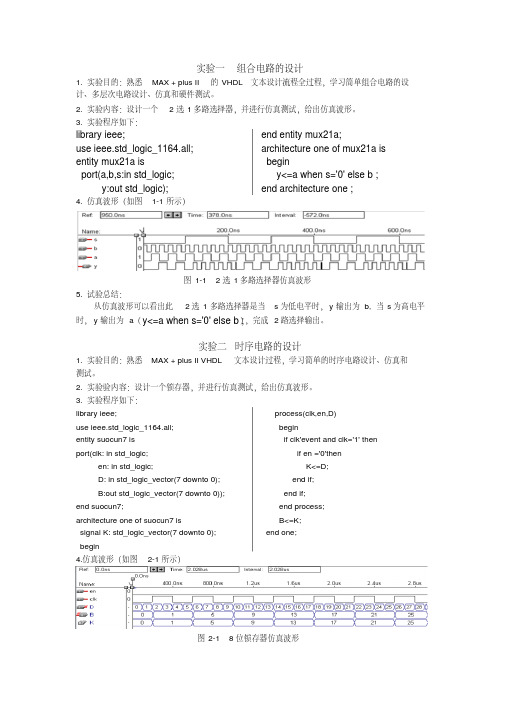

实验一组合电路的设计1. 实验目的:熟悉MAX + plus II 的VHDL 文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

2. 实验内容:设计一个2选1多路选择器,并进行仿真测试,给出仿真波形。

3. 实验程序如下:library ieee;use ieee.std_logic_1164.all; entity mux21a isport(a,b,s:in std_logic;y:out std_logic); end entity mux21a; architecture one of mux21a is beginy<=a when s='0' else b ; end architecture one ;4. 仿真波形(如图1-1所示)图1-1 2选1多路选择器仿真波形5. 试验总结:从仿真波形可以看出此2选1多路选择器是当s为低电平时,y输出为b, 当s为高电平时,y输出为a(y<=a when s='0' else b ;),完成2路选择输出。

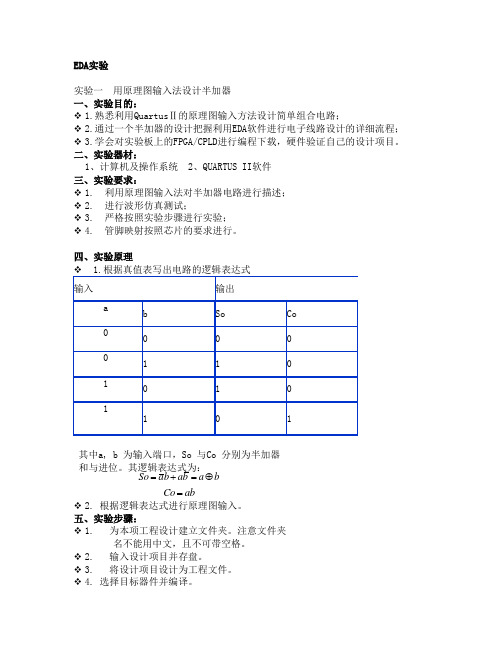

实验二时序电路的设计1. 实验目的:熟悉MAX + plus II VHDL文本设计过程,学习简单的时序电路设计、仿真和测试。

2. 实验验内容:设计一个锁存器,并进行仿真测试,给出仿真波形。

3. 实验程序如下:library ieee;use ieee.std_logic_1164.all;entity suocun7 isport(clk: in std_logic;en: in std_logic;D: in std_logic_vector(7 downto 0);B:out std_logic_vector(7 downto 0)); end suocun7;architecture one of suocun7 issignal K: std_logic_vector(7 downto 0); beginprocess(clk,en,D)beginif clk'event and clk='1' thenif en ='0'thenK<=D;end if;end if;end process;B<=K;end one;4.仿真波形(如图2-1所示)图2-1 8位锁存器仿真波形此程序完成的是一个8位锁存器,当时钟上升沿到来(clk'event and clk='1')、使能端为低电平(en ='0')时,输出为时钟上升沿时的前一个数,从仿真波形看,实现了此功能。

EDA实验报告完结版

EDA实验报告完结版一、实验目的本次 EDA 实验的主要目的是通过实际操作和设计,深入理解和掌握电子设计自动化(EDA)技术的基本原理和应用。

具体而言,包括熟悉 EDA 工具的使用方法,学会运用硬件描述语言(HDL)进行逻辑电路的设计与描述,以及通过综合、仿真和实现等流程,将设计转化为实际的硬件电路,并对其性能进行评估和优化。

二、实验环境本次实验所使用的 EDA 工具为_____,该工具提供了丰富的功能模块和强大的设计支持,包括原理图编辑、HDL 代码编写、综合、仿真和下载等。

实验所使用的硬件平台为_____开发板,其具备多种接口和资源,便于对设计的电路进行实际验证和测试。

三、实验内容1、基本逻辑门电路的设计与实现使用 HDL 语言(如 Verilog 或 VHDL)设计常见的基本逻辑门电路,如与门、或门、非门等。

通过编写代码,对逻辑门的输入输出关系进行描述,并进行综合和仿真,验证设计的正确性。

2、组合逻辑电路的设计与实现设计并实现较为复杂的组合逻辑电路,如加法器、减法器、编码器、译码器等。

运用 HDL 语言描述电路的功能,进行综合和仿真,确保电路在各种输入情况下的输出结果符合预期。

3、时序逻辑电路的设计与实现设计常见的时序逻辑电路,如计数器、寄存器、移位寄存器等。

在设计过程中,考虑时钟信号、同步复位和异步复位等因素,通过仿真验证时序逻辑的正确性,并对电路的性能进行分析。

4、有限状态机(FSM)的设计与实现设计一个有限状态机,实现特定的功能,如交通信号灯控制器、数字密码锁等。

明确状态转移条件和输出逻辑,通过编写 HDL 代码实现状态机,并进行综合和仿真,验证其功能的准确性。

5、综合与优化对设计的电路进行综合,生成门级网表,并通过优化工具对电路进行面积、速度等方面的优化,以满足特定的设计要求。

6、硬件实现与测试将综合后的设计下载到硬件开发板上,通过实际的输入输出信号,对电路的功能进行测试和验证。

观察电路在实际运行中的表现,对出现的问题进行分析和解决。

EDA实验报告

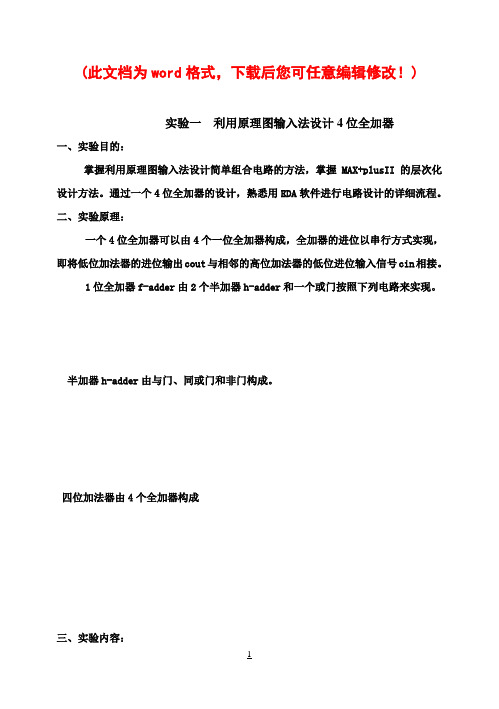

EDA 实验实验一 用原理图输入法设计半加器一、实验目的:1.熟悉利用Quartus Ⅱ的原理图输入方法设计简单组合电路;2.通过一个半加器的设计把握利用EDA 软件进行电子线路设计的详细流程;3.学会对实验板上的FPGA/CPLD 进行编程下载,硬件验证自己的设计项目。

二、实验器材:1、计算机及操作系统2、QUARTUS II 软件三、实验要求:1. 利用原理图输入法对半加器电路进行描述;2. 进行波形仿真测试;3. 严格按照实验步骤进行实验;4. 管脚映射按照芯片的要求进行。

四、实验原理其中a, b 为输入端口,So 与Co 分别为半加器和与进位。

其逻辑表达式为:2. 根据逻辑表达式进行原理图输入。

五、实验步骤:1. 为本项工程设计建立文件夹。

注意文件夹名不能用中文,且不可带空格。

2. 输入设计项目并存盘。

3. 将设计项目设计为工程文件。

4. 选择目标器件并编译。

b a b a b a So ⊕=+=ab Co =5. 时序仿真。

6. 引脚锁定。

7. 编程下载。

实验二用原理图法设计一位、四位全加器一、实验目的:1. 熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路;2. 通过一个半加器的设计把握利用EDA 软件进行电子线路设计的详细流程;3. 学会对实验板上的FPGA/CPLD 进行编程下载,硬件验证自己的设计项目。

二、实验器材:1、计算机及操作系统2、QUARTUS II软件三、实验要求:1.利用原理图输入法对一位全加器电路进行描述;2. 进行波形仿真测试;3. 严格按照实验步骤进行实验;四、实验原理:利用实验一所设计的半加器设计一位全加器;利用设计封装好的一位全加器进行四位全加器的设计。

五、实验步骤:与实验一相同。

六、实验报告:1. 要求画出一位、四位全加器的真值表;2. 分析用半加器实现一位全加器的优点;3. 对波形进行分析,并绘制波形图。

实验三用文本输入法设计D触发器和锁存器一、实验目的:1. 熟悉QuartusⅡ的VHDL 文本设计过程。

EDA技术实验报告

(此文档为word格式,下载后您可任意编辑修改!)实验一利用原理图输入法设计4位全加器一、实验目的:掌握利用原理图输入法设计简单组合电路的方法,掌握MAX+plusII的层次化设计方法。

通过一个4位全加器的设计,熟悉用EDA软件进行电路设计的详细流程。

二、实验原理:一个4位全加器可以由4个一位全加器构成,全加器的进位以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的低位进位输入信号cin相接。

1位全加器f-adder由2个半加器h-adder和一个或门按照下列电路来实现。

半加器h-adder由与门、同或门和非门构成。

四位加法器由4个全加器构成三、实验内容:1. 熟悉QuartusII软件界面,掌握利用原理图进行电路模块设计的方法。

QuartusII设计流程见教材第五章:QuartusII应用向导。

2.设计1位全加器原理图(1)生成一个新的图形文件(file->new->graphic editor)(2)按照给定的原理图输入逻辑门(symbol->enter symbol)(3)根据原理图连接所有逻辑门的端口,并添加输入输出端口(4)为管脚和节点命名:在管脚上的PIN_NAME处双击鼠标左键,然后输入名字;选中需命名的线,然后输入名字。

(5)创建缺省(Default)符号:在 File菜单中选择 Create Symbol Files for Current File 项,即可创建一个设计的符号,该符号可被高层设计调用。

3.利用层次化原理图方法设计4位全加器(1)生成新的空白原理图,作为4位全加器设计输入(2)利用已经生成的1位全加器的缺省符号作为电路单元,设计4位全加器的原理图.4.新建波形文件(file->new->Other Files->Vector Waveform File),保存后进行仿真(Processing ->Start Simulation),对4位全加器进行时序仿真。

EDA实验报告(程序)

江西科技师范大学实验报告课程EDA技术与verilog实验系别通信与电子学院班级10电科一班学号20102481姓名刘先明报告规格一、实验目的二、实验原理三、实验仪器四、实验方法及步骤五、实验记录及数据处理误差分析及问题讨论实验一 EDA实验箱使用一.实验目的1.GW48教学实验系统原理与使用介绍2.熟悉QuartusII两种输入方式下编译、仿真简单的组合电路。

二.实验内容首先了解GW48系统使用注意事项以及GW48系统主板结构与使用方法,接着对各实验电路结构图特点与适用范围简述。

最后在QuartusII界面下,用文本输入和图形输入分别验证九选一多路选择器的功能。

三.程序清单文本输入如下所示:module mux91a(a0,a1,a2,a3,a4,a5,a6,a7,a8,out6,sel);input a0,a1,a2,a3,a4,a5,a6,a7,a8;input [3:0] sel;output out6;reg out6;always @ (a0,a1,a2,a3,a4,a5,a6,a7,a8)begincase (sel)0:out6<=a0;1:out6<=a1;2:out6<=a2;3:out6<=a3;4:out6<=a4;5:out6<=a5;6:out6<=a6;7:out6<=a7;8:out6<=a8;default:out6<=0;endcaseendendmodule图形输入如下所示:四.实验步骤1、新建一个名称为MUX91a的工程,并在该文件夹中新建一个MUX91a.v的文件。

2、编译代码,编译成功后进行第三步,若不成功则查改代码中的错误。

3、在工程文件夹中新建一个MUX91a.vwf的波形文件,导入工程端口,设置输入波形,仿真得出输出端口波形。

4、验证输出端口波形是否达到四选一多路选择器的功能。

仿真波形如下图所示。

eda实验报告完整版

EDA实验报告焦中毅201300121069实验1 4选1数据选择器的设计一、实验目的1.学习EDA软件的基本操作。

2.学习使用原理图进行设计输入。

3.初步掌握器件设计输入、编译、仿真和编程的过程。

4.学习实验开发系统的使用方法。

二、实验仪器与器材1.EDA开发软件一套2.微机一台3.实验开发系统一台4.打印机一台三、实验说明本实验通过使用基本门电路完成4选1数据选择器的设计,初步掌握EDA设计方法中的设计输入、编译、综合、仿真和编程的过程。

实验结果可通过实验开发系统验证,在实验开发系统上选择高、低电平开关作为输入,选择发光二极管显示输出电平值。

本实验使用Quartus II 软件作为设计工具,要求熟悉Quartus II 软件的使用环境和基本操作,如设计输入、编译和适配的过程等。

实验中的设计文件要求用原理图方法输入,实验时,注意原理图编辑器的使用方法。

例如,元件、连线、网络名的放置方法和放大、缩小、存盘、退出等命令的使用。

学会管脚锁定以及编程下载的方法等。

四、实验要求1.完成4选1数据选择器的原理图输入并进行编译;2.对设计的电路进行仿真验证;3.编程下载并在实验开发系统上验证设计结果。

五、实验结果4选1数据选择器的原理图:仿真波形图:管脚分配:实验2 四位比较器一、实验目的1.设计四位二进制码比较器,并在实验开发系统上验证。

2.学习层次化设计方法。

二、实验仪器与器材1.EDA 开发软件 一套 2.微机 一台 3.实验开发系统 一台 4.打印机 一台 5.其它器件与材料 若干 三、实验说明本实验实现两个4位二进制码的比较器,输入为两个4位二进制码0123A A A A 和0123B B B B ,输出为M (A=B ),G (A>B )和L (A<B )(如图所示)。

用高低电平开关作为输入,发光二极管作为输出,具体管脚安排可根据试验系统的实际情况自行定义。

四、实验要求1.用硬件描述语言编写四位二进制码 比较器的源文件; 2.对设计进行仿真验证; 3.编程下载并在实验开发系统上进行 硬件验证。