SPI接口的verilog实现

适用于MS5611的SPI接口设计

适用于MS5611的SPI接口设计崔璨;邓圣;代航阳;张杨;杨泰波【摘要】MS5611是瑞士MEAS推出的新一代高分辨率的气压传感器,广泛应用于移动高度计/气压计系统、自行车电脑、智能手表、GPS、智能手机、无人机高度测量系统等.MS5611体积小,内部集成了气压传感器、温度传感器、24位ADC、128位PROM、数字滤波器、SPI和I2C接口.针对MS5611的SPI接口,选用输入输出资源丰富,配置灵活的FPGA作为微控制器,并设计相应的SPI接口电路;采用Verilog编写具有MS5611五种指令的SPI接口模块,并进行了时序仿真验证.仿真结果表明,基于FPGA的SPI接口模块能很好地对MS5611进行控制,并实现数据的读写,在基于MS5611的气压测量设备上有很好应用.【期刊名称】《科技创新导报》【年(卷),期】2017(014)001【总页数】4页(P31-33,35)【关键词】气压测量;MS5611;SPI;时序仿真【作者】崔璨;邓圣;代航阳;张杨;杨泰波【作者单位】中国核动力研究设计院四川成都 610094;中国核动力研究设计院四川成都 610094;中国核动力研究设计院四川成都 610094;中国核动力研究设计院四川成都 610094;中国核动力研究设计院四川成都 610094【正文语种】中文【中图分类】TP361.1气压和温度一直都是很多实验室和工业生产中的重要环境参数,需要对其进行实时检测,以实现对实验室环境和工业生产环境的控制,达到实验预想效果,生产出高品质产品[1]。

例如:在机房设备监测系统中,通过气压传感器对气压进行监测,当波动较大时,可通过短信通知机房负责人[2]。

而对于登山爱好者来说,非常关心海拔高度,可通过测量气压来计算海拔高度,其测量精度远比全球定位系统(Glo bal Positioningsystem, GPS)高,在原有GPS基础上增加气压测量功能,可使三维定位更加准确。

SPI_I2S

应用笔记487利用MAX II CPLD 实现SPI 至I 2S 的接口引言本应用笔记介绍怎样使用Altera ®MAX ®II CPLD 来实现协议转换,通过串行外设接口(SPI)控制inter-IC 声音(I 2S)总线上的音频设备数据流。

I 2S 和SPI 接口I 2S 是3线半双工串行接口,常用于通过被称为I 2S 总线的3线总线来连接系统中的音频设备。

I 2S 设备和总线使用3条线:串行数据(SDA ),承载了对应于每一个音频通道的两路时分复用音频数据;串行时钟(SCK )和字选择(WS ),控制数字音频数据在I 2S 总线上不同设备之间的传输。

I 2S 系统能够处理和串行时钟分开的串行音频数据,以消除抖动。

SPI 是4线全双工串行接口,常用于连接系统内部和外部的系统处理器(主机)和外设(从机)。

SPI 利用单独的数据输出信号线(主机输出从机输入,即MOSI )和数据输入信号线(主机输入从机输出,即MISO ) 以及时钟(SCLK )和从机选择或者片选信号(CS )来进行通信。

本设计支持SPI 接口主机对其他设备的数据流控制,包括A/D 转换器、数字信号处理器、数字滤波器、音频处理器、PC 多媒体音频转换器等 I 2S 总线设备。

有的嵌入式系统并没有为音频数据通信提供I 2S 接口,但是有SPI 接口。

您可以在和这些接口相似的环境中有效地使用本设计。

利用MAX IICPLD 实现SPI 至I 2S 的接口SPI 主机的桥接接口是SPI 从机,它有四条信号线(CS , SCLK , MISO 和MOSI )。

I 2S 总线一侧接口是I 2S 主机,它有三条信号线(I2S_ SCK , I2S_SDA 和I2S_WS )。

CLK 是主机时钟,位于I 2S 主机外部。

图1所示为采用 MAX II CPLD 来实现SPI 至I 2S 接口。

2007年12月,1.0版图1.利用MAX II CPLD实现SPI至I2S接口本设计提供协议转换功能,通过SPI 接口(更常用的4线串行接口,用于连接串行外设接口和微处理器或者主机)来控制I2S 总线(带宽相对较窄的协议,用于连接系统中的数字音频设备)上音频设备的数据流。

SPI控制器的ASIC设计与实现

SPI控制器的ASIC设计与实现

曹傧;王祥;程野;张瑞峰;杜杨

【期刊名称】《数字通信》

【年(卷),期】2010(037)001

【摘要】介绍了SPI控制器的基本原理,详细阐述了该控制器的设计思路,重点介绍了主控模块和收发模块的架构.在用Verilog语言实现整个设计的基础上,运用ModelSim进行了功能仿真,利用SMIC 0.13 μm工艺库和SYNOPSYS的Design Compiler对其综合.经过FPGA验证,确保该控制器作为一个独立的IP核可嵌入到ASIC系统中.

【总页数】3页(P94-96)

【作者】曹傧;王祥;程野;张瑞峰;杜杨

【作者单位】重庆邮电大学移动通信重点实验室,重庆,400065;重庆邮电大学移动通信重点实验室,重庆,400065;重庆邮电大学研究院,重庆,400065;重庆邮电大学移动通信重点实验室,重庆,400065;重庆邮电大学移动通信重点实验室,重庆,400065【正文语种】中文

【相关文献】

1.ⅡS控制器的ASIC设计与实现 [J], 郑建宏;程野

2.Camera接口控制器的ASIC设计与实现 [J], 晏龙;郑建宏

3.基于FPGA的SPI Flash控制器的设计与实现 [J],

4.SPI接口控制器设计与实现 [J], 王耿;王金明

5.面向EEPROM应用的SPI主控制器设计与实现 [J], 赵海婷;贺占庄

因版权原因,仅展示原文概要,查看原文内容请购买。

FPGA实现SPI

FPGA实现SPIFPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以实现不同的数字电路功能。

SPI(Serial Peripheral Interface)是一种同步串行通信协议,常用于连接外围设备和主控制器。

在本文中,将介绍如何使用FPGA实现SPI。

1.确定硬件资源:首先,需要确定FPGA中可用的IO资源。

SPI需要至少4个IO口,分别是主设备的时钟引脚(SCK),主设备输出的数据引脚(MOSI),主设备输入的数据引脚(MISO)和片选引脚(SS)。

根据所用的FPGA型号,可以查找对应的引脚定义。

2.确定SPI时序:SPI的时序是非常重要的,不同设备可能有不同的时序规范。

一般情况下,SPI的时序包括时钟下降沿数据采样、时钟上升沿数据输出等。

SPI的时序图可以在设备的数据手册中找到。

3. 编写SPI控制器:SPI控制器可以用硬件描述语言如VHDL或Verilog编写。

控制器的功能包括生成时钟、控制数据的发送和接收、以及处理片选信号。

a.时钟生成:SPI通信需要一个时钟信号来驱动数据的传输。

可以通过计数器模块来生成控制器的时钟信号。

计数器的频率一般是SPI时钟频率的若干倍。

b. 数据发送:对于主设备(Master),要发送数据给外设,可以使用移位寄存器(Shift Register)来存储要发送的数据。

可以使用计数器生成移位寄存器的时钟信号,通过串行输入数据,并在时钟的上升沿时将数据发送到MOSI引脚。

c.数据接收:对于主设备,要接收外设发送的数据,可以使用另一个移位寄存器来接收MISO引脚传输的数据。

可以使用计数器生成移位寄存器的时钟信号,通过MISO引脚接收数据,并在时钟的下降沿时将数据存储到接收寄存器。

d.片选控制:SPI通信需要一个片选信号来选择要与主设备通信的外设。

可以通过一个时序控制器实现片选信号的生成。

在与一些外设通信时,使能片选信号,否则禁用片选信号。

CRC校验在SPI接口设计中的实现

CRC校验在SPI接口设计中的实现强小燕;史兴强;刘梦影【摘要】串行外设接口(SPI,serial peripheral interface)以其高速的传输性能和灵活简单的配置,广泛应用于扩展外设及其数据交换.由于串行通信传输的不确定性以及干扰等原因,通信经常会出现异常情况.为提高SPI通信传输的可靠性,在SPI接口设计中增加循环冗余校验(CRC,cyclic Redundancy Check)功能.运用硬件描述语言Verilog HDL设计并实现了具有CRC校验功能的SPI接口.仿真结果表明,该SPI 接口不仅可以高速高效地工作于多种工作模式,且CRC校验功能能够保证通信传输的可靠性.【期刊名称】《电子与封装》【年(卷),期】2018(018)011【总页数】6页(P30-35)【关键词】CRC;串行;SPI;可靠性【作者】强小燕;史兴强;刘梦影【作者单位】中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072【正文语种】中文【中图分类】TN4021 引言为适应复杂的通信环境和高速的通信速率要求,能够快速可靠地完成大量数据交换的数据总线是极其重要的,因此设计一个高效可靠的通信接口就十分重要。

SPI接口技术是一种高速高效的串行接口技术[1],其接口连线简单、配置灵活、传输效率高[2],广泛应用于扩展外设和进行数据交换[3]。

随机噪声和干扰等因素存在于串行通信传输中,可能导致数据传输错误。

通过采用硬件措施进而加强通信传输的可靠性可检测这类错误,或在设计中增加校验功能,通过该方法检测数据在传输过程中是否发生错误[4]。

CRC是由分组线性码的分支而来[5],该算法简单易实现,能够同时检测和抗干扰,是一种高效可靠的差错校验法[6]。

该方法导致数据的冗余量增加,发送端不仅发送数据,最后还需将CRC码发送给接收端。

Verilog的spi总线-推荐下载

SPI串行总线接口的Verilog实现摘要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。

SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。

本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。

重点描述了SPI串行总线接口在一款802.11b芯片中的位置,及该接口作为基带和射频的通讯接口所完成的功能,并给出了用硬件描述语言Verilog HDL 实现该接口的部分程序。

该实现已经在Modelsim 中完成了仿真, 并经过了FPGA 验证, 最后给出了仿真和验证的结果。

在SOC设计中,利用EDA 工具设计芯片实现系统功能已经成为支撑电子设计的通用平台.并逐步向支持系统级的设计方向发展。

而且,在设计过程中,越来越强调模块化设计。

SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通讯效率高等特点。

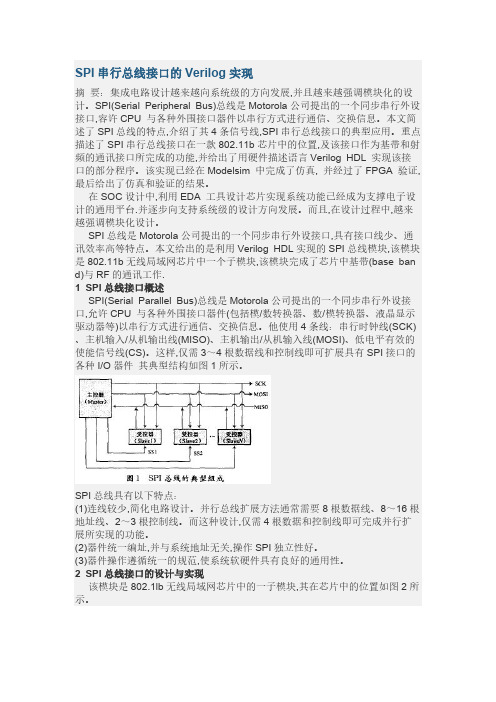

本文给出的是利用Verilog HDL实现的SPI总线模块,该模块是802.11b无线局域网芯片中一个子模块,该模块完成了芯片中基带(base band)与RF的通讯工作.1 SPI总线接口概述SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,允许CPU 与各种外围接口器件(包括模/数转换器、数/模转换器、液晶显示驱动器等)以串行方式进行通信、交换信息。

他使用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有效的使能信号线(CS)。

这样,仅需3~4根数据线和控制线即可扩展具有SPI接口的各种I/O器件其典型结构如图1所示。

SPI总线具有以下特点:(1)连线较少,简化电路设计。

并行总线扩展方法通常需要8根数据线、8~16根地址线、2~3根控制线。

SPI协议的Verilog 实现

// //接收数据存入 out_data

6

begin case(addr) 1'b0: begin in_buffer = in_data; busy = 1'b1; end 转入工作状态 1'b1: begin busy = 1'b0;end endcase end end else begin if(cs) begin clkcount = clkcount + 1'b1; if(clkcount >= 8'b10) // 控制 SCK 周期 begin clkcount = 0; if((count % 2) == 0) //待发数据存入缓存区,

DataPort[5]-DataPort[0] : busy、sdo 、addr、cs、wr、rd DataPort[21]-DataPort[14] :待发送 8bit 数据 DataPort[13]-DataPort[6] : 接收的 8bit 数据

3

� 总结

完成时间:12.4--12.12 前期:该阶段主要是熟悉 SPI 工作原理,进一步掌握和认识 SPI 通信协议。Chipscore 的使 用之前未曾接触, 在这一阶段, 我先通过简单编程结合开发板抓取数据进行分析达到 对其的基本掌握。 中期:在熟悉 SPI 的工作原理之后,开始尝试编写代码。写了两三次代码,效果均不理想, 很多问题在编写代码的时候没有考虑清楚,导致到了仿真阶段结果与预期有所差距, 且代码冗长复杂。参考了一些资料,效果也不是很好,特别是数据传输暂停部分, 很 多都省略了。不过借鉴别人写的代码也让我收获了不少编写的经验,有些情况下, 运 用不同的逻辑思维可以让代码更简洁、 更具有健壮性。 当然期间也遇到了一些自己无 法解决的问题,非常感谢福星学长耐心的指导,让我学到了不少知识和经验。 后期:该阶段主要是对代码进行再修改、波形仿真以及抓数据调试。 问题及分析: 小问题遇到不少,不过大多都通过 error 的提示,或者上网搜索,找到了问题的原因, 并予以解决。也有软件上的原因,比如:第一次装 ISE 的时候可能没有安装好,上板调试的 时候,cable 不能识别。经过测试分析发现 ISE 里的 drive 没有装上。考虑到这样一个问题的 出现可能还会附带有一些软件上的漏洞,重装了一遍 ISE,问题解决。 使用 chipscope 的时候,芯片配置不对连接失败,查阅该电路板的资料,重新配置,问 题解决。在 chipscope 里面有些触发信号找不到,经分析是被优化了,通过简单修改代码避 免它被优化后,问题解决。运行 chipscope 后发现 waveform 始终没反应,经过一番分析, 认 为时钟线的引脚配置有问题,重换一个时钟信号线 I/O 引脚,问题解决。解决后发现抓取的 波形没有明显的高低跳变,经分析可能是参考时钟选取不对,重选后问题解决。

基于UVM的SPI接口IP核的设计与验证

基于UVM的SPI接口IP核的设计与验证SPI(Serial Peripheral Interface)是一种常用的串行外设接口,广泛应用于数字系统中。

为了实现SPI接口的功能,需要设计和验证相应的IP核。

本文将介绍基于UVM(Universal Verification Methodology)的SPI接口IP核的设计与验证。

首先,我们需要了解SPI接口的基本原理。

SPI接口由一个主设备和一个或多个从设备组成。

主设备通过时钟信号控制数据的传输,同时使用片选信号选择从设备。

主设备通过一个数据线发送数据,并通过另一个数据线接收从设备返回的数据。

SPI接口的主要特点是数据传输速度快、灵活性高,适用于多种外设连接。

在设计SPI接口的IP核时,我们需要考虑以下几个方面。

首先,IP核需要支持不同的SPI模式,包括不同的时钟极性和相位设置。

其次,IP核需要能够处理不同的数据位宽,并支持全双工和半双工传输模式。

此外,IP核还需要支持多个从设备的片选信号,并能够处理中断请求。

为了验证SPI接口的IP核,我们采用了UVM方法。

UVM 是一种基于SystemVerilog的验证方法学,提供了一套丰富的验证库和方法。

我们可以利用UVM提供的功能,建立一个完整的验证环境,并编写验证测试用例。

在验证SPI接口的IP核时,我们需要分别验证其主设备和从设备的功能。

对于主设备,我们可以编写测试用例来验证其发送数据的正确性、时序和时钟控制的准确性。

对于从设备,我们可以编写测试用例来验证其接收数据的正确性和片选信号的选择准确性。

通过使用UVM方法,我们可以模拟SPI接口的IP核,并在仿真平台上验证其功能和性能。

通过编写一系列的测试用例,我们可以确保IP核在不同的工作场景下都能正常工作。

综上所述,本文介绍了基于UVM的SPI接口IP核的设计与验证。

通过设计一个支持多种模式、不同数据位宽和多个从设备的IP核,并利用UVM方法进行验证,我们可以确保IP核在实际应用中的正确性和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI接口的verilog实现

项目中使用的许多器件需要SPI接口进行配置,比如PLL:ADF4350,AD:AD9627,VGA:AD8372等,根据SPI协议,站长编写了一个简单的SPI读写程序,可以进行32为数据的读写(读者可以修改程序中数字使其变成16位或8位读写,也可以将读写位数参数化),可以设置SPI SCLK相对于主时钟的分频比。

【SPI程序】

/* SPI interface module V1.0 一些语句做了简单的英文注释*/

module spi_master(addr, in_data, out_data, rd, wr, cs, clk, miso, mosi, sclk);

input wire [1:0] addr;

input wire [31:0] in_data;

output reg [31:0] out_data;

input wire rd;

input wire wr;

input wire cs;

input wire clk;

inout miso;

inout mosi;

inout sclk;

reg sclk_buffer = 0;

reg mosi_buffer = 0;

reg busy = 0;

reg [31:0] in_buffer = 0;

reg [31:0] out_buffer = 0;

reg [7:0] clkcount = 0;

reg [7:0] clkdiv = 0;

reg [6:0] count = 0;

always@(cs or rd or addr or out_buffer or busy or clkdiv)

begin

out_data = 32'bx;

if(cs && rd)//selected and read

begin

case(addr)

2'b00: begin out_data = out_buffer; end // read data received by SPI interface

2'b01: begin out_data = {31'b0, busy}; end // read 'busy' flag of SPI interface

2'b10: begin out_data = clkdiv; end // read 'clkdiv' number of SPI

endcase

end

end

always@(posedge clk)

begin

if(!busy) //SPI interface is not busy

begin

if(cs && wr) //selected and write

begin

case(addr)

2'b00: begin in_buffer = in_data; busy = 1'b1; end //write in_data to SPI Buffer and let 'busy' flag on 2'b10: begin clkdiv = in_data; end //write 'clkdiv' number to SPI

endcase

end

end

else

begin

clkcount = clkcount + 1;

if(clkcount >= clkdiv) //every clkdiv*period(clk) time send one bit by SPI

begin

clkcount = 0;

if((count % 2) == 0) // change data in negtive sclk

begin

mosi_buffer = in_buffer[31];

in_buffer = in_buffer << 1;

end

if(count > 0 && count < 65) //32 periods

begin

sclk_buffer = ~sclk_buffer;

end

count = count + 1;

if(count > 65)

begin

count = 0;

busy = 1'b0;

end

end

end

end

always@(posedge sclk_buffer)

begin

out_buffer = out_buffer << 1;

out_buffer[0] = miso; //read data from pin 'miso'

end

assign sclk = sclk_buffer;

assign mosi = mosi_buffer;

endmodule

【SPI程序testbench】

/*

SPI module testbench V1.0

Loujianquan

2009.7.20

*/`timescale 1ns/1ns

module spi_master_tb();

reg [1:0] addr;

reg [31:0] in_data;

wire [31:0] out_data;

reg rd;

reg wr;

reg cs;

reg clk;

tri1 miso;

wire mosi;

wire sclk;

spi_master uut(addr, in_data, out_data, rd, wr, cs, clk, miso, mosi, sclk); integer counter = 0;

initial

begin

// Init

addr = 0;

in_data = 0;

rd = 0;

wr = 0;

cs = 0;

clk = 0;

// Set CLK_DIV

addr = 2;

in_data = 0;

wr = 1;

cs = 1;

#20;

addr = 0;

in_data = 0;

wr = 0;

cs = 0;

#20;

// Output from 0 to 255

for(counter = 0; counter < 256; counter = counter + 1) begin

addr = 0;

in_data = counter;

wr = 1;

cs = 1;

#20;

addr = 0;

in_data = 0;

wr = 0;

cs = 0;

#20;

// Poll Busy signal

addr = 1;

cs = 1;

rd = 1;

#20;

while(out_data[0] == 1'b1)

begin

#20;

end

cs = 0;

#20;

end

$stop;

end

always begin clk = ~clk; #10; end endmodule

【仿真波形】

ISE仿真结果。