锁相环英文文献翻译

锁相环设计外文翻译

外文翻译原文1:Frequency Modulation in Microwave Phase Lock Loop Synthesizers译文1:微波锁相回路合成器的调频原文2:The Design of A Low-Power Low-Noise Phase Lock Loop译文2:低功率低噪声的锁相环的设计Frequency Modulation in Microwave Phase Lock Loop SynthesizersAbstract —This paper shows, that frequency modulation bandwidth of phase locked controlled oscillator (CO) can be simple expanded using precorrecting circuit (corrector) connected to control port of oscillator. A method is presented of calculation of corrector according to exact PLL and frequency response of modulation channel, with experimental demonstration presented of adequacy of described technique being shown.Index Terms —Microwave PLL synthesizer, frequency modulation, maximum deviation, modulation bandwidth.I. INTRODUCTIONIn many microwave systems the synthesizer must generate frequency modulated signal in addition to monochromatic signal generation, its main function. Solution of this problem in case of phase lock loop (PLL) synthesizer becomes complicated due resistance of PLL to the CO modulation, as an automatic control system. The most difficulty is the expansion of modulation band and the modulation index range. The purpose of this paper is contribution in solution of these problems.II. TARGET SETTINGIt is well known that frequency modulation possibility of phase locked CO is limited by cutoff band. Modulation bandwidth corner is equal to PLL angular frequency [1]. In band above cutoff the loop makes no resistance to the CO modulation, but below cutoff its resistance increases when modulating frequency decreases. Thus, modulation bandwidth of CO must be widened up to down the PLL angular frequency. It can be made by three issues:• By decrease of PLL cutoff frequency;•by impact modulating signal into PLL: modulation of the reference frequency, manipulation of feedback division ratio, addition of the modulating signal to control signal of phase detector;•by application of linear precorrection to modulating signal for compensation of high-pass properties of PLL [2,3].Further the last method is considered. It is more effective as it makes no worse on dynamic and spectral purity characteristics of PLL synthesizer like first method and has no limitation of modulation bandwidth above like second way.III. MATHEMA TICAL DESCRIPTION OF CORRECTOR MODEL To improve the modulation sensitivity of CO an active corrector instead the passive corrector [2] is proposed in Fig. 1.Fig. 1. Corrector schematicModulating signal comes to input 1. PLL control signal comes to input 2. Driving signal for CO goes out through output 3.A. Small signal modelCorrector transfer function K1(p) from input 1 to output 3 is represented by:where a, c are gain factors of third stage at low and high frequencies respectively; τ is high frequency time constant of third stage; k is depth of dip of response curve in PLL corner frequency area;b is gain factor of first stage at high frequencies; τ1, τ2 are low and high frequency time constants of dip of response curve respectively. Parameters in (1) can be selected in case of an exact PLL and modulation channel requirements.B. Large signal modelMaximum deviation ΔFmax is limited by several facto rs, which are bound with nonlinear distortions of modulated signal envelope. These distortions appear in such cases as:-voltage or current operational amplifier (opamp) saturation;-CO frequency obtain the corner of regulation curve;-appearance of dynamic distortion of opamp.In first case the maximum deviation with voltage saturation is:where Usat is the saturation voltage of opamp; Kv is CO tuning sensitivity; KL(p) is closed PLL transfer function.In second case maximum deviation is constant equal to distance between average CO frequency and nearest corner of CO regulation curve. In third case maximum deviation is represented by [4]where S is slew rate of opamp.IV. CORRECTOR DESIGN AND TESTFig. 2 shows the calculated and experimental frequency responses of modulation channel with and without corrector. PLL cutoff frequency is 100 kHz, phase margin – 45°, CO tuning sensitivity –95 MHz/V. CO lag is not allowed.Fig. 2. Frequency responses of modulation channel normalized to CO tuning sensitivity Fig. 3 shows calculated and experimental frequency responses of maximum deviation for all types of distortions: solid curve – for first, dotted curve – for second and chain line – for third. Calculation was made for opamp AD829 with Usat=12V. Distance between average CO frequency and nearest corner of CO regulation curve is 50 MHz.From Fig. 2 and 3 is seen that modulation cannel bandwidth with corrector at maximum deviation 100 kHz is of 1,5 kHz facing 100 kHz without corrector. Dynamic distort ions in opamp don’t appear in comparison with two other types. In the fig. 2 experimental curve is close to calculated one. In Fig. 3 experimental curve differs from calculated one because current saturation of opamp has been appeared.V. CONCLUSIONSApplying an introduced corrector in PLL synthesizer one can expand the modulation bandwidth considerably. Here the simple schematic solution and low-cost elements can be used. A calculation method is simple and unlike described one in [3] incorporates the calculation of maximum frequency deviation.Fig. 3. Maximum deviation frequency responses作者:Andrew V. Gorevoy国籍:Russia出处:Siberian Conference on Control and Communications SIBCON–2009微波锁相环合成器的频率调制摘要:本论文表明,通过使用连接预先校正的电路来控制振荡器的端口,柏锁可控制振荡器的调频宽带就能够很容易被扩展。

CMOS4046集成电路研究锁相环(PLL)的工作原理 毕业论文外文翻译

本实验要使用CMOS4046集成电路研究锁相环(PLL )的工作原理。

电路包括两个不同的鉴相器和一个VCO 。

另外还有一个齐纳二极管参考电压源用在供电调节中,在解调器输出中有一个缓冲电路。

用户必须提供环路滤波器。

4046具有高输入阻抗和低输出阻抗,容易选择外围元件。

注意事项1. 本实验较为复杂,进入实验室之前,确认你已经弄懂了电路预计应该怎样工作。

对 某样东西还没有充分分析之前,不要去尝试制作它。

在开始实验之前要通读本文。

2. 在实验第一部分得到的数据要用来完成实验的其它任务。

所以要仔细对待这部分内容。

3. 小心操作4046芯片,CMOS 集成电路很容易损坏。

避免静电释放,使用10k Ω电阻 把信号发生器的输出耦合到PLL 。

在关掉4046供电电源之前先关闭信号发生器,或者从信号输入端给整个电路供电。

要避免将输出端对电源或对地短路,TTL 门电 路可以容忍这种误操作但CMOS 不能(要注意松散的导线)。

CMOS 输出也没有能力驱动电容负载。

VSS 应该接地,VDD 应该接5V ,引脚5应该接地(否则VCO 被禁止)。

1 VCO 工作原理阅读数据手册中的电路描述。

VCO 常数(0K 单位为弧度/秒-伏)是工作频率变化与输入电压(引脚9上)变化之比值。

测量出0K ,即,画出输出频率关于输入电压的曲线。

确认数据范围要覆盖5kHz 到50kHz 。

对于R1, R2 和C 的各种参数取值进行测量,确定0K 对于R1 ,R2 和C 是怎样的近似关系。

测量VCO 输出的上升和下降时间,研究电容性负载的影响。

2 无源环路滤波器无源环路滤波器位于鉴相器输出与VCO 输入之间。

此滤波器对鉴相器输出中的高次谐波进行衰减,并控制环路的强度。

通常用一个简单RC 滤波器就可以满足要求,这种设计能避免有源滤波器设计中固有的电平移动和输出限制的恼人问题。

但另外一方面,有源滤波器可以提供更优越的性能。

2.1 相位比较器首先来看一下4046的相位比较器II 的输出。

锁相环外文翻译

锁相环外文参考文献译文及原文目录外文参考文献译文1锁相环 (1)1.1锁相特性 (1)1.2历史与应用 (2)1.3其它应用 (4)2光通信元件 (5)2.1光纤 (5)2.2调制器和检测器 (6)外文参考文献原文1Phase Lock Loop (9)1.1Nature of Phaselock (9)1.2History and Application (10)1.3Other Applications (13)2Optical Communication Components (14)2.1The Optical Fiber (14)2.2Modulators and Detectors (17)1锁相环1.1锁相特性锁相环包含三个组成部分:1、相位检测器(PD)。

2、环路滤波器。

3、压控振荡器(VCO),其频率由外部电压控制。

相位检测器将一个周期输入信号的相位与压控振荡器的相位进行比较。

相位检测器的输出是它两个输入信号之间相位差的度量。

差值电压由环路滤波后,再加到压控振荡器上。

压控振荡器的控制电压使频率朝着减小输入信号与本振之间相位差的方向改变。

当锁相环处于锁定状态时,控制电压使压控振荡器的频率正好等于输入信号频率的平均值。

对于输入信号的每一周期,振荡器输出也变化一周,且仅仅变化一周。

锁相环的一个显而易见的应用是自动频率控制(AFC)。

用这种方法可以获得完美的频率控制,而传统的自动频率控制技术不可避免地存在某些频率误差。

为了保持锁定环路所需的控制电压,通常要求相位检测器有一个非零的输出,所以环路是在有一些相位误差条件下工作的。

不过实际上对于一个设计良好的环路这种误差很小。

一个稍微不同的解释可提供理解环路工作原理的更好说明。

让我们假定输入信号的相位或频率上携带了信息,并且此信号不可避免地受到加性噪声地干扰。

锁相接收机的作用是重建原信号而尽可能地去除噪声。

为了重建原始信号,接收机使用一个输出频率与预计信号频率非常接近的本机振荡器。

锁相环电路概述

锁相环电路原理概述By jluhong 锁相环的英文全称是Phase-Locked Loop,简称PLL。

它是由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)三部分构成的一种信号相差自动调节反馈电路(环)。

PLL电路框图如下,其具体工作过程为,当输入信号Vi(t)=0时,环路滤波器的输出Vc(t)为某一固定值。

这时,压控振荡器按其固有频率fv=f0进行自由振荡。

当有频率为fi的Vi(t)输入时,Vi(t)和Vo(t)同时加到鉴相器进行鉴相。

如果二者相差不大,鉴相器输出一个与二者相位差成正比的误差电压Vd(t),再经过环路滤波器滤去Vd(t)中的高频成分,输出一个直流控制电压Vc,Vc将使压控振荡器的频率fv(和相位)发生变化,向输入信号频率fi靠拢,最后使fv= fi,环路锁定。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在,而且当输入信号频率在捕捉带范围内变化时或相位变化时,VCO输出信号跟踪输入信号的频率和相位。

(跟踪是有条件的,即输入信号频率变化在一定范围内,否则PLL失锁)。

大家要注意,若鉴相器输入信号和VCO本振频率ωo频差很大时,鉴相器输出的差拍频率很高,则差拍频率经过环路低通滤波器被滤除了。

只有很小的分量漏加到压控振荡器的输入端。

由于控制电压太小,压控振荡器输出仍然是它的固有振荡频率ωo,整个系统输出信号基本没有发生变化,PLL失去其作用,因此要注意一个PLL电路对输入信号频率范围的限制(取决于ωo)。

鉴相器:鉴相器类型很多。

按鉴相特性分类有:正弦形鉴相器、锯齿形鉴相器、三角形鉴相器、梯形鉴相器等等;按电路性质分类有:模拟鉴相器、数字鉴相器、模拟乘法鉴相器等等。

环路滤波器可分为有源和无源二类。

压控振荡器的类别很多,常用的有LC压控振荡器,RC压控振荡器,晶体压控振荡器(VCXO)在锁相环中压控振荡器实现压控主要采用如下两种方法:直接改变决定振荡频率的振荡回路元件(如C、或R)的数值;控制多谐振荡器中定时元件的充放电流或电压。

全数字锁相环的VHDL设计【文献综述】

文献综述电子信息工程全数字锁相环的VHDL设计前言锁相环其实不是什么新东西,很早以前就有人使用了。

锁相技术的理论早在1932年就被提出来了,但直到40年代在电视机中才得到广泛的应用,用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。

20世纪50年代后期随着空间技术的发展,锁相环用于对宇宙飞行目标的跟踪、遥测和遥控。

60年代初随着数字通信系统的发展,锁相环应用愈广,例如为相干解调提取参考载波、建立位同步等。

具有门限扩展能力的调频信号锁相鉴频器也是在60年代初发展起来的。

在电子仪器方面,锁相环在频率合成器和相位计等仪器中起了重要作用。

锁相环的英文全称是(Phase-Locked Loop),简称PLL,锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环。

是实现相位自动控制的负反馈系统,它使振荡器的相位和频率与输入信号的相位和频率同步。

主题从前言的论述中我们知道了锁相环路具有一些相当优良的功能,且成本低、使用方便,因而它已成为电子技术领域中一种相当有用的技术手段,获得了越来越广泛的应用。

锁相环可以分为模拟锁相环和数字锁相环。

模拟锁相环主要由相位参考提取电路、压控振荡器、相位比较器、控制电路等组成。

压控振荡器输出的是与需要频率很接近的等幅信号,把它和由相位参考提取电路从信号中提取的参考信号同时送入相位比较器,用比较形成的误差通过控制电路使压控振荡器的频率向减小误差绝对值的方向连续变化,实现锁相,从而达到同步。

数字锁相环主要由相位参考提取电路、晶体振荡器、分频器、相位比较器、脉冲补抹门等组成。

分频器输出的信号频率与所需频率十分接近,把它和从信号中提取的相位参考信号同时送入相位比较器,比较结果示出本地频率高了时就通过补抹门抹掉一个输入分频器的脉冲,相当于本地振荡频率降低;相反,若示出本地频率低了时就在分频器输入端的两个输入脉冲间插入一个脉冲,相当于本地振荡频率上升,从而达到同步[1]。

锁相技术译文翻译

锁相技术译文翻译英文原文:An On-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOI译文:45纳米SOI全数字片上测量电路表征锁相环响应特性年级专业:姓名:学号:2013 年 6 月 2 日英文中文An On-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOIAbstract—An all-digital measurement Circuit , built in 45-nm SOI-CMOS enabl es on-chip characterization of phase-loc ked loop (PLL) response to a self-induce d phase step.This technique allows estimationof PLL closed-loop bandwidth and jitterpeaking. The circuit canbe used to plot step-response vs.time, measure static phase error,and observe phase-lock status. INTRODUCTIONMany applications such as PCI Express ? require a PLL to produce alow-jitter cl ock at a given frequency while meeting stringent bandwidth and jitter peaking r 45纳米SOI全数字片上测量电路表征锁相环响应特性摘要---建立在45纳米的SOI-CMOS上一个全数字测量电路,它能够表征PLL对自诱导相步进的响应这项技术允许对PLL闭环带宽和抖动峰值的估计。

司洪珲的外文翻译

本科生毕业设计 (论文)外文翻译原文标题Designing,Simulating,and Testing an AnalogPhase-Locked LoopPhase-Locked Loop in a Digital Environment译文标题在数码环境下设计、模拟和测试一个模拟锁相环作者所在系别电子工程系作者所在专业自动化作者所在班级B06223作者姓名司洪珲作者学号20064022318指导教师姓名齐建玲指导教师职称副教授完成时间2009 年12 月北华航天工业学院教务处制译文标题在数码环境下设计,模拟和测试一个模拟锁相环原文标题Designing,Simulating,and Testing an Analog Phase-Locked Loop in aDigital Environment作者Thomas J. ThatcherMichael M. OshimaCindy Botelho译名托马斯.撒切尔罗切斯特辛迪博特略国籍美国美国美国原文出处April 1997 Hewlett-Packard Journal 6在数码环境下设计,模拟和测试一个模拟锁相环唐静文,中国香港罗切斯特,美国设计用在几项惠普ASIC上的锁相环时,现有阶段的数字部分锁相环被转移成一个VHDL描述与合成的行为。

在模拟部分写出一种行为模型,使ASIC设计师模拟运行系统。

开发出了一种新的非常有效的,用于筛选出在原来的设计过滤过程中的缺陷的泄漏试验。

本文介绍了设计和集成几个正在当前应用专用集成电路的锁相环的一个阶段过程。

该设计是基于锁相环的ASIC上一个循环,但有一些改进。

首先,该阶段的数字部分锁相环被转移到了一种VHDL描述与合成的行为。

在编写代码时,可重用性是一个大的考虑。

VHDL代码的便携性使我们能在很短的时间内设计几种锁相环。

第二,写一个行为模型的模拟部分,这样使ASIC设计师模拟运行系统。

在全数字化设计环境下,对于设计师模拟锁相环提出了若干挑战。

第十五篇 锁相环PLL及APBDIV

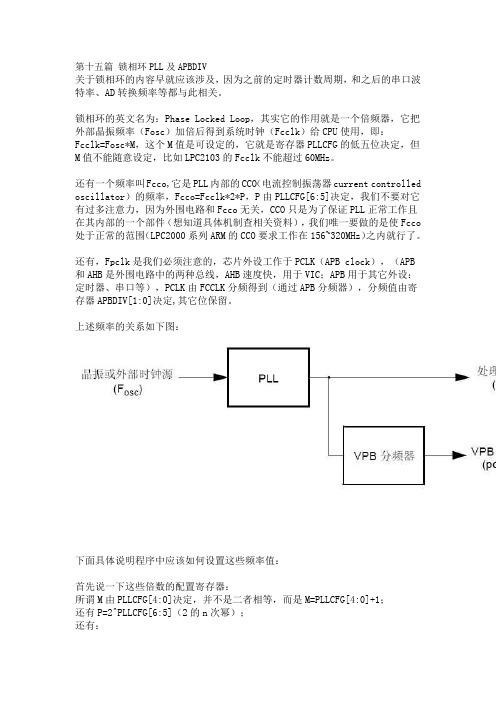

第十五篇锁相环PLL及APBDIV关于锁相环的内容早就应该涉及,因为之前的定时器计数周期,和之后的串口波特率、AD转换频率等都与此相关。

锁相环的英文名为:Phase Locked Loop,其实它的作用就是一个倍频器,它把外部晶振频率(Fosc)加倍后得到系统时钟(Fcclk)给CPU使用,即:Fcclk=Fosc*M,这个M值是可设定的,它就是寄存器PLLCFG的低五位决定,但M值不能随意设定,比如LPC2103的Fcclk不能超过60MHz。

还有一个频率叫Fcco,它是PLL内部的CCO(电流控制振荡器current controlled oscillator)的频率,Fcco=Fcclk*2*P,P由PLLCFG[6:5]决定,我们不要对它有过多注意力,因为外围电路和Fcco无关,CCO只是为了保证PLL正常工作且在其内部的一个部件(想知道具体机制查相关资料),我们唯一要做的是使Fcco 处于正常的范围(LPC2000系列ARM的CCO要求工作在156~320MHz)之内就行了。

还有,Fpclk是我们必须注意的,芯片外设工作于PCLK(APB clock),(APB 和AHB是外围电路中的两种总线,AHB速度快,用于VIC;APB用于其它外设:定时器、串口等),PCLK由FCCLK分频得到(通过APB分频器),分频值由寄存器APBDIV[1:0]决定,其它位保留。

上述频率的关系如下图:下面具体说明程序中应该如何设置这些频率值:首先说一下这些倍数的配置寄存器:所谓M由PLLCFG[4:0]决定,并不是二者相等,而是M=PLLCFG[4:0]+1;还有P=2^PLLCFG[6:5](2的n次幂);还有:APBDIV[1:0]=00,Fcclk/Fpclk=1/4;APBDIV[1:0]=01,Fcclk/Fpclk=1;APBDIV[1:0]=10,Fcclk/Fpclk=1/2;APBDIV[1:0]=11,保留。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相技术译文翻译

英文原名:High Speed Digital Hybrid PLL Frequency Synthesizer

译文:高速数字混合锁相环频率合成器

年纪专业:08级通信工程班

姓名:学号:

2011年 5月2日

To get the high-speed, it is necessary to prepare the precise synchronization of the complicated design.

In 2001, H. G. Ryu proposed a simplified structure of the DDFS (direct digital frequency synthesizer)-driven PLL for the high switching speed [2].

However, there is a problem that the speed of the whole system is limited by PLL.

Y. Fouzar proposed a PLL frequency synthesizer of dual loop configuration using frequency-to-voltage converter (FVC) [3].

It has a fast switching speed by the PD (phase detector), FVC using output signal of VCO and the proposed coarse tuning controller.

However, H/W complexity is increased for the high switching speed.

Also, it shows the fast switching characteristic only when the FVC works well.

Another method is pre-tuning one which is called DH-PLL in this study [4].

It has very high speed switching property, but H/W complexity and power consumption are increased due to digital look-up table (DLT) which is usually implemented by the ROM including the transfer characteristic of

VCO(voltage controlled oscillator).

For this reason, this paper proposes a timing synchronization circuit for the rapid frequency synthesis and a very simple DLT replacement digital logic block instead of the complex ROM type DLT for high speed switching and low power consumption. Also, the requisite condition is solved in the proposed method. The fast switching operation at every the frequency synthesis process is verified by the computer circuit simulation.

II.DH-PLL synthesizer

As shown in Fig.1, the open-loop synthesizer is a direct frequency synthesis type that VCO 要得到高运行速度,事先做好复杂设计的精确同步是必要的。

2001年,H.G.Ryu提出了一种简化结构的直接数字频率合成器(DDFS)驱动的高转换速度锁相环【2】。

但是,有一个问题,整个系统的速度是受锁相环限制的。

Y.Fouzar提出了一种使用频率—电压转换器(FVC)具有双重回路结构的锁相环频率合成器【3】。

因为鉴相器(PD), FVC利用了压控振荡器的输出信号和我们提出的粗调控制器,所以它具有快速切换速度。

但是,因为有高速系统转换速度使得H / W的复杂性增加了。

另外,结果表明只有FVC工作状态良好时系统才有较高切换速度。

另一种方法是做预先调整也就是本项研究中的DH-PLL 【4】。

它具有高速切换的特性,但是因为数字查找表(DLT)的原因,H / W复杂度和功耗明显增大了,因为DLT 经常被ROM执行,DLT中包含压控振荡器(VCO)的传输特性。

介于以上原因, 为得到较高切换速度和低功耗,本文提出了一种新的快速定时同步频率合成电路,用一个非常简单的DLT替代数字逻辑块,而不用复杂的ROM型(DLT)。

同时,在该方法中所需必要条件也解决了,频率合成过程的高切换速度在计算机电路仿真中已经得到验证了。

2.DH-PLL合成器

图1中所示的开环频率合成技术是一种直接频率合成方式,在频率控

desired VCO frequency.

③is fixed until a new FCW is made.

Fig. 4. Operating signal of DH-PLL. 关系是固定的。

图4 DH-PLL工作信号

Fig.5. Block diagram of the new proposed 图5 新提出的DH-PLL框图。

表1 仿真参数。