数电课程项目-下降沿触发的JK-FF组成四位同步加计数器

四位异步二进制加法计数器[资料]

![四位异步二进制加法计数器[资料]](https://img.taocdn.com/s3/m/f0cd3354a9956bec0975f46527d3240c8447a11a.png)

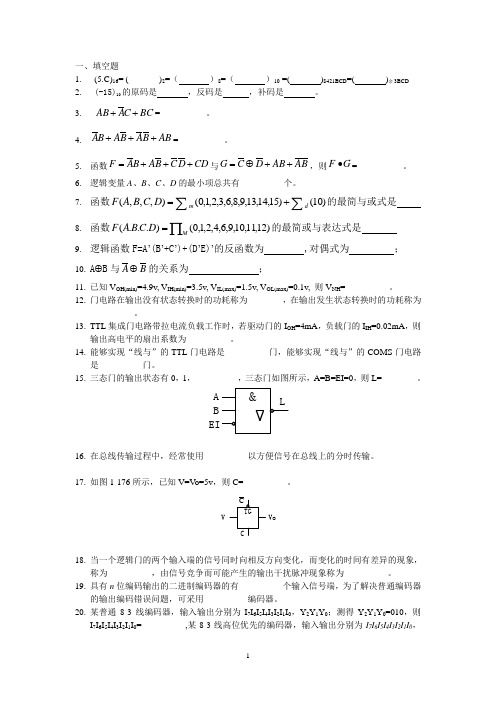

《四位异步二进制加法计数器》实验报告0实验人姓名:杨令0专业班级:电子12040班内序号:50美国德州仪器半导体技术上海(有限)公司0西安电子科技大学MSP430单片机联合实验室0实验日期:2012年10月25日实验报告提交日期:2012年11月1日0一、实验目的01.加深理解四位异步二进制加法计数器的工作原理及电路组成。

2.学会正确使用T触发器。

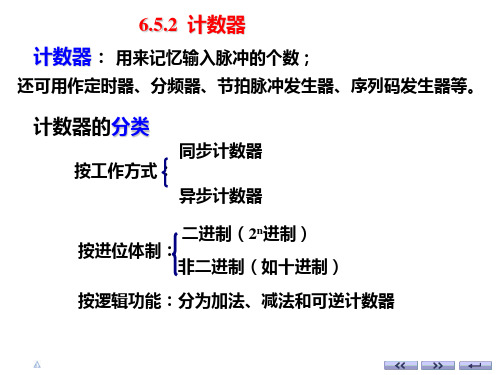

0二、实验内容01、计数器简介0计数器是最常用的时序电路之一,可用来计数、分频、定时、产生节拍脉冲以及其他时序信号。

但计数器分类有很多,有同步计数器和异步计数器、加计数器、减计数器和可逆计数器、二进制计数器、BCD码计数器、循环码计数器。

本次设计的是四位异步二进制加法计数器。

02、实验接线图、测试步骤及结果0(1)四位异步二进制计数器逻辑图如上,它由4个T触发器组成。

计数脉冲CP加至时钟脉冲输入端,每输入一个计数脉冲,U1将翻转一次。

U2、U3和U4都以前级触发器的/Q端输出作为触发信号,当Q0端由1变成0时,即/Q0由0变成1时,U1翻转,其余类推。

/R 端是用来清零端,只能全部置0,/S端是用来置1端,只能全部置1。

(2)四位二进制异步加法计数器的实现:首先是将每个T触发器的/Q端与D端相连,构成T触发器,然后按照先前的构思连接电路,加法计数器的计数脉冲输入端为CP,全部清0端为/R,全部置1端为/S,输出端由低位到高为分别为Q0、Q1、Q2、Q3。

0三、思考与总结01、功能特点:利用触发器的翻转功能,异步二进制计数器可以实现加法或减法计数,记录结果用若干位十进制数表示,N位计数器可实现0到(2N-1)个CP脉冲的计数。

02、结构特点:高位触发器的时钟脉冲CP由低位触发器的输出Q或Q提供。

03、工作原理:异步二进制加法计数器的工作特点是:高位触发器在低一位触发器的输出信号Q出现下降沿的时候翻转;异步二进制减法计数器的工作特点是:高位触发器在低一位触发器的输出信号Q出现下降沿的时候翻转。

数电经典习题 (1)

0

1

1

1

1

1

1

(3)逻辑图:

2.解:(1)

(2) ,逻辑图如下图所示:

(3)

将A,B,C接至151的地址输入端,可知151各个数据输入端Di的表达式为:

连线图如下图所示:

3.解:(1)

(2)全加器,Y1为和输出,Y2为进位输出。

(3)连线图:

4.a、状态转换图,输入:时钟CP;输出:进位C(2分)

15.三态门的输出状态有0,1,__________,三态门如图所示,A=B=EI=0,则L=________。

16.在总线传输过程中,经常使用__________以方便信号在总线上的分时传输。

17.如图1-176所示,已知V=Vo=5v,则C=__________。

18.当一个逻辑门的两个输入端的信号同时向相反方向变化,而变化的时间有差异的现象,称为__________,由信号竞争而可能产生的输出干扰脉冲现象称为__________。

46.n位DA转换器有个_________个模拟量输出值,10位D/A转换器中,其分辨率是,若其输出阶梯电压V=0.02V,则它的最大输出电压为V。

47.某8位AD转换器输入信号最大值为5v,则它能分辨的最小输入信号电压为_________,则当输入2.56V时,结果(二进码)为。

48.AD转换的过程包括、、和。

0

1

1

0

1

0

1

0

1

1

0

1

0

0

1

1

0

1

0

1

1

0

0

1

1

1

1

由表可知,电路是一个检奇电路,当输入的信号有奇数个1时输出为1,否则输出为0

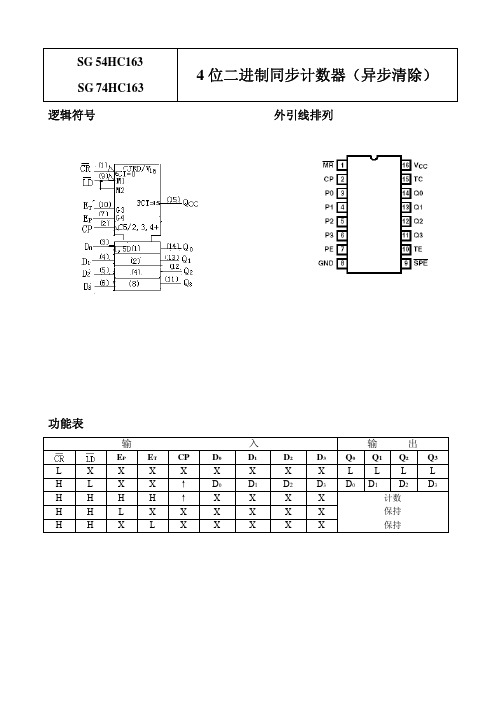

4位二进制同步计数器(异步清除)

单 位 MHz ns ns ns ns

tPHL 传输延迟时间 (最大)

tPLH 传输延迟时间 (最大)

ET→ QCC ET→ QCC

tPHL 传输延迟时间 (最大)

tREM 撤离时间 (最大)

→ QCC,Q CP → CP

tS 建立时间 (最大)

tH 保持时间 (最大)

,, ET , EP , D→CP

电源电压 输入电压 输出电压 工作环境温度TA

输入脉冲上升,下降时 间 Tr ,Tf

VCC……………….2V~6V V1…………………………..0~VCC VO……..…………..0~VCC 54HC……..-55℃~+125℃ 74HC………-400C~+85℃

VCC=2.0V….…...≤ 1000ns

D→ CP

tW 脉冲宽度 (最大)

CP, ,

tr 输入信号上升/下降

时间

tf

(最大)

tTLH 传输转换时间 tTHL (最大)

CPD 功耗电容 (典型值)

CI 输入电容 (最大)

* 无负载动态动耗PD=CPD·VCC²·f+ICC·VCC

无负载动态动耗电流IS=CPD·VCC·f+ICC

2.0 195

4.5

35

6.0

30

2.0 205

4.5

41

6.0

35

2.0 170

4.5

34

6.0

29

范 74HC TA=全温

4 21 25 217 54 46 220 44 37 258 52 44 214 43 36

值 54HC TA=全温

4 18 21 320 64 54 260 52 44 305 61 52 253 51 43

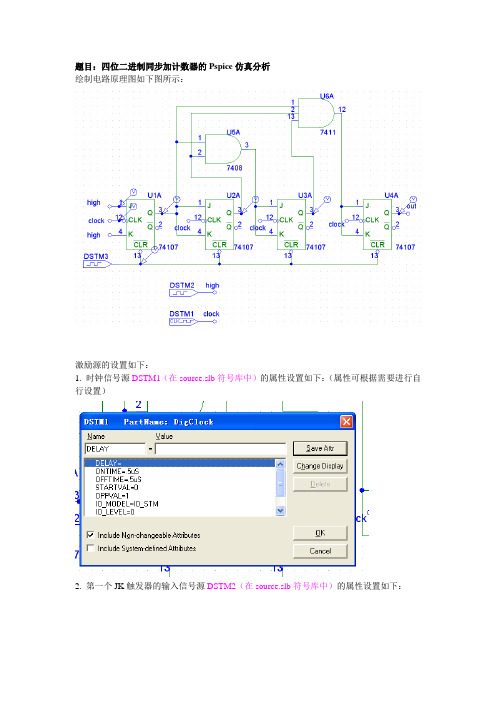

PSpice教程9-四位二进制同步加计数器仿真分析

题目:四位二进制同步加计数器的Pspice仿真分析

绘制电路原理图如下图所示:

激励源的设置如下:

1. 时钟信号源DSTM1(在source.slb符号库中)的属性设置如下:(属性可根据需要进行自行设置)

2. 第一个JK触发器的输入信号源DSTM2(在source.slb符号库中)的属性设置如下:

3. 清零信号源DSTM3(在source.slb符号库中)的属性设置如下:

仿真分析类型设置如下:

仿真结果如下:

将激励源的属性改为如下所示,仿真结果是什么?进行实验,并对结果进行分析。

思考:

1. 第一个JK触发器的的输入为什么?

2. 每一级计数器的周期是多少?

3. 在时钟信号的下降沿还是上升沿开始计数?

4. 计满多少个数在out上有一个正脉冲出现?

5. Q1、Q2、Q3、Q4分别在什么时候进行翻转?。

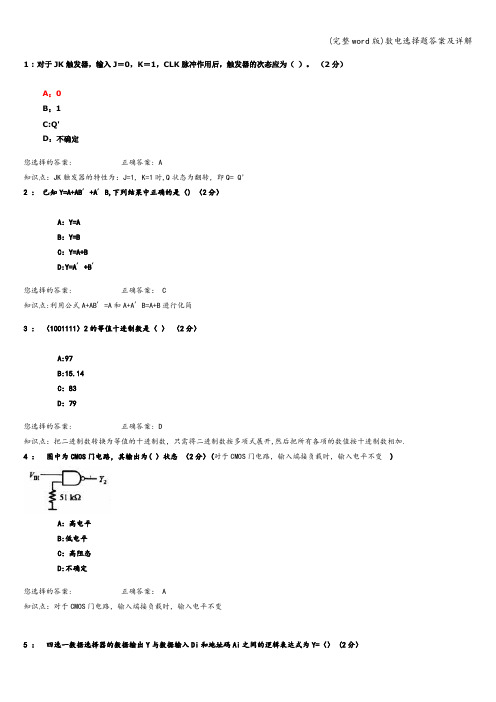

(完整word版)数电选择题答案及详解

1 : 对于JK触发器,输入J=0,K=1,CLK脉冲作用后,触发器的次态应为()。

(2分)A:0B:1C:Q'D:不确定您选择的答案: 正确答案: A知识点:JK触发器的特性为:J=1, K=1时,Q状态为翻转,即Q= Q’2 : 已知Y=A+AB´+A´B,下列结果中正确的是() (2分)A:Y=AB:Y=BC:Y=A+BD:Y=A´+B´您选择的答案: 正确答案: C知识点:利用公式A+AB´=A和A+A´B=A+B进行化简3 : (1001111)2的等值十进制数是()(2分)A:97B:15.14C:83D:79您选择的答案: 正确答案: D知识点:把二进制数转换为等值的十进制数,只需将二进制数按多项式展开,然后把所有各项的数值按十进制数相加.4 :图中为CMOS门电路,其输出为( )状态(2分)(对于CMOS门电路,输入端接负载时,输入电平不变 )A:高电平B:低电平C:高阻态D:不确定您选择的答案: 正确答案: A知识点:对于CMOS门电路,输入端接负载时,输入电平不变5 :四选一数据选择器的数据输出Y与数据输入Di和地址码Ai之间的逻辑表达式为Y=() (2分)A:A1´A0´D0+ A1´A0D1+ A1A0´D2+ A1A0D3B:A1´A0´D0C: A1´A0D1D:A1A0´D2您选择的答案: 正确答案: A知识点:四选一数据选择器的Y= A1´A0´D0+ A1´A0D1+ A1A0´D2+ A1A0D6 :一个同步时序逻辑电路可用()三组函数表达式描述(2分)A:最小项之和、最大项之积和最简与或式B:逻辑图、真值表和逻辑式C:输出方程、驱动方程和状态方程D:输出方程、特性方程和状态方程您选择的答案: 正确答案: C知识点:时序逻辑电路的逻辑关系需用三个方程即输出方程、驱动方程及状态方程来描述.7 : (1010。

数电-时序逻辑电路 计数器

——依照一般同步时序电路的设计步骤

例题

用D触发器设计同步十进制加法计数器 用JK触发器设计同步六进制减法计数器

(1)异步二-十进制计数器 74HC/HCT390

FF0 二进制计数器 CP0输入,Q0输出

FF1——FF3

异步五进制计 数器(P277)

CP1输入,Q3、Q2、Q1输出

CP1 1

1000~1111 8进制

异步计数器

方法二 整体反馈清0法实现72进制加法计数器

1 CP

××××

CR D0 D1 D2 D3

CET

CEP 74161(0) TC CP Q0 Q1 Q2 Q3 PE 1

××××

CR D0 D1 D2 D3

CET

CEP 74161(1) TC

CP Q0 Q1 Q2 Q3 PE 1

TC

CEP

74161

PE

>CP Q0 Q1 Q2 Q3

CR: 异步清零端

CP:

有效

PE: 同步并行置数使能端

D0 - D3 :预置数据输入端 CET、CEP: 计数使能端

TC:进位输出端,用于级连(TC = CET·Q3·Q2·Q1·Q0)

74161逻辑功能表

输入

输出

清预 零置

使能

时 钟

预置数据输入

连接方式1 Q2 Q1 Q0 000 001 010 011 100 101 110 111 000 001

(5421码)

连接方式2 Q0 Q3 Q2 Q1 0 000 0 001 0 010 0 011 0 100 1 000 1 001 1 010 1 011 1 100

二-五-十进制加法计数器

数字电子技术项目4 4位二进制数加法数码显示

YAB AB

A1 =B=1&;A<B时,Y AY B

≥1

YAB

&

A

B

1

YAB

YAB AB

可写出逻辑函数表达式

YAB AB AB AB AB

2.多位数值比较器

如两个多位二进制数进行比较时, 则需从高位到低位逐位进行比较。 只有在高位相应的二进制数相等时, 才能进行低位数的比较。当比较到 某一位二进制数不等时,其比较结 果便为两个多位二进制数的比较结 果。

逻辑电平开关,输出端接LED电平指示,灯亮为1, 灯灭为0。 3)验证功能 输入端按真值表输入不同数值,观察输出端接 LED电平指示,

4.4 项目实施

1.4位二进制数加法数码显示电路

+5V

S1

S2

5

A1

VCC

S3

3

A2

S4

14

A3

S1

4

S5

12

A4

S2

1

S6

6

B1

S3

13

S7

2

B2

S4

S

2. 全加器

将两个多位二进制数相加时,除了将两个同位数 相加外,还应加上来自相邻低位的进位,实现这 种运算的电路称为全加器。

全加器具有三个输入端,A、B为被加数和加数, Ci-1是来自低位的进位输入,两个输出端,Ci是向 高位的进位输出,Si是本位和输出。

写出输出逻辑表达式

Ci-1

=1

Si

Si Ai Bi Ci1

Ai

Bi

Ci Ai Bi Ci1 ( Ai Bi )

=1 &

Ai

11电子技术(JK触发器计数器)PPT课件

K

D

J Q Q3

CP

Q2

1K

Q3 主从型J-K触发器

J=0、K=1时,CP Q=0 J=1、K=0时,CP Q=1

13

20. 3计数器

20.3.1 二进制计数器 二进制数: 用0和1两个数字表示, 加1计数,逢2进1

0000 +) 1

0001 +) 1

001 0

第0位的1相当于十进制的1 第1位的1相当于十进制的2

(4) Q3的翻转: Q2Q1Q0=111时,再来一个CP,Q3翻转一23次

同步二进制加法计数器设计 用维—阻型J-K触发器

Q3 & Q2Q1Q0 Q2

Q1 Q1Q0 &

Q0

R

S

JK

R

S

JK

R

S

JK

R

S

JK

CP

JR,K=(Q2•Q1•Q0) J,K=(Q1•Q0) J,K=Q0

JK=11

CP Q3 Q2 Q1 Q0 91001 10 1 0 1 0 11 1 0 1 1 12 1 1 0 0 13 1 1 0 1 14 1 1 1 0 15 1 1 1 1 16 0 0 0 0

要求: 每来一个CP,计数器加171

1. 异步二进制加法计数器

用触发器组成计数器

例: 用维—阻型J-K触发器组成异步二进制加法计数器

在CP下降沿时,根据接收 到的J、K信息,Q变化

JK 00 01

Qn+1 Qn 0

10 1

1 1 Qn

9

主从型J-K触发器工作波形图举例

J K Qn+1CP Nhomakorabea0 0 Qn

同步计数器实验报告

同步计数器实验报告同步计数器实验报告引言:同步计数器是数字电路中常见的一种组合逻辑电路,用于实现二进制计数功能。

在本次实验中,我们将通过搭建一个4位同步计数器的电路,来探索其工作原理和性能特点。

一、实验目的本次实验的主要目的是:1. 理解同步计数器的基本原理;2. 掌握同步计数器的电路搭建方法;3. 分析同步计数器的性能特点。

二、实验器材和原理1. 实验器材:- 逻辑门集成电路(IC):我们使用74LS74型D触发器芯片;- 连线和电源:用于搭建电路连接和供电。

2. 原理:同步计数器是由多个触发器构成的,每个触发器的输出与下一个触发器的时钟输入相连。

当时钟信号触发时,触发器将根据输入信号的状态进行状态转移。

当所有的触发器都完成状态转移后,计数器的输出就会自动递增。

三、实验步骤1. 搭建电路:根据74LS74芯片的引脚功能,将两个芯片按照级联的方式连接起来。

将两个芯片的VCC引脚连接到正电源,GND引脚连接到地线。

将一个芯片的时钟输入引脚连接到一个外部时钟信号源,同时将该芯片的Q输出引脚连接到另一个芯片的时钟输入引脚。

2. 观察实验现象:接通电源后,我们可以观察到计数器的输出从0000开始递增,直到1111,然后再从0000开始重新计数。

这是因为我们使用的是4位计数器,最大计数为15(二进制1111),当计数达到最大值时,计数器会自动清零并重新开始计数。

四、实验结果与分析通过实验,我们可以得出以下结论:1. 同步计数器能够实现二进制计数功能,且能够自动清零并重新计数;2. 通过增加触发器的数量,我们可以扩展计数器的位数,实现更大范围的计数;3. 同步计数器的计数速度受到外部时钟信号的影响,时钟信号越快,计数速度越快;4. 由于同步计数器是由多个触发器级联构成的,其输出在计数过程中可能会出现一定的延迟,需要注意信号的传输时间。

五、实验总结本次实验通过搭建同步计数器电路,我们深入了解了同步计数器的原理和性能特点。

可编程逻辑器件实现四位加减法器

PLD1

Ci

S

A

Co

B

全加器

图7-36 全加器元件符号图

7-37全加器仿真电路的设计工具箱面板

7.3 用可编程逻辑器件仿真设计全加器

7.3.3 仿真验证PLD的全加器电路功能 2.搭接仿真电路,运行仿真

XLC1

AB

PLD1

Ci

S

A

Co

根据存储单元的工作原理不同,RAM分为静态RAM和动态RAM。

7.1 认识半导体存储器

7.1.3 存储器的扩展 1.位数的扩展 存储器芯片的字长多数为一位、四位、八位等。当实际的存储系

统的字长超过存储器芯片的字长时,需要进行位扩展。位扩展可以利 用芯片的并联方式实现,图7-13是用八片1024×1 位的RAM扩展为 1024×8 位RAM的存储系统框图。

项目引导

项目要求:

1.工作任务:用可编程逻辑器件设计四位加/减法器,并进行仿真调 试。

2.电路功能:当输入四位二进制数A3-A0和B3-B0时,通过设置控 制端Sign为0和1分别能实现四位二进制数的加法和减法;输出端S3-S0为 和(加法)或者差(减法),输出端Co为进位(加法)或借位(减法) 信号。

从存储器的角度看,只要将逻辑函数的真值表事先存入ROM,便可 用ROM实现该函数。

用ROM实现逻辑函数一般按以下步骤进行: (1)根据逻辑函数的输入、输出变量数目,确定ROM的容量,选择合 适的ROM。 (2)写出逻辑函数的最小项表达式,画出ROM的阵列图。 (3)根据阵列图对ROM进行编程。

7.1 认识半导体存储器

7.1.1 只读存储器(ROM)

1.ROM的结构

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SHANGHAI UNIVERSITY

数字电子技术课程实践项目

学院机电工程与自动化学院

专业电气工程及其自动化

班级电气7班

学号 11123548

姓名孟蔓菁

用下降沿触发的JK-FF组成四位同步加计数器、异步加计数器一、下降沿触发的JK-FF组成四位同步加计数器

同步加计数器:同步计数器中,所有触发器的CP端是相连的,CP 的每一个触发沿都会使所有的触发器状态更新。

实验电路图:

实验原理:同步计数器中各触发器的CP端输入同一时钟脉冲,因此触发器的翻转状态就由它们的输入信号J、K端的状态决定。

1、时钟方程

CP0=CP1=CP2=CP3=CP

2.驱动方程

3.状态方程

4.状态图

2、列状态转换真值表

6.理论波形图

7.实验波形图

Q

0波形:Q1波形

Q2波形Q3波形

二、下降沿触发的JK-FF组成四位异步加计数器

异步计数器是在做加1计数时是采取从低位到高位逐位进位的方式工作的。

因此其中的各个触发器不是同步翻转的。

按照二进制加

法计数规则,每一位如果已经是1,则再计入1时应变为0,同时向高位发出进位信号,使高位翻转。

实验电路图:

1、时钟信号

CP0=CP

CP1=Q0

CP2=Q1

CP3=Q2

2、驱动方程

J 0=K0= J1=K1= J2=K2= J3=K3=1

3、状态方程

3、真值表

每16个CP循环一周

5、理论波形图

6、实际波形图

Q0波形Q1波形

Q2波形Q3波形。