Lattice fpga工具约束参数详解

fpga管脚约束格式

FPGA管脚约束格式

FPGA(现场可编程门阵列)是一种灵活的集成电路,它可以根据用户的需求进行编程和配置。

在FPGA的设计和实现过程中,管脚约束是一个重要的环节。

管脚约束定义了FPGA内部逻辑块与外部接口之间的连接方式,以确保正确的数据传输和时序控制。

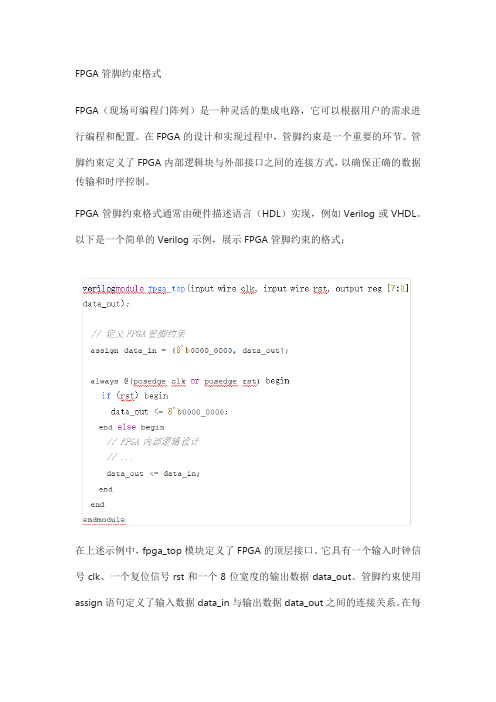

FPGA管脚约束格式通常由硬件描述语言(HDL)实现,例如Verilog或VHDL。

以下是一个简单的Verilog示例,展示FPGA管脚约束的格式:

在上述示例中,fpga_top模块定义了FPGA的顶层接口。

它具有一个输入时钟信号clk、一个复位信号rst和一个8位宽度的输出数据data_out。

管脚约束使用assign语句定义了输入数据data_in与输出数据data_out之间的连接关系。

在每

个时钟上升沿或复位信号上升沿时,内部逻辑会根据需要更新data_out的值,并通过管脚约束将其传递到外部接口。

需要注意的是,上述示例只是一个简单的示例,实际的FPGA管脚约束格式可能因具体的FPGA芯片和应用需求而有所不同。

因此,在实际应用中,需要根据具体的FPGA芯片和设计要求来编写相应的管脚约束代码。

ISE管脚约束设置参数详解5页word文档

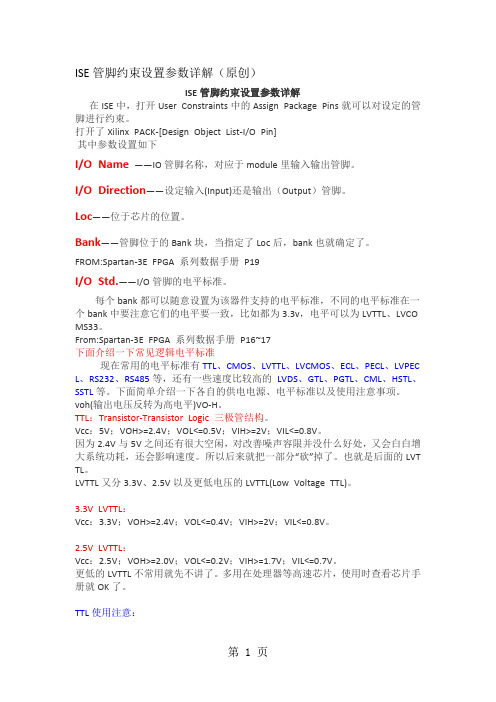

ISE管脚约束设置参数详解(原创)ISE管脚约束设置参数详解在ISE中,打开User Constraints中的Assign Package Pins就可以对设定的管脚进行约束。

打开了Xilinx PACK-[Design Object List-I/O Pin]其中参数设置如下I/O Name——IO管脚名称,对应于module里输入输出管脚。

I/O Direction——设定输入(Input)还是输出(Output)管脚。

Loc——位于芯片的位置。

Bank——管脚位于的Bank块,当指定了Loc后,bank也就确定了。

FROM:Spartan-3E FPGA 系列数据手册P19I/O Std.——I/O管脚的电平标准。

每个bank都可以随意设置为该器件支持的电平标准,不同的电平标准在一个bank中要注意它们的电平要一致,比如都为3.3v,电平可以为LVTTL、LVCO MS33。

From:Spartan-3E FPGA 系列数据手册P16~17下面介绍一下常见逻辑电平标准现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPEC L、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。

下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

voh(输出电压反转为高电平)VO-H。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

所以后来就把一部分“砍”掉了。

也就是后面的LVT TL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。

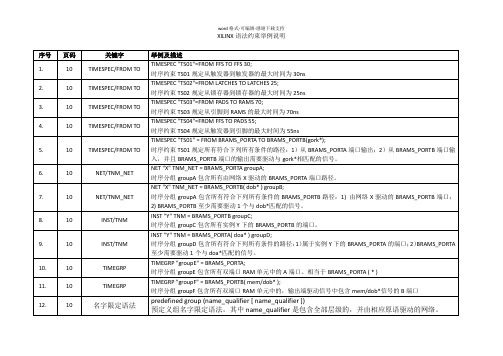

XILINX语法约束举例说明

29

Verilog

always@(current_state or reset)

begin (* parallel_case *) (* full_case *)

case (current_state)

18.

30

Verilog

(* mult_style = "pipe_lut" *) MULT my_mult (a, b, c);

时序分组input_pads是除output_pads分组外的所有引脚。

21.

33

保留字

NET net OFFSET=IN 20 BEFORE CLOCK;错误

NET "net" OFFSET=IN 20 BEFORE CLOCK;正确

NET "$SIG_0" OFFSET=IN 20 BEFORE CLOCK;正确

19.

32

疑问

NET "$SIG_0 MAXDELAY" = 10;

NET "$SIG_1 MAXDELAY" = 12 ns;

疑问:上面是否应将"$SIG_0 MAXDELAY"改为"$SIG_0 "MAXDELAY

20.

33

EXCEPT

TIMEGRP "input_pads"=PADS EXCEPT output_pads;

39.

61

全局输出

偏置约束语法

OFFSET = OUT value1VALID value2AFTER clock;

全局约束,输出信号在clock后value1时间内有效,并且保持最小来自alue2时间。40.

fpga主要参数

fpga主要参数FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有灵活可重新配置的硬件特性。

它可以被程序员用于实现特定的电路功能,适用于各种不同的应用领域。

在选择使用FPGA时,有一些主要参数需要考虑。

以下是一些重要的FPGA参数及其详细说明。

1.逻辑单元数量:逻辑单元是FPGA的基本构建块,用于实现不同的逻辑功能。

逻辑单元的数量决定了FPGA的运算能力和复杂性。

当应用需要进行大规模的并行计算时,逻辑单元数量是一个关键参数。

2. 查找表数量:查找表(Look-Up Table,LUT)是FPGA中最小的逻辑单元。

它可以存储逻辑函数,并在需要时提供输出。

查找表数量越大,FPGA的灵活性就越高,可以实现更复杂的逻辑功能。

3.存储单元数量:存储单元用于存储数据和程序。

它可以是寄存器、存储器或分布式RAM等形式。

存储单元的数量决定了FPGA的数据处理能力和存储容量。

对于需要大量数据存储的应用,存储单元数量是一个重要的考虑因素。

4.I/O接口数量:输入/输出(I/O)接口用于与其他外部设备进行数据交互。

I/O接口数量决定了FPGA连接外部设备的能力,如传感器、存储设备、网络接口等。

对于需要大量连接的应用,例如通信系统或数据采集系统,I/O接口数量是一个重要的指标。

5.时钟频率:时钟频率表示FPGA在单位时间内完成的操作次数。

它决定了FPGA的工作速度和响应性能。

高时钟频率可以使FPGA更快地执行计算任务,但对电路设计和功耗管理提出了更高的要求。

适当选择时钟频率可以平衡FPGA的性能和功耗。

6.资源利用率:资源利用率是指FPGA上实际使用的逻辑资源占总资源的比例。

对于系统设计,资源利用率越高,系统的性能就越好。

低资源利用率可能意味着设计不充分或存在冗余。

因此,在选择FPGA时,需要考虑资源利用率,以确保最佳性能和资源利用。

7.功耗:功耗是FPGA运行时所消耗的能量。

xilinx fpga中时钟输入管脚的约束

xilinx fpga中时钟输入管脚的约束在Xilinx FPGA中,时钟输入管脚的约束是非常重要的,它们可以确保时钟信号的稳定性和一致性,从而保证设计的性能和可靠性。

因此,合理设置时钟输入管脚的约束是进行FPGA设计中不可忽视的一部分。

时钟输入管脚约束主要包括以下几个方面:1.频率约束:时钟输入管脚的频率约束指定了该管脚接收的时钟信号的频率范围。

在设计中,需要根据时钟源的特性和系统的工作要求来设置合适的频率约束。

2.总线延迟约束:在一些应用中,时钟信号可能需要进行时序约束,以确保各个时钟域之间的同步稳定性。

总线延迟约束指定了时钟信号与其他信号的最大传播延迟,这样可以避免时序问题和死锁。

3.约束路径的设置:时钟输入管脚的约束路径设置是确保时钟信号按照设计要求正确到达目标寄存器的关键。

通过设置约束路径,可以规定时钟信号到达目标寄存器的最长路径,确保时钟信号的稳定性,减少时钟抖动和时钟周期不稳定等问题。

4.时钟输入和输出约束:时钟输入管脚还可能有一些其他的约束设置,如时钟输入和输出的相位约束、时钟输入和输出的组合约束等。

这些约束的目的是保证时钟信号的稳定性和相位一致性。

除了上述的基本约束外,还有一些特殊的约束需要注意:1.编译工具约束:在进行FPGA设计时,可以使用Xilinx的编译工具对设计进行优化和约束分析。

通过正确设置时钟输入管脚的约束,可以使编译工具更好地理解设计的时钟域和时序要求,从而提高设计的性能和可靠性。

2.时钟插入延迟约束:在一些高速设计中,时钟插入延迟约束非常重要。

它指定了时钟信号从输入管脚到达目标寄存器之间的最小插入延迟。

通过设置时钟插入延迟约束,可以在设计中引入适当的延迟,从而使时钟信号的到达时间更加可控和稳定。

3.锁定时钟约束:在一些需要时钟同步的设计中,可能需要设置锁定时钟约束。

这个约束规定了时钟信号之间的相位关系,确保它们在设定的相位范围内保持同步。

这对于一些高速通信和信号处理系统中的数据同步非常重要。

FPGA约束的详细介绍

FPGA约束的详细介绍1、约束的目的介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。

所以首先要设计合理,才可能满足约束,约束反过来检查设计能否满足时序。

主要涉及到xilinx vivado xdc约束语法,给出对应的ISE ucf 语法。

另外quatus的语法和xdc几乎兼容,原理都一样。

时序约束中最基本的是时钟,时钟有抖动(jitter),偏移(skew),占空比失真(duty cycle distorTIon)三种特性。

1、抖动,分为周期抖动(cycle jitter),周期差抖动(cycle to cycle jitter)和长期抖动(long term jitter)。

2、偏移和时钟线的长度,时序单元的负载电容和个数有关。

FPGA的全局时钟采用全铜工艺和树状结构,偏移非常小,可以忽略。

3、占空比失真就是高低电平不对称,会吞噬时序裕量。

2、基本的时钟约束最简单的情况,设计只有一个时钟。

这时候需要对这个时钟的周期进行约束,(当然也可以对占空比进行约束,默认为50%)。

如果不对时钟进行约束,我们就不知道自己的设计是否时序收敛。

简单的说,比如系统时钟是200M的,那么周期就是5ns,也就是说信号从一个寄存器出来,经过了一系列的组合逻辑,要在下一个时钟的上升沿到来之前被目的寄存器采样到。

当然考虑到,实际情况还复杂很多。

假如设计里有很多时钟,那么哪些时钟是必须要约束的呢?首先是从端口进入FPGA的时钟。

其他衍生时钟(如通过PLL或者MMCM生成的)跟它是同源时钟,工具会自动推导。

然后是GT的rx_clk和tx_clk必须要约束。

最后是用户自己分频产生的行波时钟(用于简单的低频应用),必须约束。

create_clock -name clk_200m -period 5 [get_ports I_clk200]。

xilinx时序约束

前一段时间调试了xilinx的板子上跑代码,自己加IP核,看了它的约束文件,在网上找了一些讲语法的资料,自己整理了一下,我感觉在你了解了语法之后,确实得好好看一下它自己给出的约束,有些我自己没用到,我就没整理了。

1.约束文件的概念FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF 文件,最后再经过实现后生成PCF 文件。

本节主要介绍UCF文件的使用方法。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。

NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。

PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。

一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。

2.UCF文件的语法说明UCF文件的语法为:{NET|INST|PIN} "signal_name" Attribute;其中,“signal_name”是指所约束对象的名字,包含了对象所在层次的描述;“Attribute”为约束的具体描述;语句必须以分号“;”结束。

可以用“#”或“/* */”添加注释。

需要注意的是:UCF文件是大小写敏感的,信号名必须和设计中保持大小写一致,但约束的关键字可以是大写、小写甚至大小写混合。

在UCF文件中描述管脚分配的语法为:NET “端口名称” LOC =引脚编号;NET "CLK" LOC = P30; “CLK”就是所约束信号名,LOC = P30;是约束具体的含义,将CLK信号分配到FPGA的P30管脚上。

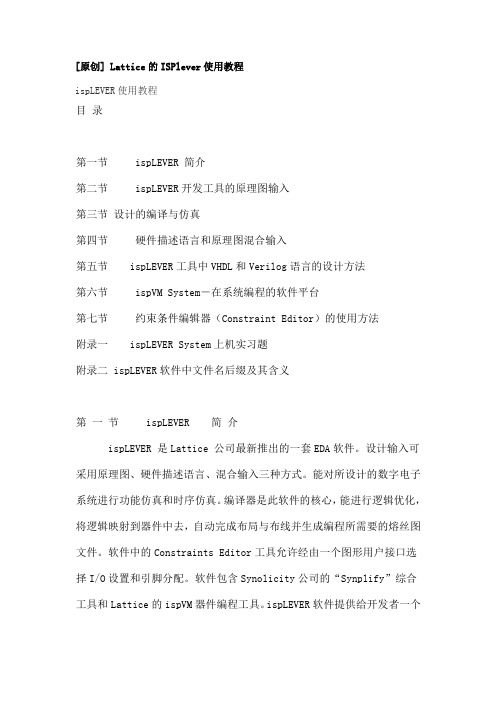

Lattice的ISPlever使用教程

[原创] Lattice的ISPlever使用教程ispLEVER使用教程目录第一节 ispLEVER 简介第二节 ispLEVER开发工具的原理图输入第三节设计的编译与仿真第四节硬件描述语言和原理图混合输入第五节 ispLEVER工具中VHDL和Verilog语言的设计方法第六节 ispVM System-在系统编程的软件平台第七节约束条件编辑器(Constraint Editor)的使用方法附录一 ispLEVER System上机实习题附录二 ispLEVER软件中文件名后缀及其含义第一节 ispLEVER 简介ispLEVER 是Lattice 公司最新推出的一套EDA软件。

设计输入可采用原理图、硬件描述语言、混合输入三种方式。

能对所设计的数字电子系统进行功能仿真和时序仿真。

编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线并生成编程所需要的熔丝图文件。

软件中的Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。

软件包含Synolicity公司的“Synplify”综合工具和Lattice的ispVM器件编程工具。

ispLEVER软件提供给开发者一个简单而有力的工具,用于设计所有Lattice可编程逻辑产品。

软件支持所有Lattice公司的ispLSI 、MACH、ispGDX、ispGAL、GAL器件。

ispLEVER 工具套件还支持Lattice新的ispXPGATM和ispXPLDTM产品系列,并集成了Lattice ORCA Foundry设计工具的特点和功能。

这使得ispLEVER的用户能够设计新的ispXPGA和ispXPLD产品系列,ORCA FPGA/FPSC系列和所有Lattice的业界领先的CPLD产品而不必学习新的设计工具。

软件主要特征:1. 输入方式* 原理图输入* ABEL-HDL输入* VHDL输入* Verilog-HDL输入* 原理图和硬件描述语言混合输入2. 逻辑模拟* 功能模拟* 时序模拟3. 编译器* 结构综合、映射、自动布局和布线4. 支持的器件* 含有支持ispLSI器件的宏库及MACH器件的宏库、TTL库* 支持所有ispLSI、MACH、ispGDX、ispGAL、GAL、ORCA FPGA/FPSC、ispXPGA和ispXPLD器件5. Constraints Editor工具* I/O参数设置和引脚分配6. ispVM工具* 对ISP器件进行编程软件支持的计算机平台:PC: Windows 98/NT/2000/XP第二节 ispLEVER开发工具的原理图输入I. 启动ispLEVER(按Start=>Programs=>LatticeSemiconductor=>ispLEVER Project Navigator)II. 创建一个新的设计项目A. 选择菜单File。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1-100

1-99

Routing Resource Optimization Routing Delay Reduction Passes PLC Input Lim6 0-6 Off, Low, Medium, High

PLC Input Neighbor Size

Command Line Options

d Timing Performance Listed) July 20, 2006 Ver 1.0 Analysis

Specifies the global design frequency (in MHz). Improve Fmax.

Specifies the Area mode. For Precision: Specifies the encoding style to use with the design. For Synplify: Enables/disables the FSM Compiler and controls the use of FSM synthesis for state machines. When this is set to True (default), the FSM Compiler automatically recognizes and optimizes state machines in the design. It can improve area optimization if turn on, •Binary - Most area efficient. Will use a minimum number of registers to implement the state vector resulting in the smallest overall area. Binary is generally not the optimal encoding for FPGAs because of the abundance of registers these devices offer. Precision will use Binary for small FSMs in FPGAs. Turn on when the number of states is less than 5. •One-hot - Provides the fastest clock to out timing. One-hot FSM encoding uses a separate register for each bit of the state vector. The state register is connected directly to the FSM outputs providing the fastest clock to out timing. Onehot FSMs generally result in the fastest performance and are the most common encoding selected by Precision's Auto selection. Turn on when the number of states is > 5 and <= 16. •Two-hot - Offers a compromise between the area advantages of binary and the performance advantages of one-hot. Two hot FSM uses 2 to True, output bits driven to a will not one to define the decoding. For If it is set if you have an If this property is set register Synplify or Precision logical add I/O buffers to your design. example, to False (default), the synthesis tool will insert I/O buffers to your design. For hierarchical and mixed design, Disable_IO_Insertion should befanout i.e, the synthesis. When the specified fanout limit is achieved, logic will be duplicated and Fmax may Controls false, during I/O buffers should be added. be improved. Large fanouts may cause long delay and congestion, less resource. Setting this property to True causes the advanced retiming algorithms to be run. The default is False. Setting this property to True transforms Set/Reset on DFFs to Latches. The default is True.

1,2,…,5

Routing Passes Disable Timing Driven Routing Options Placement Iterations

1,2,…,30

True/False 0,1

0-99

Placement Start Point Placement Save Best Run

True/False Auto (default), Binary, One Hot, Two Hot, Random, or Gray for Precision. Treu/False for Synplify

Condition

the Area property is set to False.

Synthesis, Map, PAR Properties (Only Those Impact on Area and Timing Performance Listed) July 20, 2006 V Value Synthesize VHDL/Verilog File Property Frequency Area FSM Encoding

Sets the relative density (of available PFUs) at which the Programmable Functional Units (PFUs) within a device are to be packed. The mapper translates the factor into number of PFUs, that is, the number is the percentage of slices to pack to. For example, 90 means pack to 90% of slices on the chip (quite spread). 10% means pack to 10% of slices (quite dense)will not pack components from different top level modules into the same PFU. This affords PLACE & ROUTE MAP better placement choices through improved logic grouping. This Text property is made available after an initial design run. It is used to move registers across combinational logic to balance timing according to the constraints of tSU (INPUT_SETUP), tCO (CLOCK_TO_OUT), and fMAX (FREQUENCY). Retiming supports six timing preferences: INPUT_SETUP, CLOCK_TO_OUT, FREQUENCY, MULTICYCLE, MAXDELAY, and PERIOD. Other preferences have no effect on retiming. This property can take two options: EFFORT: Retiming Level of Effort option. Takes integer values 1-6, with 1 being the least effort and 6 the most. Default value for all devices is 4.High effort value may not always provide best results, as it may incur higher run time and register count. DETOUR: Retimingtiming-driven logic collapsing andDetour. Takesto further optimize the critical paths.least severity Allows you to apply estimation on severity of Routing optimization integer values 1-6, with 1 being the Timing Driven Mapping reads the preference file and calculates the slacks for all constrained paths. The mapping optimizes the critical paths based on the slack distributions. Specifies the effort level of the design from 1 (simplest designs) to 5 (most complex designs). The level is not an absolute; it shows instead relative effort. After you use PLACE & ROUTE for a while, you will be better able to estimate whether a design is simple or complex. If you place and route a simple design at a complex level, the design will be placed and routed properly, but the process will take more time than placing and routing at a simpler level. If you place and route a complex design at a simple level, the design may not route to completion or may route less completely (or with worse delay characteristics) than at a more complex level.