高精度轨对轨CMOS峰值检测电路设计

精密峰峰值检测电路

精密峰峰值检测电路

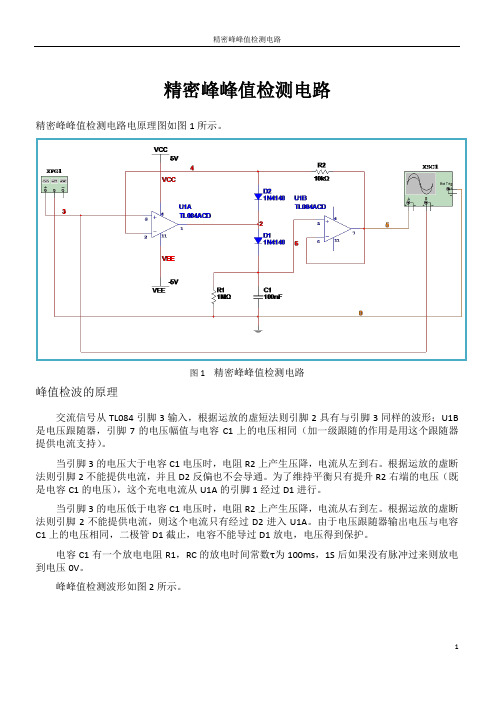

精密峰峰值检测电路电原理图如图1所示。

图1 精密峰峰值检测电路

峰值检波的原理

交流信号从TL084引脚3输入,根据运放的虚短法则引脚2具有与引脚3同样的波形;U1B 是电压跟随器,引脚7的电压幅值与电容C1上的电压相同(加一级跟随的作用是用这个跟随器提供电流支持)。

当引脚3的电压大于电容C1电压时,电阻R2上产生压降,电流从左到右。

根据运放的虚断法则引脚2不能提供电流,并且D2反偏也不会导通。

为了维持平衡只有提升R2右端的电压(既是电容C1的电压),这个充电电流从U1A的引脚1经过D1进行。

当引脚3的电压低于电容C1电压时,电阻R2上产生压降,电流从右到左。

根据运放的虚断法则引脚2不能提供电流,则这个电流只有经过D2进入U1A。

由于电压跟随器输出电压与电容C1上的电压相同,二极管D1截止,电容不能导过D1放电,电压得到保护。

电容C1有一个放电电阻R1,RC的放电时间常数τ为100ms,1S后如果没有脉冲过来则放电到电压0V。

峰峰值检测波形如图2所示。

图2 精密峰峰值检测电路工作电压波形。

高精度CMOS峰值保持电路设计

图 9 误差率仿真结果

图 10 版图设计 ( 下转第 990 页,Continued on page 990)

科学出版社,1994. [4]管兴胤,张子川,刘君红. 精确测量光电倍增管最大

脉冲线性参数的实验研究[J]. 原子能科学技术, 2009,43( 7) : 640 - 643.

[5]潘洪波,欧阳晓平,刘德林,等. 新型超快光电辐射 探测器研制[J],原子能科学技术,2009,43( 1) : 81 - 84.

保持电容连接到放大器的正输入端故此时放大器的正输入端电压值大于负输入端电压放大器的输出电压迅速变大当放大器输出电压t大于参考电压时比较器发生翻转从而使d2触发器发生翻转控制开关s1和s2打开开关s3s4及s5闭合

第 31 卷 第 9 期 2011 年 9 月

核电子学与探测技术 Nuclear Electronics & Detection Technology

及 S5 闭合。

图 1 电路整体结构

信号,对 整 个 电 路 进 行 reset,控 制 开 关 S6 闭 合,使保持电容上电压等于 VB ( VB 的大小一般 设置为小于等于输入信号的基线电压值) ,完 成对整个电路的 reset,直至下个有效信号到来 为止。当下个有效信号到来时,促使 D1 触发 器发生 翻 转,断 开 开 关 S6,使 整 个 电 路 进 入 “写”状态。如果两次 CDN 之间到来多个有效 输入信号,该电路只对第一个到来的信号进行 保持,仿真结果如 6 所示。

959

图 5 “读”状态电路时电路简化图

图 7 仿真波形图

图 8 输入、输出幅度对应图

图 6 reset 信号产生时序仿真图

为 5 mV 左右,但误差率降为 1. 2% ,随着输入 信号的进一步增加,误差电压进一步减小,误差 率也相应下降到 1% 之内。当输入信号峰值达 到 3. 1 V 时( 本电路采用 3. 3 V 电压供电) ,放 大器不能正常工作,电路失效。虽然在小信号 时误差率较大,但我们可以看出在小信号时产 生的误差电压值几乎为一个定值 5 mV 左右, 故我们可以在电路最终应用时对小信号输出电 压进行修正,完全可以使误差率小于 1% 。

峰值检测电路

一、前言峰值检测电路(PKD,Peak Detector)的作用是对输入信号的峰值进行提取,产生输出V o = Vpeak,为了实现这样的目标,电路输出值会一直保持,直到一个新的更大的峰值出现或电路复位。

峰值检测电路在AGC(自动增益控制)电路和传感器最值求取电路中广泛应用,自己平时一般作为程控增益放大器倍数选择的判断依据。

有的同学喜欢用AD637等有效值芯片作为程控增益放大器的判据,主要是因为集成的方便,但个人认为是不合理的,因为有效值和信号的正负峰值并没有必然联系;其次,实际应用中这类芯片太贵了。

当然,像电子设计竞赛是可以的,因为测试信号总是正弦波,方波等。

(本文参加了TI公司的博文比赛,觉得还行的话,希望大家帮顶一下、回复一个,谢谢大家,我会更努力的:-)二、峰值检测电路原理顾名思义,峰值检测器(PKD,Peak Detector)(本文默认以正峰值检测为例)就是要对信号的峰值进行采集并保持。

其效果如下如(MS画图工具绘制):根据这样的要求,我们可以用一个二极管和电容器组成最简单的峰值检测器。

如下图(T INA TI 7.0绘制):这时候我们可以选择用面包板搭一个电路,接上信号源示波器观察结果,但在这之前利用仿真软件TINA TI进行简单验证会节省很多时间。

通过简单仿真(输入正弦信号5kHz,2 Vpp),我们发现仅仅一个二极管和电容器组成的峰值检测器可以工作,但性能并不是很理想,对1nF的电容器,100ms后达到稳定的峰值,误差达10%。

而且,由于没有输入输出的缓冲,在实际应用中,电容器中的电荷会被其他部分电路负载消耗,造成峰值检测器无法保持信号峰值电压。

既然要改进,首先要分析不足。

上图检测的误差主要来自与二极管的正向导通电压降,因此我们可以用模电书上说的“超级二极管”代替简单二极管(TINA TI 7.0绘制):从仿真结果来看,同等测试条件下,检测误差大大减小。

但我们知道,超级二极管有一个缺点,就是Vi从负电压变成正电压的过程中,为了闭合有二极管的负反馈回路,运放要结束负饱和状态,输出电压要从负饱和电压值一直到(Vi+V二极管)。

高精度CMOS峰值保持电路设计

两种工作状态的误差分析

Vi

-

M1

+

Vo

-

+

ZL

Ch

Ch

(a)“写”状态

误差Verror

VGP VO,CM AO

VOFF

1 CMRR

2V1

VDD 2

(b)“读”状态

误差Verror

VIP VO,CM AO

VOFF

1 CMRR

2V1

VDD 2

最终误差 Verror

VO

- VIP

VGP VIP AO

P (VDD VT)2

(1/ 3 1/ 5)

比较器的设计

前置放大

锁存

器

器

自偏置差 分放大器

输出驱动级

比较器仿真波形

版图设计

一通道

二通道

三通道

四通道

偏置 电路

面积: 1280um*1280um 工艺: chrt0.35um CMOS 电源电压:

3.3V 一个通道的功耗: 小于1mW

后仿真结果

谢 谢!

以忽略。

增益为48.8DB

单位增益带宽为70M。

vip

out

vss

电流镜管子大小的选择

• M1管的尺寸需要越小越好,从而减小对输 出精度的影响。

• M0管与电路在“写”状态时环路的稳定性 有关。通过分析可以推算出

W

1

A0,MAX

2VI'MAX L

E (VDD VT)2

C gp Cox

AO,MAX

2VI'MAX L2

VB

• “写”状态: 开关S3, S4 及 S5 打开 ,开关S1 和 S2 闭合。

轨到轨CMOS运算放大器的研究与设计

重废邮虫盍堂亟±论塞簋三童熟到魍£MQS运簋趑太墨的县佳遮让第三章轨到轨CMOS运算放大器的具体设计运放的输入电位通常要求高于负电源某一数值,而低于正电源某一数值。

经过特殊设计的运放可以允许输入电位在从负电源到正电源的整个区间变化,甚至稍微高于正电源或稍微低于负电源也可以。

这种运放称为轨到轨(Rail—to—Rail)输入运算放大器。

3.1轨到轨运放的输入级设计3.1.1传统的输入级设计通过对差分放大器的直流性质研究我们发现,NMOS差分对管的输入共模电压可以达到电源电压%仃,同时可得PMOS差分对管的共模输入电压可以无限制的接近地电压,上面的直流工作点都可以通过对管子的器件特性的选择来选定。

但是无论如何我们不可能让NMOS差分对管的共模电压接近于地电压,同理,我们也不能让PMOS差分对管的共模电压接近于电源电压%D,这些是因为器件本身的性质决定的。

于是我们不可能通过只选择其中的任何一个类型的管子而实现共模输入电压达到轨到轨的要求。

然而我们通过上面的分析可以发现,假如两种类型的管子配合着相互使用,于是问题则可以迎刃而解。

如此输入级的共模输入电压范围就可达到运放对输入级电路轨到轨的要求。

通过上面的分析我们得到互补式运算放大器的差分输入电路结构如图3.1所示。

从下图中我们得出:当只有N/dOS差分对导通的时候,N/dOS差分对管Ml,M2的输入共模范围为‰一%+‰;当只有PMOS差分对管处于导通状态的时候,M3,M4作为输入级其共模的输入范围为‰一K,。

+‰;通过上面的分析我们知道两种差分对管实现了优缺点的互补,我们就完成了共模输入电压范围扩大的目的,此时为坎。

~%。

,如此一来轨到轨输入级结构的大体思路已经成行,我们同时可以计算出可以使这对差分对管正常工作的最小的电源电压,其电压值大小是:‰nlin=‰+‰+2‰。

上面的式子中‰,%分别是PMOS晶体管和NMos晶体管的栅源电压;‰是16尾电流管的饱和电压,这里尾电流管子是采用电流镜技术。

CMOS模拟集成电路设计_ch9运算放大器3——高增益、轨到轨、全差分运放

共模反馈

理想情况:I 7 I 8 I 9 实际:工艺偏差、沟道长度调制 I 7 I8 I9

若I 7 I 8 I 9 VX 、VY 上升,M 5 ~ M 8退出饱和 若I 7 I 8 I 9 VX 、VY 下降,M 1 ~ M 4退出饱和

共模输出电平对器件特性、失配敏感;增益越大,越敏感。 所以全差分的高增益放大器需要共模反馈电路来保障正确的工作电平

高增益运算放大器

辅助放大器的实现方式

高增益运算放大器

VX VGS 3 Vout VGS 3+Vdsat 2 辅助放大器减小了输出 摆幅

采用PMOS辅助放大器 可以克服这个问题

高增益运算放大器

共源共栅差分对中增益 的提高 (a ) : 使用两个独立的辅助放 大器 (b) : 使用全差分辅助放大器

高增益运算放大器

折叠共源共栅差分放大 器用做辅助放大器 VX 允许的最小电压为 Vdsat 1 Vdsat,不受辅助放大器限制

高增益运算放大器

性能比较

增益 中 中 高 高 摆幅 速度 功耗 噪声 中 高 低 低 中 高 中 高 低 中 中 中 高 中 低 中

套筒式共源共栅 折叠式共源共栅 两极运放 增益提高运放

CMFB的原理结构图

共模检测电路检测出共模电平,与VREF(一般为VDD/2)进行比 较,如果共模电平大于VREF ,则增大尾电流,从而降低共模电 平。如果小于,则相反。即通过负反馈使共模电平稳定在VREF

典型的运放结构和种类 • • • • • 筒套式共源共栅运算放大器 折叠式共源共栅运算放大器 高增益运算放大器 轨对轨运算放大器 全差动运算放大器

轨对轨运算放大器

PMOS、NMOS的输入范围分别在上下轨受限பைடு நூலகம்

高精度测量与控制电路设计

测量技术的发展历程

模拟测量阶段

早期的测量技术主要采用模拟测量方 式,如机械式、电感式等,精度和稳 定性较低。

数字化测量阶段

智能化和网络化测量阶段

现代测量技术正朝着智能化和网络化 方向发展,通过集成传感器、微处理 器、通信等技术,实现远程、实时、 自动测量。

电路设计的优化方法

优化元件选择

根据实际需求选择性能优良、精度高 的元件,是提高电路性能的基础。

布局与布线

合理的布局和布线可以减小信号干扰 和寄生效应,提高电路的稳定性。

电源与接地

稳定的电源和良好的接地是保证电路 正常工作的关键,需充分考虑电源和 接地设计。

仿真与调试

通过仿真软件对电路进行仿真分析, 并在实际制作前进行调试,可以及时 发现并修正设计中的问题。

控制电路的设计方法

确定控制目标

根据实际需求和系统要求,明确控制目 标,如调节温度、压力、速度等。

设计控制电路

根据控制算法和控制目标,设计控制 电路,包括电源电路、信号处理电路

、执行电路等。

选择合适的控制算法

根据控制目标,选择合适的控制算法 ,如PID控制、模糊控制、神经网络 控制等。

测试与调试

完成控制电路设计后,进行测试和调 试,确保控制电路的稳定性和可靠性 。

多功能化测量与控制技术

总结词

多功能化测量与控制技术是指将多种测量和控制功能集成在一个系统中,以实 现更全面的测控应用。

详细描述

多功能化测量与控制技术能够减少系统成本和复杂性,提高测控的可靠性和精 度,适用于环境监测、能源管理、医疗诊断等领域。

一种轨至轨CMOS运算放大器的设计

电了在沟道 表 面的迁 移率 , / =2 7 i x . 。如果 M 9的沟道宽长 比设计为 M1 2的 27倍 , B = . 则 N B, 再通过 电流源尾部控 制电路 的作用 , I 使 = I, 那么就可保证输人级工作在第一和第三 区域

2 1 运放 输入 级 的设计 .

C O 运算放大器的输入输出信号的动态范 围大 M S

大减 小 。为 了提 高 运 放 的性 能 , 大输 入 输 出信 增 号 的动态 范 围 , 最好 能达 到整 个 电源 电压 范 围 , 即 轨 到轨 ( 2 R i—t R R: a l o—R i , 须 对 运 放 的 差 a )必 l 分输 入级 和输 出级 进 行 改 进设 计 。对 于输 入 级 , 恒跨 导 的 R R设计 是研 究 的热 点 , 现 的方 法 很 2 实 多, 比较 常用 的一 种 方 法是 利 用 偏 置 回路来 保 持 尾 电流平 方根 之和 的恒定 。而输 出级 多采 用共 源

因此 , 由上可 见 整 个 输人 级 的共模 输 人 范 围 在 V 和V ∞之 间 。

1 当共模输人 电压接近负 电源时 , P ) 仅 沟输 人对导通 , 共模输人电压范围为 :

V。 <V D— st Vsp 。<V D Vda— g () 1

其 中, 为共模输人 电压 , 唧为 P管的栅 V V

维普资讯

第 2 第 3期 5卷 20 0 7年 9月

誉 篥

瓣蒌

V0 . 5 No 3 12 . Sp 20 e .0 7

JC E I H NGDI ANLU ONGXU T N

一

种 轨至 轨 C S运算 放 大 器 的设 计 MO

维普资讯

ห้องสมุดไป่ตู้囊

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1引 目

峰值检测电路是将某一时间段内信号的最值 反映出来,遇到信号峰值就跟随,若没有就保持.其 工作状态主要包括跟踪、保持和复位,可以广泛应 用于信号采集和处理[1]、RF功率运放(PAs)的反 馈保护系统[2]、仪器仪表、医疗、自动控制等众多领 域,如用来实现波形的毛刺捕捉、冲击信号峰值检

1. 带反馈的闭环峰值检测电路工作原理如 下:

a.在峰值到来时,Ampv 1输出为正,Vo。一 AU>V。,M2开关管导通,Ampvl的反馈网络 M2一Ampv2一R使输入端之间保持虚短路,R无电 流通过,此时

VⅫ一U3=V以=Ul—V白=

U:一儿一AU—亿;

b.峰值下降时,Ampvl输出下降,M2管截止,M1

一种带反馈的闭环峰值检测电路如图1所示, 该电路中Ampvl可提供对电容的快速充放电电 流和使输入电压信号放大;Ampv2为缓冲器,与电 阻R引入反馈回路;M1防止U。与u。偏离太远, 且防止Ampvl进入饱和状态而影响速度以及检 测精确度;M2是控制电容充放电通路的开关; CAP为电容存储器;Rst为复位开关,控制峰值检 测复位.

同【] 精度轨对轨CMOS峰值检测电路设计

王开贤,邬齐荣,高 鑫,李美光,汤恩松

(四JII大学物理科学与技术学院微电子技术四川省重点实验室,成都610064)

摘 要:设计一种高精度轨对轨CMOS峰值检测电路.基于信号“先缩小后放大”,在MOS采

样开关管控制下电源对存储电容充电,该电路实现了轨对轨峰值检测,降低了检测电路的工作 电流,提高了MOS开关管的速度和峰值检测的精度.该电路设计基于CSMC 0.5 ktm CMOS 工艺,采用了5 V单电源,检测精度小于1 mV,检测电压范围为0~5 V,整个检测电路的静

孺疆蕞 ‰一V肋一y删一

@’

从上式可以看出,当t—o。,V。一VDD—V措这是 因为当V。,接近VDD—V丁H时,NMOS的驱动电压 趋近零,使得对存储电容器CAP的充电电流减小 到可以忽略不计.由此可见,MOS开关有一个严重

的缺点:如果输入信号的电平接近V肋,那么由于 MOS开关得到的输出信号就不能跟踪输入信号, 其输出信号的最大电压略小于V肋一、厂州,其中 V掰与MOS开关管的性能及所采用的工艺有关. 实验测得该电路输出的最大电压约为3.64 V.而 且该电路直接由开关管控制对存储电容的充电,充 电速度慢,影响了采样的精度,其采样延迟约为10 肚s,精度约为10 mV.

我们设计了一种高精度轨对轨CMOS峰值检 测电路,适用于甚低频信号的峰值检测.该电路基 于CSMC 0.5肿n CMOS工艺,整体电路功耗低, 其静态电流消耗约为2 mA;基于信号“先缩小后 放大”的设计机理和存储电容充放电系统,该电路 实现了电压信号轨对轨峰值检测,降低了检测电路 的工作电流,提高了MOS采样开关管的速度和峰 值检测的精度;其正常工作频率为0.1 Hz~10 KHz.因此,该峰值检测电路适用于精度要求高的 甚低频信号峰值检测,如低频冲击信号强度的检 测,水流流动过程瞬间压力变化信号检测等.

态电流消耗为2 mA,正常工作频率为0.1 Hz~10 KHz.

关键词:峰值检测;轨对轨;采样;CMOS差动放大器;同相比例运算电路

中图分类号:047

文献标识码:A

文章编号:0490—6756(2009)06—1702—07

High-。precision rail-·to。。rail CMOS peak detector circuit design

此外,运放失调会影响电路精度,而且该峰值 检测电路的工作频率大概是10 Hz~1 KHz,这就 大大限制了该峰值检测电路的应用领域. 2.2高精度轨对轨CMOS峰值检测电路原理

高精度轨对轨CMOS峰值检测电路设计基于 上述带反馈的闭环峰值检测电路的基本思想,采用 “先缩小后放大”的方法,即输入电压信号经电阻分 压网络使得信号幅度缩小,再经峰值检测电路检测 信号的峰值,接着将检测到的信号输入到一个同相 比例运算电路放大,恢复原信号幅度,最后输出,从 而完成某个时间段内峰值检测过程.

其基本电路结构如下:

图2 高精度轨对轨CMOS峰值检测电路原理图 Fig.2 High—Frccision rail—to-rail CMOS peak detector

circuit schematic diagram

由图2可知,高精度轨对轨CMOS峰值检测 电路由电阻分压网络、闭环峰值检测电路、同相 比例运算电路、电容存储器、复位电路构成.其 中:R。与R:构成电阻分压结构,使输入电压降 低;Ampvl可提供对采样一保持电路的快速充放电 电流和使输入信号放大;Ampv2作为电压跟随器, 并引入反馈回路;M1防止U。与U。偏离太远,且 防止Ampvl进入饱和状态而影响速度以及检测 精确度;M2是对电容器充电的采样开关管,控制

收稿日期 基金项目 作者简介 通讯作者

2008·-09..20

IⅡUll大学首届“大学生创新性实验计划”基金项目重点项目[20073 王开贤(1984一),男,海南海1:3人。2004级,微电子学专业(IC设计方向)毕业. 邬其荣.E-mail:wuqi5@163.coin.

万方数据

第6期

王开等:高精度轨对轨CMOS峰值检测电路设计

测[3]、轴承振动噪声的峰值检测[41等.因此峰值检 测器有着广泛的市场需求,且随着电子产业和信息 产业的不断发展,对信号的采集处理方面的要求愈 加突出,它将发挥愈来愈大的作用.

传统峰值检测电路采用放大器和分立二极管 加电容组成充放电电路,并利用二极管的单向导 通性和电容器的存储作用构成检测电路.但这种峰 值保持电路的线性差、通频带窄,故在很大程度上

导通,Ampvl的反馈网络M1,此时,儿=V白一 K,电容器C保持着电压峰值.

2. NMOS采样开关管[10]

假设U。为yh,U。为%,那么由图1可知,

由于NMOS开关管的栅极和漏极电位相同,MOS 管处于饱和区.在饱和区,漏极电流为:

J。一百1.£z。C。W(VDD一儿一V州)2(1)

万方数据

四大学学报(自然科学版) Journal of Sichuan University(Natural Science Edition)

Nov.2009 V01.46 No.6

doi:103969/j.issn.0490—6756.2009.06.026 ·-.】‘

阈值电压L,而且当输入信号的峰值小于n时,

二极管将截止,可见此电路不能用于小信号(< V。)的峰值检测,而且二极管开启电压受温度影响 较大.另外,电容C直接与后续电路相连,易受其 影响引起电荷泄露,保持时间、精度无法保证等.

R

Fig.1

图1带反馈的闭环峰值检测电路

Closed loop peak detector circuit with feedback

万方数据

第6期

王开等:高精度轨对轨CMOS峰值检测电路设计

当R,=R:时,有:

2峰值检测电路基本原理

峰值检测的基本原理,主要包括信号跟随、信 号保持、信号复位等.即当输入信号n增大时,电 路对其采样,并使输出V。。能够很好的跟随输入; 当输入信号V。减小时,电路进入保持阶段,即保持 前一个峰值并输出;当n再次大于此保持电压时, 电路继续跟踪y加进行采样;当复位信号到来时,

儿放电归零,然后开始采样一保持的下一周期.

W-ANG Kai—Xian,WU Qi—Rong,GAO Xin,LI Mei—Guang,丁ANG En—Song

(Micro-electronics Technology Sichuan Key Laboratory,School of Physical Science and Technology,Sichuan University,Chengdu 610064,China)

1703

不能适应当今电子产品的发展趋势.在国外,美国 ANALOG DEVICE公司的PKD01峰值检测器[5] 采用跨导型运算放大器,因而具有响应速度快、线 性好、检测峰值范围宽等特点印].PKD01代表了目 前国际上峰值检测器相关产品的领先水平,并得以 应用在大量的电子系统中.然而,PKD01峰值检测 器采用BICMOS工艺,双电源,对于大多数单电源 系统造成资源浪费,高达40美元的价格极大削弱 终端产品的竞争力,而且其主要应用于军事领域. 对比而言,国内虽然对峰值检测系统的研究不断有 所改进,但是已有的峰值检测系统大多采用国外的 芯片搭建电路,缺乏自主创新品牌,如传统的模拟 峰值检测器便以美国NS公司的采样保持器 LF398H芯片为核心[7],即将被测信号经传感器变 为电信号,再经放大器放大、LF398采样/保持后输 出.而且生产工艺大多局限于双极型晶体管,这样 功耗大,成本高,性能差.目前,国内峰值检测的研 究以南开大学提出高频CMOS峰值检测电路方案 为先进代表[8],该设计基于中芯国际0.35仁m标 准CMOS工艺,但其主要适用于射频信号和基带 信号的峰值检测,不适合甚低频信号的峰值检测.

Abstract:A high—precision rail—to—rail CMOS peak detector circuit is designed.Based on that the signal is zooming out and in,and that the power supply can charge the storage capacitance under the control by MOS sample switch,the circuit could achieve rail—to—rail peak detector,lower the working current of the detection circuit,and improve the velocity of MOS switch and the precision of peak detector.The circuit design is based upon CSMC 0.5 btm CMOS technology,using 5 V single power supply.The detection precision is less than 1 mV,the range of detection voltage is 0~5 V,the static current dissipation is 2 mA,and the normal working frequency is 0.1 Hz~10 K Hz. Key words:peak detector,Rail—to—Rail,sample,CMOS Differential—Amplifier,in—phase scale operation