高速信号抖动测试解决方案

jitter抖动(相位噪声)的概念及其测量方法(EyeDiagram)

抖动的概念及其测量方法摘要:在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

本文介绍了时间抖动(jitter)的概念及其分析方法。

关键字:时间抖动、jitter、相位噪声、测量一、引言随着通信系统中的时钟速率迈入GHz级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3GHz 以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

二、时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。

但不幸的是,这种信号并不存在。

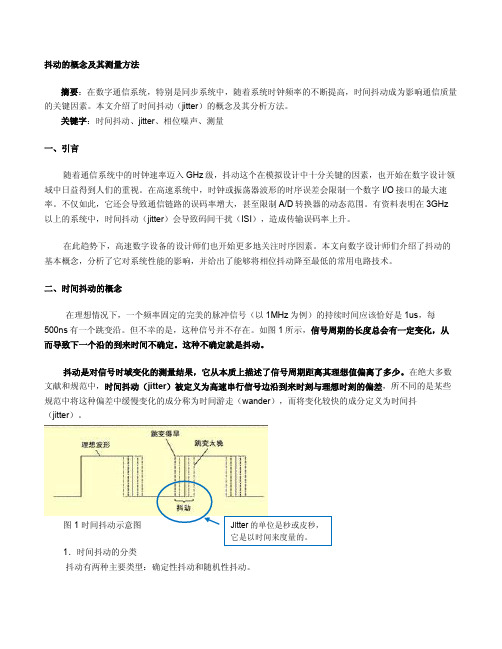

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。

随机抖动是指由较难预测的因素导致的时序变化。

例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。

电路设计流程如何应对高速信号传输与时延问题

电路设计流程如何应对高速信号传输与时延问题高速信号传输与时延问题是电路设计流程中常见的挑战。

在设计过程中,若不能有效地处理这些问题,可能会导致信号失真、时钟偏移和系统错误等不良后果。

因此,本文将介绍如何应对电路设计过程中的高速信号传输与时延问题。

一、信号传输问题的原因及影响高速信号传输问题主要源于信号的传输速度快、频率高、时钟精度要求高等特点。

以下是几个常见的信号传输问题及其影响:1. 时钟抖动:时钟抖动是指时钟信号频率的不稳定性,可能导致数据误差、时序错误等问题。

2. 串扰:高速信号传输时,信号之间可能发生串扰,导致信号失真。

3. 端口反射:当信号到达传输终点时,可能会发生端口反射,造成信号波形的失真和干扰。

二、解决高速信号传输问题的方法为了解决高速信号传输过程中遇到的问题,设计师可以采用以下方法:1. 时钟源的优化:合理选择时钟源,并增加时钟源的稳定性和精确度,可有效减少时钟抖动。

2. 信号完整性设计:利用滤波器、终端阻抗匹配和屏蔽罩等方法,避免信号之间的串扰,提高信号传输的准确性。

3. 驱动电流的控制:通过控制驱动电流的大小,能够减少端口反射产生的信号波形失真和干扰。

4. 延时补偿技术:通过引入延时补偿电路,可以对超高速信号进行时延补偿,以确保各个信号的同步传输。

三、电路设计流程中的注意事项在电路设计流程中,设计师需要注意以下几个方面:1. 信号完整性分析:在设计开始之前,应对电路进行信号完整性分析,包括信号的传输路径、时延要求、时钟精度等因素,为解决高速信号传输问题做准备。

2. 仿真与验证:在设计过程中,可以通过使用仿真工具对电路进行验证,以确定设计方案的可行性,避免出现一些隐蔽的高速信号传输问题。

3. 布局与布线规范:合理的布局和布线有助于降低信号传输过程中的串扰和反射等问题。

设计师应遵循相关的布局和布线规范,确保设计的完整性。

4. 时延分析与优化:通过时延分析工具,对信号传输过程中的时延进行评估和优化,以满足设计要求。

Jitter_数字信号抖动的测试

f 此图是频谱图,从图上

可以很容易的分析出抖 动的频率分布情况,从 而帮助找到抖动的根 源,去除抖动,指导电 路调试。

35

浴盆曲线分析

f 水平轴显示 BER Eye

Opening,垂直轴为累 积的bit数

f 此图显示误码率及累积

次数的曲线图,从图上 可以很容易的分析出 BER必须使用很 长存储深度捕获数据, 才能发现数据的变化规 律

29

周期趋势统计分析

f 水平轴显示每一个测量

点,垂直轴为测量的数 值

f 右上方显示光标值

f 此图可呈现每一个周期

的抖动偏移量,从而了 解此时钟信号的周期趋 势

30

抖动滤波(Jitter3 V2新功能)

31

滤波器模型

可以根据需要设置滤波器模型的 参数,对时间趋势图或周期趋势图 进行低通滤波,带通滤波,高通滤 波分析不同频段的抖动趋势。

32

抖动滤波应用:用5MHz的截止频率进行低通滤波

33

抖动滤波应用: 用35K的截止频率进行低通滤波

34

抖动频谱统计分析-追溯抖动根源

f 水平轴显示抖动频率,

垂直轴为每一个频率点 抖动幅度

直方图(Histogram)统计分析 时间趋势(Time Trend)统计分析 周期趋势(Cycle Trend)统计分析 抖动频谱(Spectrum)统计分析 浴盆曲线(BathTub)统计分析

25

测量参数

f TDS7000系列示波器配合

TDSJit3应用软件

f 测量参数包括: – 时钟(10项) – 数据(4项) – 时钟-数据(3项) – 通用(8项) 共 4类25项参数 f 一次可同时测量任意6项参

15

抖动测量的三种方法

抖动测量三种有效方法只要测试数据通信IC或测试电信网络,就需要测试抖动。

抖动是应该呈现的数字信号沿与实际存在沿之间的差。

时钟抖动可导致电和光数据流中的偏差位,引起误码。

测量时钟抖动和数据信号就可揭示误码源。

测量和分析抖动可借助三种仪器:误码率(BER)测试仪,抖动分析仪和示波器(数字示波器和取样示波器)。

选用哪种仪器取决于应用,即电或光、数据通信以及位率。

因为抖动是误码的主要原因,所以,首先需要测量的是BER。

若网络、网络元件、子系统或IC的BER超过可接受的限制,则必须找到误差源。

大多数工程技术人员希望用仪器组合来跟踪抖动问题,先用BER测试仪、然后用抖动分析仪或示波器来隔离误差源。

BER测试仪制造商需要测量其产品的BER,以保证产品符合电信标准。

当需要表征数据通信元件和系统时,BER测试对于测试高速串行数据通信设备也是主要的。

BER测试仪发送一个称之为伪随机位序列(PRBS)的预定义数据流到被测系统或器件。

然后,取样接收数据流中的每一位,并对照所希望的PRBS图形检查输入位。

因此,BER 测试仪可以进行严格的BER测量,有些是抖动分析仪或示波器不可能做到的。

尽管BER测试仪可进行精确的BER测量,但是,对于10-12BER(每1012位为1位误差)精度的网络或器件测试需数小时。

为了把测试时间从数小时缩短为几分钟,BER测试仪采用“BERT scan”技术,此技术用统计技术来预测BER。

可以编程BER测试仪在位时间(称之为“单位间隔”或“UI”)的任何点取样输入位。

“澡盆”曲线表示BER是取样位置的函数。

若BER测试仪检测位周期(0.5UI)中心的位,则抖动引起位误差的概率是小的。

若BER测试仪检测位于靠近眼相交点上的位,则将增大获得抖动引起位误差的似然性。

抖动分析仪BER测试仪不能提供有关抖动持性或抖动源的足够信息。

抖动分析仪(往往称之为定时时间分析仪或信号完整性分析仪)可以测量任何时钟信号的抖动,并提供故障诊断抖动的信息。

高速公路通信设施检测中常见问题与解决途径

Journal of Antennas 天线学报, 2021, 10(1), 1-4Published Online March 2021 in Hans. /journal/jahttps:///10.12677/ja.2021.101001高速公路通信设施检测中常见问题与解决途径裴元贞,王翠雪山东省交通科学研究院,山东济南收稿日期:2021年4月4日;录用日期:2021年5月5日;发布日期:2021年5月13日摘要目前,高速公路通信设施干线中心级、通信站级、光缆传输链路三级检测过程中会遇到诸多问题。

对检测过程中常见的问题进行调查、分析、比较,找出问题原因,提出解决问题的方法和途径,以促进高速公路通信设施质量的提高。

关键词高速公路,通信设施,检测,问题,解决途径Common Problems and Solutions inExpressway Communication FacilitiesDetectionYuanzhen Pei, Cuixue WangShandong Transportation Institute, Jinan ShandongReceived: Apr. 4th, 2021; accepted: May 5th, 2021; published: May 13th, 2021AbstractAt present, there are many problems in the process of three-level detection of highway communi-cation facilities, including trunk center level, communication station level and optical cable trans-mission link. This paper investigates, analyzes and compares the common problems in the detec-tion process, finds out the causes of the problems, and puts forward the methods and ways to solve the problems, so as to improve the quality of highway communication facilities.裴元贞,王翠雪KeywordsExpressway, Communication Facilities, Detection, Problems, SolutionsCopyright © 2021 by author(s) and Hans Publishers Inc.This work is licensed under the Creative Commons Attribution International License (CC BY 4.0)./licenses/by/4.0/1. 引言高速公路中,通信设施是机电工程中的重要组成部分,是高速公路机电工程中的大动脉,发挥着数据采集、数据分析、数据安全维护以及数据传输等重要作用。

抖动分析原理及安捷伦公司抖动分析解决方案

P3

0.980ns -0.030ns -0.020ns

(0.990/1.010/0.980/1.020)

P4

1.020ns 周期 0.040ns 周期到周期 0.000ns时间间隔误差

周期抖动 = 18.3ps RMS

周期到周期抖动 = 36.1ps RMS 时间间隔误差 = 9.6ps RMS

(0.020/-0.030/0.040)

2 1

4

Rise Fall

3

L_pkg C_comp R_pkg C_pkg

5

电路的不稳定性

PLL问题 同步开关噪声 互连阻抗不连续,互连损耗

上游的参考时钟

收发器发送的数据是以参考时钟为基准的,如果参考时钟

抖动过大。。。 使得抖动预估更困难 成为系统抖动

小结:抖动的成因

• 标准偏差 .

(所有测得的定时错误的RMS值).

• 峰 -峰值 .

(测得的定时错误的最大与最小值之差).

TIE的测量需要参考时钟.

常见的抖动术语小结

0.0ns 0.990ns 2.000ns 2.980ns 4.000ns

P1

0.990ns -0.010ns

P2

1.010ns 0.020ns 0.000ns

率噪声的方式显现出来。

目录

抖动的概念

抖动的成因 常见的抖动术语 抖动的分解 抖动测试分析方案

抖动的成因

热噪声

注入噪声

线路不稳定性 上游时钟

热噪声

随机性的 , 是多个随机抖动源的组合性现象 噪声所导致的抖动的分布是高斯与无边际的

注入噪声

确定性的, 能被确认为一些固有的成因 确定性抖动分布是有边际的,其频谱通常呈现为分离的谐波

连接器研讨会详解高速I/O解决方案和测试挑战

图1可插拔i n / 内含 网络 变压器 网口产品的发展路线图 of

Plg a l a d I u g be I n O CM r d c s Ro d P o u t a ma p

S 锄 l 吲l 熬壁 鼢 l ● R I . 韶 o v1_ m ● C n O .¨} d ..om・ o Cl  ̄

代连接技术因此应运而生。

泰科 电子 高速l 解 决方案 , O

泰科 电子 一直 积极地 参入 到连 接器 行业标 准 中 ,并 始 终 在 新 产 品的 开 发 中保 持 领 导地 位 。 公 司 高 速 IO解 决 方 案 主 要 包 括 :可 插 拔 ]O产 / /

品 、 内含 网络 变 压 器 网 口产 品 、高 速 数 据 电 缆组

铜制带 材 、片材 、管材 、条 材 、线材及 各种 型

材。维 兰德金 属 ( 上海 )有限公司技术营销经理

陈 明华 先 生 详 细 介 绍 了 维 兰 德 高 性 能 磷 青 铜 的 主 要 特 点 和 应 用 案 例 ,其 高性 能 铜 合 金 有 K5 , 5

2 岛巫圃 6

圃 基础电 I001 子 2 1.1

・

D fe e ta t l s i r niI i u S mu

幸 生 先 生 在 演 讲 中 介 绍 了 安 捷 伦 的 物 理 层 测

通 过 模式 转换 ( d .o v in )柬 衡 mo ec n es s ro

筇模 (Diee t 1 专 共模 ( mmo ) f rni ) f a Co l t 共模 ( mmo Co n) - 蓐模 (Diee t 1 - ) f ni ) fr a

艺 , 集 成 是 电 子 产 业 的 大 势 所 趋 。 由于 芯 片 的

基于ATE的高速DAC射频参数SFDR测试技术优化

基于ATE的高速DAC射频参数SFDR测试技术优化

沈锺杰;张一圣;孔锐;王建超

【期刊名称】《现代电子技术》

【年(卷),期】2024(47)2

【摘要】利用集成电路自动测试设备(ATE)测试高速DAC射频参数时,由于ATE测试板PCB走线较长、损耗较大以及机台提供的信号抖动比实装大等原因,导致ATE 上高速DAC射频参数测试指标低于实装测试值。

为此,文中介绍DAC电路的工作原理和测试方法;其次为解决上述问题,对测试码的生成以及PCB的布局等进行一系列改进,并将改进前后的测试值与典型值进行对比。

结果表明,改进措施成效显著,大大优化了高速DAC射频参数的测试指标,使得SFDR等高频DAC动态类参数指标接近或达到实装测试值。

【总页数】5页(P16-20)

【作者】沈锺杰;张一圣;孔锐;王建超

【作者单位】中国电子科技集团公司第五十八研究所

【正文语种】中文

【中图分类】TN407‐34

【相关文献】

1.基于虚拟仪器技术的DAC静态参数测试系统

2.基于ATE的卫星导航射频芯片测试技术

3.基于ATE的SoC射频测试技术的研究与应用

4.基于ATE的SiP测试技术优化和应用

因版权原因,仅展示原文概要,查看原文内容请购买。

高速SerDes抖动成因及其测试方法分析

7 07 ) 10 7 ( 西安航 空计算技 术研 究所 ,西安

摘 要 :高速 Sr s(E Ale/ Srle) 备 在 高速 芯 片 IO 接 口互联 上 已经 占有统 治性地 位 。然 而随 着 串行 e De SR azr i DE e azr 设 ii / 链 路 速率 不 断提 高 , 随之 而 来的抖 动等 因素 对 高速 Sr s 品 率构成 极大威 胁 。本 文首先 对 Sr s e De成 e De 的结构 进行介 绍 , 然后 对高速 Sr e 中信号抖动进行定性分析 , eD s 最后提 出了几种重要的 Sr s e De 测试方法 , 对高速 Sre 的测试具有一定参考价值。 e s d

电子论文-高速互联链路中参考时钟的抖动分析与测量

高速互联链路中参考时钟的抖动分析与测量中兴&力科 高速信号测试技术联合实验室 陈明华 张昌骏摘要在高速互联链路中,发送器的参考工作时钟的抖动是影响整个系统性能的关键因素之一。

本文对时钟抖动的主要概念、测试方法及注意事项、测试难点进行分析和探讨。

高速互联链路介绍任何一个通信链路都包含三个部分:发送器(TX)、媒质(信道)、接收器(RX)。

对于高速的串行互联链路也包含这三个部分,如下图1所示为一个典型的高速互联链路的结构图。

其中发送器包括了:并行转换串行、编码(比如8b10b编码)、发送信号优化(如预加重)、发送驱动等功能。

接收器包括了:时钟恢复、数据恢复、接收信号优化(如均衡)、串行转化并行、解码等功能。

传输通道则由印刷电路板的走线、过孔、连接器、插卡的金手指、电缆、光纤等组成。

从整个链路的组成来看,发送器参考时钟的抖动在串并转换时就引入到整个链路中,影响着TX端发送出的数据的抖动,而接收器要从这些数据中恢复出时钟来进行后续的处理。

可以看出发送器参考时钟的性能对整个链路的性能起到很关键的作用。

本文从时钟抖动的相关概念、测试实例、测试注意事项、测试难点几方面对时钟抖动测试进行分析和探讨。

图1:串行互联链路的结构示意图三种时钟抖动的定义,峰峰值与有效值时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。

TIE又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。

理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟。

如图2所示TIE 抖动的示意图,I1、I2、I3、In-1、In 是时钟第一个到第n 个上升沿与理想时间位置的偏差,将I1、I2到In 进行数理统计,在所有样本的找出最大值和最小值,两者相减可以得到TIE 抖动的峰峰值,即:假设N为测量的样本总数,抖动的平均值可表示为:抖动的有效值(即RMS 值)为所有样本的1个Sigma 值,即:周期抖动(Period Jitter )是多个周期内对时钟周期的变化进行统计与测量的结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速信号抖动测试解决方案

概述

在高速传输的数字系统或是通讯系统当中,将信号完整无缺地从传送到

目的地为其首要目标。

信号在传输的过程当中因为传输线的损失、系统的噪声,以及不可避免的人为因素,常使得信号失真,而传输抖动之现象,乃是今日研

究之重要课题。

在大都会之骨干网络当中,为了提升传输系统误码率之质量,

通常会以低噪声的前置放大器作为降低噪声以及抖动的方法之一。

通常随着抖

动量之增加,系统误码率便会提升。

所以如何从正确地分析抖动之特性以及对

传输系统所造成之影响为本文所讨论之重点。

安捷伦提供了一系列之抖动测试

解决方案,使得用户能在准确而快速的状况下取得适合的数据,亦能提供详细

之报表以作分析之用。

本文将以眼

定义

任何数字传输系统必定存在两种构成要素,一是本质数字信号( Deterministic Digital Signal),另一则是时钟信号( Clock Signal)。

时钟信号又分为标准时钟信号(Standard Clock)及依附时钟信号(Embedded C lock)。

所谓的抖动现象,乃是指本质数字信号与时钟信号所产生的一种相位差,亦可看做是一

种相位调变信号。

而在这时候,时钟信号所扮演的是一种标准之参考信号。

这

种时间差的相位变化,经过了一段时间可能形成一种周期性的正弦调变现象,

而将其称之为时域抖动现象,如

抖动的形成通常我们会使用取样示波器(Sampling Scope)来撷取其眼

所以通常通讯规范组织会定义出一种屏蔽(Mask)来判定此通讯系统是否。