理想MOS结构的表面空间电荷区全解

10分钟详细图解MOS管的结构原理

10分钟详细图解MOS管的结构原理什么是MOS管MOS管是⾦属 (metal) — 氧化物 (oxide) — 半导体 (semiconductor) 场效应晶体管,或者称是⾦属 — 绝缘体 (insulator)— 半导体。

MOS管的source和drain是可以对调的,他们都是在P型backgate中形成的N型区。

在多数情况下,这个两个区是⼀样的,即使两端对调也不会影响器件的性能,这样的器件被认为是对称的。

双极型晶体管把输⼊端电流的微⼩变化放⼤后,在输出端输出⼀个⼤的电流变化。

双极型晶体管的增益就定义为输出输⼊电流之⽐ (beta) 。

另⼀种晶体管叫做场效应管 (FET) ,把输⼊电压的变化转化为输出电流的变化。

FET的增益等于它的transconductance,定义为输出电流的变化和输⼊电压变化之⽐。

市⾯上常有的⼀般为N沟道和P沟道,⽽P沟道常见的为低压MOS管。

场效应管通过投影⼀个电场在⼀个绝缘层上来影响流过晶体管的电流。

事实上没有电流流过这个绝缘体,所以FET管的GATE电流⾮常⼩。

最普通的FET⽤⼀薄层⼆氧化硅来作为GATE极下的绝缘体。

这种晶体管称为⾦属氧化物半导体(MOS) 晶体管,或⾦属氧化物半导体场效应管 (MOSFET) 。

因为MOS管更⼩更省电,所以他们已经在很多应⽤场合取代了双极型晶体管。

MOS管的优势•可应⽤于放⼤,由于场效应管放⼤器的输⼊阻抗很⾼,因此耦合电容可以容量较⼩,不必使⽤电解电容器•很⾼的输⼊阻抗⾮常适合作阻抗变换,常⽤于多级放⼤器的输⼊级作阻抗变换•可以⽤作可变电阻•可以⽅便地⽤作恒流源•可以⽤作电⼦开关•在电路设计上的灵活性⼤,栅偏压可正可负可零,三极管只能在正向偏置下⼯作,电⼦管只能在负偏压下⼯作;另外输⼊阻抗⾼,可以减轻信号源负载,易于跟前级匹配MOS管结构原理图解结构和符号 (以N沟道增强型为例)—— 在⼀块浓度较低的P型硅上扩散两个浓度较⾼的N型区作为漏极和源极,半导体表⾯覆盖⼆氧化硅绝缘层并引出⼀个电极作为栅极。

MOS的物理机制讲解

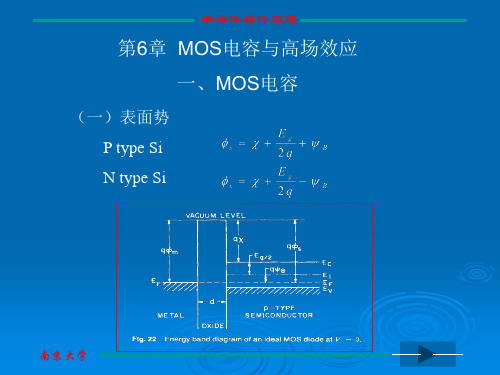

MOS的表面能带弯曲•说明:qψS ( 表面势能) = ( 半导体内的E i ) – ( 表面处的E i );V GS 可使表面势ψs 变化( 基本是线性变化关系) ;Q n(y) 是沟道中的少数载流子面电荷密度.•半导体的Fermi势ψB和表面状态:在半导体表面处的载流子浓度决定于表面能带的弯曲程度:n P0 = n i exp[(E F-E i)/kT] >> n i ;p P0 = n i exp[(E i-E F)/kT] << n i .在半导体内的Fermi势能(qψB = E i-E F ) 可用半导体内的参量来表示:∵半导体内的平衡多子浓度p P0 = n i exp[(E i-E F)/kT] = n i exp(qψB/kT) ≈ N A ,∴ψB =( E i-E F )/q = (kT/q) ln(N A / n i ).可见: 在ψs = ψB时, 表面处的多子浓度将小于体内的多子浓度, 而少子浓度将多于体内的少子浓度,即表面呈现为弱反型的表面;在ψs = 2ψB时, 表面处的多子浓度将远小于体内的多子浓度,而少子浓度将远多于体内的少子浓度,为强反型表面.理想MOSFET的阈值电压:•说明:①MOSFET是“理想”的含义:在MOS系统中不含有任何电荷状态(除栅电压在半导体表面产生的空间电荷以外, 不考虑表面态电荷和M-S功函数差).→在栅电压V GS = 0 时, 半导体表面的能带不发生弯曲(平带状态) .②在讨论V T时忽略了反型层中的电荷:因为刚达到强反型时, 正好沟道中的电子浓度= p-衬底内的空穴浓度; 而且反型层仅限于表面极薄的一层,其中的电荷Q n, 比耗尽层中的电荷Q B少得多(在刚强反型时, 耗尽层宽度最大). 所以可忽略反型层中的电荷Q n .MOS的非饱和特性•说明:沟道的长度(y方向)为L ;沟道的宽度(z方向)为Z ;沟道的厚度(x方向)为X(y) ;沟道的截面积为A ;沟道的电子浓度为n .•理想MOSFET的输出伏安特性计算~沟道电流I D是沟道中的面电荷密度Q n(y)漂移运动的结果:I D= Z X q n μn E(y) = Q n(y) Z μn E(y) ,代入Q n(y)与电压的关系, 并把E(y)用电压来表示为dV(y)/dy, 即有I D= Z μn C i [V GS - V T - V(y)] dV(y)/dy ,积分之∫I D dy = Z μn C i ∫[V GS - V T - V(y)] dV(y) ,[ 积分限: y= 0~L , V= 0~V DS ]则得到I D= ( Z μn C i / L ) {(V GS - 2ψB - V D/2) V DS-(2γ/ 3)×[ (V DS+ 2ψB)3/2 - (2ψB)3/2 ] },I D≈( m Z μn C i / L ) { (V GS - V T ) V DS - V DS2 }= m β{ (V GS - V T ) V DS - V DS2 } (Sah方程) ,其中γ≡( 2εε0 q N A )1/2 /C i称为衬偏系数; 对较小的N A , m = 1/2 .β = Z μn C i / L .①当V DS 较小时, 有线性特性:I D= ( Z μn C i / L ) {V GS - 2ψB - [2εε0 q N A(2ψB)]1/2 / C i } V DS= β (V GS - V T ) V DS∝V DS ,当V GS= 2ψB - [2εε0 q N A (2ψB)]1/2 / C i ≡V T 时, I D = 0, 即沟道夹断, 这时的栅电压就是阈值电压(夹断电压) .线性区的跨导为g m= ( Z μn C i / L ) V DS .系数( Z μn C i / L ) 称为器件的增益因子(或导电因子).②饱和区:由dI D / dV DS= 0 = β[(V GS - V T ) – V DS ] ,得到饱和电压V DSat = V GS - V T.把V DSat代入到I D表示式中, 求得饱和电流为I DSat= (β/2) (V GS - V T ) 2 ∝V GS2 .可见, 饱和电流与V DS无关, 而与V GS有抛物线关系; 而且饱和电压V DSat随着V GS 的增大而升高.•长沟道MOSFET的电流饱和机理:随着V DS的增加, 夹断点逐渐从漏端移向源端(夹断区扩大); 所增加的电压(V DS - V D sat ) 就降落在夹断区上(使电场↑), 而未夹断的沟道上的电压基本上维持在V D sat ; 当电子从源端漂移到夹断点时, 就被夹断区中的强电场拉到漏极, 则漏极电流基本上由未夹断的沟道区(有效沟道长度)决定, 而有效沟道上的电压基本不变, 故电流饱和(实际上, 由于有效沟道长度随V DS而变, 类似BJT中的Early效应, 所以电流并不完全饱和, g D≠0).饱和电流与V GS有抛物线关系; 饱和电压与V GS之间有线性关系.实际mos的VT•对于实际的MOSFET,需要考虑金属与半导体功函数之差、Si-SiO2系统中电荷的影响。

半导体物理基础 第六章 MOS

QS QB qNa xd

2 qNa xd S 2k s 0

(6-5)

和

(6-6)

6.2 理想MOS电容器

代入(6-44)式解出 x

d

Xd

kS 0 kS 0 2VG 1 C0 2 C0 C0 qkS 0 N a

2 0 12

(6-45)

C 2C 1 qN k VG C0 a S 0

6.2 理想MOS电容器

积累区( VG <0)

MOS系统的电容C基本上等于绝缘体电容 C0。当负偏压的数值逐渐减少时,空间电 荷区积累的空穴数随之减少,并且 QS 随 C也就变小。 平带情况( VG =0)

S

的变化也逐渐减慢, C S 变小。总电容

C FB C0

1 k 0 LD 1 k s x0

(6-1)

掌握载流子积累、耗尽和反型和强反型的概念。 正确画出流子积累、耗尽和反型和强反型四种情况的能带图。 导出反型和强反型条件

6.2 理想MOS电容器

6.2 理想MOS电容器

系统单位面积的微分电容

微分电容C与外加偏压 VG 的关系称为MOS系统的电容—电压特性。

dQM C dVG

(6-1)

S =半导体表面的电场

k0 =氧化物的相对介电常数

k S =半导体相对介电常数

xd =空间电荷区在半导体内部的边界亦即空间电荷区宽度。

外加电压 VG 为跨越氧化层的电压

V0和表面势 S 所分摊:

(6-2)

VG V0 S

6.1 理想MOS结构的表面空S结构内的电位分布

(6-22)

dV0 d s 1 dVG C dQM dQM dQM

第五章 MIS结

理想 M I S 结构在正偏和负偏时,半导体表面可有三种情形: 积累 P型 耗尽 反型

能带向下弯曲增加 能带向下弯曲 能带向上弯曲, 多数载流子耗尽 本征能级与费米能级 价带顶接近费米能级 在表面相交, 多数载流子在表面处积累 表面处的少数载流子 多于多数载流子 理想MIS二极管在V≠ 0时的三种能带图。 (6)

2ε i C = [1 + V ]−1 / 2 Ci qN Aε S d 2

2

(20)

QS = −(2qN Aε sψ s )1/ 2

dQS ε s CD = − = dψ s W

5)V> ψB , 反型区

(1) (2) (3) (4) (5)

ψS= ψB:弱反型开 始。 ψS=2 ψB:强反型开 始。 由于电容增加依赖 于电子(少子)密度 对外加交流信号的 跟随能力,不同的 频率下,将有不同 的表现: • 低频下, 总电容减少到 一个极小值再增加 • 高频下电容不增加。

(1)

(2) (3) (4) (5)

4)V>0,耗尽开始, 耗尽区的表面势范 围:ψS=0 ~ψB 随着外加偏压的增 加,耗尽区宽度增 加,半导体电容减 小。总电容减小。 半导体表面耗尽 时,耗尽区的电离 受主为:QS =-qNAW

qN AW 2 M I S系统的电容 - 电压曲线 表面势:ψ s = 2ε s

空间电荷 半导体体内,电子和空穴密度与ψ的关系:

n p = n po exp(qψ / kT ) = n po exp(βψ ) p p = p po exp(− qψ / kT ) = p po exp(− βψ )

P型半导体体内电 子,空穴平衡密度 半导体表面,电子和空穴密度与ψs的关系:

β = q / kT

半导体器件物理哈理工复习资料缩印

半导体器件物理哈理⼯复习资料缩印1.PN 结:采⽤不同的掺杂⼯艺,通过扩散作⽤,将P 型半导体和N 型半导体制作在同⼀块半导体基⽚上,在它们的交界⾯就形成空间电荷区称为PN 结。

2.雪崩击穿:随着PN 结反向电压的增加,势垒中电场强度也在增加。

当电场强度达到⼀定程度后,势垒区中载流⼦就会碰撞电离出新的电⼦—空⽳对。

新的电⼦—空⽳对在电场作⽤下继续碰撞产⽣新的载流⼦,如此反复即碰撞电离率增加,流过PN 结的电流急剧增⼤,击穿PN 结。

3.空间电荷区:在PN 结中,由于⾃由电⼦的扩散运动和漂移运动,使PN 结中间产⽣⼀个很薄的电荷区,就是空间电荷区。

4.耗尽层电容:由于耗尽层内空间电荷随偏压变化所引起的电容称为PN 结耗尽层电容。

5.MOS 阈值电压:阈值电压si -ψ+=O B TH C Q V 是形成强反型层时所需要的最⼩栅极电压。

它的第⼀项表⽰在形成强反型层时,要⽤⼀部分电压去⽀撑空间电荷QB ;第⼆项表⽰要⽤⼀部分电压为半导体表⾯提供达到强反型时需要的表⾯势si ψ。

6.强反型:当表⾯电⼦浓度等于体内平衡多⼦浓度时,半导体表⾯形成强反型层。

7.载流⼦扩散漂移观点分析空间电荷区形成当N 型P 型材料放在⼀起时,P 型材料中多的空⽳向N 型扩散,N 型多的电⼦向P 型扩散,由于扩散,在互相靠近N 侧和P 侧分别出现施主离⼦和受主离⼦,这些空间电荷建⽴⼀个电场,即空间电荷区。

8.载流⼦扩散漂移分析PN 结单向导电性若在PN 结加正向电压,PN 结势垒⾼度下降,减⼩的势垒⾼度有助于扩散通过PN 结,形成⼤的电流,若加反向电压,势垒⾼度增加,漂移作⽤增强,阻挡载流⼦通过PN 结扩散,所以PN 结单向导电1.5种半导体器件:PN 结,光电⼆极管,JFET,MOSFET ,太阳能电池。

2.PN 结隧道电流产⽣条件:费⽶能级进⼊能带;空间电荷层的宽度很窄,因⽽有⾼的隧道3.穿透概率;在相同的能⼒⽔平上,在⼀侧的能带中有电⼦⽽在另⼀侧的能带中有空的状态。

22 第六章 62 理想MOS电容器讲解

1. 积累区(VG<0)

Physics of Semiconductor Devices

当MOS电容器的金属电极上加有较大的负偏压时,能带明显向 上弯曲,在表面造成多数载流子空穴的大量积累;只要表面势

φS稍有变化,就会引起表面空间电荷QS的很大变化;所以,半

导体表面电容比较大,可以忽略不计。MOS系统的电容基本上 等于绝缘体电容C0。

Physics of Semiconductor Devices

两个电容串联后,总电容变小,且其数值主要由较小的一个电 容所决定,因为大部分电压都降落在较小的电容上。

MOS电容的等效电路

C/C0称为系统的归一化电容

VG

C0 CS

对于理想MOS系统:

Physics of Semiconductor Devices

MOS电容积累区的C-V特性

2. 平带情况(VG=0)

Physics of Semiconductor Devices

VG=0时,φS=0,能带是平直的,称为平带情 况 在平带附近,空间电荷区中:

由空穴的过剩或欠缺引起的电荷密度:

在平带附近,׀φ<<׀VT。上式进行指数项展开,且只保留前两项:

空间电荷与表面 势符号相反

平带情况下半导体表面的小信号电容(微分电容):

在杂质饱和电离的情况下: 归一化平带电容:

Physics of Semiconductor Devices

正比掺杂浓度 正比厚度

理想MOS的归一化平带电容随杂质浓度和氧化层厚度的关系

3. 耗尽区(VG>0)

耗尽区:

Physics of Semiconductor Devices

Physics of Semiconductor Devices

device-3

VFB

Q0 = ms COX

7

多晶硅-SiO2-Si

ms = φ f (多晶硅 ) φ f (硅衬底)

ms = 0.56 φ f (V) p-type Si n+多晶硅 ms = 0.56 + φ f (V) n-type Si

8

P型硅:平带电压为负,C-V向负方向移动

9

2. 二氧化硅及其与硅界面的相关电荷的影响 热生长二氧化硅中的电荷

1 1 1 1 = + + C Cox C s + Co C poly

反型时,SiO2-Si界面电子 可能耗尽POLY中电子,出 现Cpoly,总电容变小

有效的tox增大

Vt增大,Ids降低

电容降低,速度仍受影响

16

4、尺寸量子化效应 MOSFET 在 表 面 反 型 沟道中载流子被限制 在一很窄的势阱之中 载流子在垂直于表 面方向量子化

MOSFET并不是在Vg=Vt处就突然关断,当Vg<Vt时, 存在泄漏电流,影响器件的静态功耗 亚阈区MOSFET的电流以扩散电流为主,不是多子电流, 未出现反型层

52

类似BJT

s ∝ VG

KT

s =

界面陷阱的充放电有频率响应,在高频下,跟不上信号的 变化,Cit=0

用低频和高频C-V的差别可以测Cit

c. 引起阈值电压不稳定、迁移率降

低、跨导降低

14

3. 多晶硅耗尽效应(PDE) 当tox很薄,POLY非简并,出现PDE

15

Vg = VFB + φ s + V poly + VOX

C poly = dQ poly dV poly

-16

-16

第6章(MOS电容)

半导体器件原理

(2)界面陷阱电容(并联于硅电容)

(3)表面产生复合中心(减小少子寿命)

在耗尽时起作用,而在反型或积累时不起作用。

(4)表面态或陷阱帮助的带到带隧穿

南京大学

半导体器件原理

二、高场效应

1. 碰撞离化和雪崩击穿 αp 单位距离内空穴导致电子空穴对产生 αn单位距离内电子导致电子空穴对产生

南京大学

半导体器件原理

(4)氧化层中的可动电荷 来源:沾污氧化层外表面的正离子,在电场或温度的 作用下,漂移到近界面处。 影响:在硅表面处感应负电荷,影响器件的稳定性。

成份:Na+,K+,Li+,H+。 热氧化后去除表层氧化层, 采用P处理, 无钠清洁工艺 用氮化硅作表面钝化。

南京大学

半导体器件原理

南京大学

半导体器件原理

1)对耗尽层情况: 由氧化层厚度,半导体掺杂浓度,可得ψs 随VG的变化关系。

南京大学

半导体器件原理

2)对强反型情况: 空间电荷密度还包括载流子,耗尽层宽度达极 大值。 外加电压只引起反型层中电子浓度的增加以及 金属电极上正电荷的增加。

南京大学

半导体器件原理

南京大学

半导体器件原理

南京大学

半导 实际常用实验测定。

南京大学

半导体器件原理

经验碰撞离化率 (1)αn>> αP, 特别在低电场时 (2)离化系数随电场迅速增长,PN结中,减小最大 电场以减小离化系数 掺杂缓变或使用轻掺杂区做i层, 可有效降低PN 结中的峰值电场.

南京大学

半导体器件原理

λ:Si中热电子能量损失的平均自由程 qV(d):发射的有效能量势垒 ER:光学声子能量 λ0:10.8 nm, λ的低温极限。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.结构与工作原理 2.半导体表面空间电荷区

3.载流子的积累、耗尽和反型

4.反型和强反型的条件

前言:

半导体器件的特性与半导体表面特征性质有特 别重要的联系。在超、特大集成电路迅速发展的 今天,半导体器件的制造相当多是在很薄的一层 表面内完成的(几个微米甚至更小),因而,如 何有效控制和完善半导体的表面质量,从而进一 步利用半导体表面效应,可用来制造例如MOS(金 属 -氧化物-半导体)器件、 CCD (电荷耦合器件)、 LED (发光二极管)、 LCD (液晶显示)、半导体 激光等表面发光器件,以及太阳能电池等表面感 应器件。

因此:

即使有外加电压,表面空间电荷区也处于热平衡状态,使得 整个表面空间电荷区中费米能级为常数。

ℰ0为SiO2层的内建电场,QM为金属极板上的电荷,则半导体

表面感应电荷为QS=-QM。在外电场的作用下,在半导体表面 形成具有相当厚度(μm)的空间电荷区,它对电场起到屏

蔽作用。空间电荷区的形成是由于自由载流子的过剩或欠缺

S / VT

f / VT

OR

n( x ) ni e[ ( x ) f ] / VT nS ni e[S f ] / VT

n0 ni e

( E F Ei0 ) / KT ( Ei0 E F ) / KT

n ni e ( EF Ei ) / KT p pi e ( Ei EF ) / KT

穴的耗尽,少数载流子电子有所增加。当由于平衡少子数目极

小,因此,少子数目仍然可以忽略。 空间电荷由没有空穴中和的、固定的受主离子构成。

Ei ( x) Ei0 q ( x)

在半导体表面处有:

n ni e ( EF Ei ) / KT p pi e ( Ei EF ) / KT

Ei s Ei0 qs

令:

( Ei0 EF ) 为半导体内的费米势 f q

可以得到:

n0 ni e

( E F Ei0 ) / KT ( Ei0 E F ) / KT

p 0 pi e

半导体表面层的载流子分布:

Ei ( x) Ei0 q ( x)

( Ei0 EF ) f q

p ( x) p0 e ( x ) / VT ps p0 e S / VT p0 pi e

f / VT

OR

p ( x ) ni e[f ( x )] / VT pS ni e

理想表面(清洁表面)

原子完全有规则排列所终止的一个平面。 表面排列整齐的硅原子与体内的硅原子形成共价键,

但由于表面价键处于所谓“悬挂键”的空置状态,其状

态极其不稳定,表面很容易吸附一些其他原子例如空气 中的氧原子而形成氧化层。

真实表面

用物理或化学方法形成的半导体表面,暴露在 空气中,存在氧化层或吸附其他原子。 表面存在“悬挂键”,对电子有受主的性质,存在 一些可以容纳电子的能量状态,称为“表面能级”或“ 表面态”。 表面能级在禁带中靠近价带顶的位置,准连续。

以及杂质能级上电子浓度的变化引起的。

电场 ℰ 从半导体表面到内部逐渐减弱,直到空间电荷区内边 界上基本全部被屏蔽而为零。则每个极板上的感应电荷与电场 之间满足如下关系:

QM QS 0 s sE

εsE:半导体表面电场

在空间电荷区中电场的出现使半导体表面与体内之间产生电位 差,半导体表面的电势,称为表面势 S 。在加上电压VG时,外 加电压VG为跨越氧化层源自电压V0和表面势 S 所分摊,即有:

n ni e ( EF Ei ) / KT p pi e ( Ei EF ) / KT

p 0 pi e

Ei ( x) Ei0 q ( x)

半导体表面层的载流子分布:

( Ei0 EF ) f q

n( x) n0 e ( x ) / VT nS n0 e n0 ni e

(f S ) / VT

1. 载流子的积累

当紧靠硅表面的多数载流子浓度大于体内热平衡多数载流子浓

度时,称为载流子积累。

当金属电极上加负电压时,在半导体表面形成负表面电势 S , 表面空间电荷区中能带向上弯曲,由于费米能级EF保持常数, 能带向上弯曲使接近表面处有更大的Ei-EF,与体内相比,在表 面处有更高的空穴浓度和更低的电子浓度,使空穴在表面积累,

增加表面的电导率。

表面电荷为: QS q 0 [ p( x) p0 ]dx

xd

QS q [ p( x) p0 ]dx

0

xd

载流子积累

2. 载流子耗尽

当金属电极上施加正偏压VG时,表面势 S 为正,空间电荷区

中能带向下弯曲,准费米能级能级Ei靠近费米能级EF, (Ei –EF) 值减小,表面空穴浓度低于体内热平衡值,造成多数载流子空

VG V0 S

金属-氧比物和P型半导体的电位分布图

VG V0 S

三 载流子的积累、耗尽和反型

空间电荷区静电势 ( x) 的出现改变了空间电荷区中的能带

图。根据VG极性和大小,有可能实现三种不同的表面情况:

① 载流子积累;

② 载流子耗尽;

③ 半导体表面反型。

设半导体体内本征费米能级为Ei0,则空间电荷区内:

表面势

空间电荷区表面到内部另一端,电场从最大逐渐减弱到零,其 各点电势也要发生变化,这样表面相对体内就产生电势差,并伴随 能带弯曲,常称空间电荷区两端的电势差为表面势Ψ S。

一 结构

MOSFET结构示意图

源极、衬底和漏极构成两个背靠背的二极管。在不加栅压 时,只能有很小的反向饱和电流通过源漏极。当栅压足够 大时,栅极下面半导体会反型。

衬底N型半导体-P型反型层-P沟道MOSFET 衬底P型半导体-N型反型层-N沟道MOSFET

反型层出现后,再增加电极上的电压,主要是反型层中的电

子增加,由电离受主构成的耗尽层电荷基本上不再增加。

二 半导体表面空间电荷区

理想MOS结构假设:

① 在氧化物中或在氧化物和半导体之间的界面上不存在电荷 ② 金属和半导体之间的功函数差为零 ③ SiO2层是良好的绝缘体,能阻挡直流电流流过