基于FPGA的卫星导航信号viterbi译码方法

一种Viterbi译码器的FPGA实现

砍4

吞吐率要求。 译码器的硬件实现可以 采用串行或者并行方式。 串行方式可以 通过对硬件单元的复用降 低电 路设计门数, 适合于K值较大的 情况, 但降低了数据的吞吐量。 同样基于数据吞吐率的 要求, 在 译码器的实现中,采用了全并行方式。 电 2 C 单元、 路主要由3 个A S 全局路径比 较和回溯逻辑组成。一个A S C 单元由4 个加法器、

元。对于约束长度K 7 译码,总计需3 个蝶形单元。 =的 2 对于译码码元的输出, 根据编码方采取的 策略, 有两种不同的 方式: 1 编码端采用固定长度的数据块。 、 在每一个数据块的尾部增加 K个 0 迫使每块数据输出 , 后的编码器状态复原为全0 。在译码端, 选择最终状态为全 0 的路径作为最佳路径,沿该路径行 进记录的信息位为输出的 译码信息. 这种方法实现起来有一定的简化, 不需要最终的 6 4条路径 的比 较。 但是, 编码效率降低了。 2 编码端信息流是连续的。 、 在译码端经过一段码流后 ( 一般为L (-0 K , = - ) 可以认为 51 ) 后 续的 码流与L 位以前的 码流相关性很弱, 选择最小路径度量值的记录信息作为输出。 考虑到要求较高的编码效率,我们在设计中采用了第二种方式. 在译码器的 输出处理上, 有两种方式: 回溯法和寄存器交换法。 溯法在输入码流达到一定 回

度量的最大值和最小值; K时约束长度。当K 7 三位软判决时, =, 路径度量的范围为0 2 -4. 因此,设计中路径度量值用 6 位二进制表示。为了保证各状态的路径度量值不溢出,需要对 路径度量值做归一化处理。

全局路径比 较器需要从2, 态路径 值中 最小 K个状 - 度量 选出 结果。 设计中 采用了比 器阵 较

条。

3 Vt b译码器的结构 . e i ir

基于FPGA的卷积码Viterbi译码器实现方法

1 卷 积码和格型图

设 计某 ( 3 , 2 , 3 ) 卷 积码 V i t e r b i 译码器 , 图 1为 该 编码 器 的编码 方框 图 。

译码算法等 。由于卷积码具有 网格编码 的特点 ,

维特 比 ( V i t e r b i ) 提 出 了最 大 似 然 ( Ma x i m u m L i k e l i . h o o d ,ML ) 译 码 算 法 J , 它 易 于 对 约 束 长 度 小 的卷 积码 实 现软判 决 译码 。文 献 [ 4] 基 于 状 态 机设 计 了 V i t e r b i 译码 器 , 该 方 法 需 要将 状 态 转 移矩 阵 和输 出

@ 2 0 1 3 S c i . T e c h . E n g r g .

基于 F P G A的卷积码 V i t e r b i 译码器实现方法

李 明阳 ’ 柏 鹏 屈 鹏 , 张毓 桐。

( 空军工程大学装备管理与安全工程学院 , 综合 电子信息系统与电子对抗技术研究 中心 , 理学院。 , 西安 7 1 0 0 5 1 )

有

h +m 一1 h+ m 一1

M ( r I ) =∑ M ( r ) =∑l g P ( r )

f =0 2 =0

( 2 ) ∞一 一 O 吣 O m 1 ∞ l m O 叭 O ¨ 1 叭 l ¨ 可 以将 一条 路径 的前 t 个 分 支 的部 分路 径 量度

矩阵存储 在查找 表 中, 译码 过程 中需 要搜 索查 找 表, 增加了译码 时间。文献 [ 5 , 6 ] 分析 了资源 复用

和译 码 时 间 的关 系 并 设 计 了相 应 的译 码 器 。本 文

借鉴该文思路设计 了一个码率 为 2 / 3的卷积码 的

viterbi译码算法详解

viterbi译码算法详解Viterbi译码算法是一种常用的序列解码算法,广泛应用于语音识别、自然语言处理、通信等领域。

本文将详细介绍Viterbi译码算法的原理和步骤,以及它的应用。

Viterbi译码算法是一种动态规划算法,用于在给定观测序列的情况下,求解最可能的隐藏状态序列。

在这个过程中,算法会基于概率模型和观测数据,通过计算每个可能的状态路径的概率,选择概率最大的路径作为输出。

Viterbi译码算法的基本原理是利用动态规划的思想,将问题分解为一系列子问题,并利用子问题的最优解来求解整体问题的最优解。

在Viterbi译码算法中,我们假设隐藏状态的转移概率和观测数据的发射概率已知,然后通过计算每个时刻的最优路径来递推地求解整个序列的最优路径。

具体而言,Viterbi译码算法包括以下步骤:1. 初始化:对于初始时刻t=0,计算每个隐藏状态的初始概率,即P(x0=s)。

2. 递推计算:对于时刻t>0,计算每个隐藏状态的最大概率路径。

假设在时刻t-1,每个隐藏状态的最大概率路径已知,则在时刻t,可以通过以下公式计算:P(xt=s) = max(P(xt-1=i) * P(xi=s) * P(ot=s|xi=s))其中,P(xt=s)表示在时刻t,隐藏状态为s的最大概率路径;P(xt-1=i)表示在时刻t-1,隐藏状态为i的最大概率路径;P(xi=s)表示从隐藏状态i转移到隐藏状态s的转移概率;P(ot=s|xi=s)表示在隐藏状态s的情况下,观测到观测值为s的发射概率。

3. 回溯路径:在最后一个时刻T,选择概率最大的隐藏状态作为最终的输出,并通过回溯的方式找到整个序列的最优路径。

通过上述步骤,Viterbi译码算法可以求解出给定观测序列下的最可能的隐藏状态序列。

这个算法的时间复杂度为O(N^2T),其中N 是隐藏状态的个数,T是观测序列的长度。

Viterbi译码算法在实际应用中有着广泛的应用。

关于基于Xilinx FPGA 的高速Viterbi回溯译码器的性能分析和应用介绍

关于基于Xi1inXFPGA的高速Viterbi回溯译码器的性能分析和应用介绍新一代移动通信系统目前主要采用多载波传输技术,基带传输速率较3G有很大提高,一般要求业务速率能达到30Mb/s以上。

约束长度卷积码以及Viterbi 译码器由于其性能和实现的优点,在新一代通信系统中仍然占有一席之地。

这就要求进一步提高Viterbi译码器的译码速率,同时优化Viterbi设计以减少由速率提高和约束长度的增加带来的硬件实现复杂度。

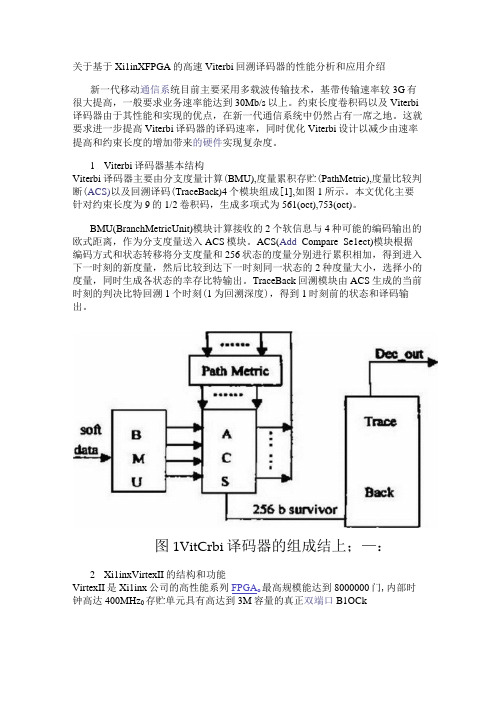

1Viterbi译码器基本结构Viterbi译码器主要由分支度量计算(BMU),度量累积存贮(PathMetric),度量比较判断(ACS)以及回溯译码(TraceBack)4个模块组成[1],如图1所示。

本文优化主要针对约束长度为9的1/2卷积码,生成多项式为561(oct),753(oct)。

BMU(BranchMetricUnit)模块计算接收的2个软信息与4种可能的编码输出的欧式距离,作为分支度量送入ACS模块。

ACS(Add_Compare_Se1ect)模块根据编码方式和状态转移将分支度量和256状态的度量分别进行累积相加,得到进入下一时刻的新度量,然后比较到达下一时刻同一状态的2种度量大小,选择小的度量,同时生成各状态的幸存比特输出。

TraceBack回溯模块由ACS生成的当前时刻的判决比特回溯1个时刻(1为回溯深度),得到1时刻前的状态和译码输出。

图1VitCrbi译码器的组成结上;—:2Xi1inxVirtexII的结构和功能VirtexII是Xi1inx公司的高性能系列FPGA o最高规模能达到8000000门,内部时钟高达400MHz0存贮单元具有高达到3M容量的真正双端口B1OCkRamo 运算单元中包括最多168b 的专用乘法器。

VirtexII 中的可配置单元为C1B(Configurab1e1og ic B1occks)。

C1B 中的资源可以灵活配置成多种结构。

viterbi译码算法详解

viterbi译码算法详解Viterbi译码算法详解Viterbi译码算法是一种在序列估计问题中广泛应用的动态规划算法。

它被用于恢复在一个已知的输出序列中最有可能的输入序列。

该算法最初由Andrew Viterbi在1967年提出,并被广泛应用于各种领域,如语音识别、自然语言处理、无线通信等。

Viterbi译码算法的基本思想是在一个已知的输出序列中寻找最有可能的输入序列。

它通过计算每个可能的输入序列的概率,并选择概率最大的输入序列作为最终的估计结果。

该算法的关键是定义一个状态转移模型和一个观测模型。

状态转移模型描述了输入序列的转移规律,即从一个输入状态转移到另一个输入状态的概率。

观测模型描述了输入序列和输出序列之间的关系,即给定一个输入状态,产生一个输出状态的概率。

在Viterbi译码算法中,首先需要进行初始化。

假设有n个可能的输入状态和m个可能的输出状态,我们需要初始化两个矩阵:状态概率矩阵和路径矩阵。

状态概率矩阵记录了每个时刻每个状态的最大概率,路径矩阵记录了每个时刻每个状态的最大概率对应的前一个状态。

接下来,我们通过递归的方式计算状态概率和路径矩阵。

对于每个时刻t和每个可能的输入状态i,我们计算当前状态的最大概率和对应的前一个状态。

具体的计算方式是通过上一个时刻的状态概率、状态转移概率和观测概率来计算当前时刻的状态概率,并选择其中最大的概率作为当前状态的最大概率。

我们通过回溯的方式找到最有可能的输入序列。

从最后一个时刻开始,选择具有最大概率的状态作为最终的估计结果,并通过路径矩阵一直回溯到第一个时刻,得到整个输入序列的最有可能的估计结果。

Viterbi译码算法的优势在于它能够处理大规模的状态空间和观测空间。

由于使用动态规划的思想,该算法的时间复杂度为O(nmT),其中n和m分别为可能的输入状态和输出状态的数量,T为输出序列的长度。

因此,在实际应用中,Viterbi译码算法能够高效地处理各种序列估计问题。

高性能维特比在卫星导航接收机中FPGA实现

高性能维特比在卫星导航接收机中PPGA实现IO:卫星定位接收机中卷枳码译码即维特比译码器,在处理器中面临占有资源较多、处理时间过长等间题,为了减少业理器资漏的占用和提高处理速度,采用并fiUDtt选噪形单元的的方法,在fPW 平台上用硬件描述语言设廿一种髙性能维特比译码器,作为gps 12 频点和galileoe1顺点接收机的通用译码器,在gps和galileo接收机上运用,大大械少资源使用,提髙接收机的处理速度。

关鍵词:viterbi译码器;gps /galileo接收机;卷枳码;fpga引言在现代通信系统中,要使信号能舉更可靠地在信道中传输,往往需要在信道编码中采用纠錯码来降低信号受噪声的影响,以降低传输的俣码率。

卷枳码及其viterbi译码是常用的信道编码方案[1 3L卷枳码在gnss接收机中得到应用,其中约束长度k=7,码率为1/2的卷枳码已经成为商业卫星通信系貌中的标准编码方法。

在卫星定位系统中,gpsl2频点fl] galileoe1的电文均采用卷枳码编码,目前在定位接收机中用软件进行viterbi译码较多,为了提髙处理速度通用性,本文设廿一种基于fpga的通用高速viterbi澤码器,能作为gps I2 fD galileo e1的电文的译码器,大大减少资源使用,提髙接收机的处理速度和城少软件复杂度,从而节约处理器的资源。

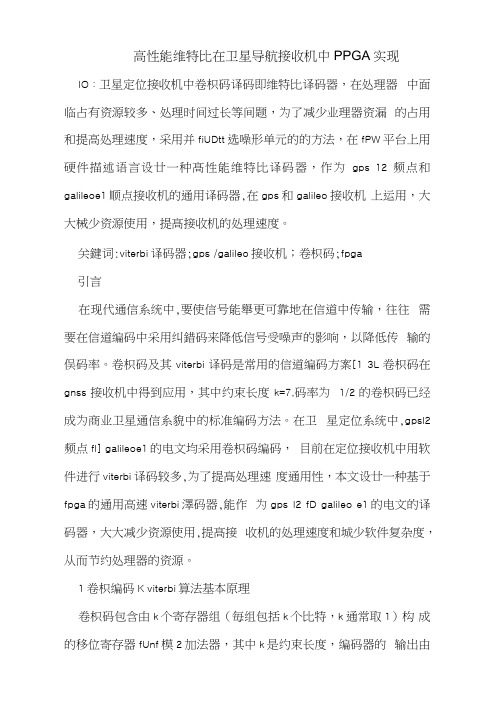

1卷枳编码K viterbi算法基本原理卷枳码包含由k个寄存器组(毎组包括k个比特,k通常取1)构成的移位寄存器fUnf模2加法器,其中k是约束长度,编码器的输出由当前输入数据和寄存器组中的数据共同决定。

对T gps 12和galileoe1 为(2, 1, 7)卷枳码,其生成多项式为g=(171, 133),电路图如图1所示。

(2, 1, 7)卷枳码编码器由6个延时器(图1中的卜1模块,可用寄存器实现)和两个模20II法器组成,它的编码约束度为7,码率为1/2, fid输人端输人1b信息,聯出端输出2 b 编码信息,并分为上、下两路并行輪出[4]。

通过Viterbi译码算法实现译码器优化实现方案

通过Viterbi译码算法实现译码器优化实现方案

1 引言

由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。

卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。

从工程应用角度看,对Viterbi译码器的性能*价指标主要有译码速度、处理时延和资源占用等。

本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。

测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。

2 卷积编码网格图特点

图1所示为卷积编码网格图结构,图中每一状态有两条输入支路和两条输出支路。

2.1 输入支路的特点

任意一个状态节点Si都有两条输入支路,且这两条输入支路对应的源节点分别为:

此外,i为偶数时,两条输入支路的输入信息都为‘1’;i为奇数时,两条输入支路的输入信息都为‘0’。

2.2 输出支路的特点

任意一个状态节点Si都有两条输出支路,且两条输出支路对应的目的节点分别为:

此外,目的节点是Sj1的输出支路对应的输入信息都为‘0’;目的节点是Sj2的输出支路对应的输入信息都为‘1’。

3 Viterbi译码器的优化算法

3.1 判决信息比特与路径信息向量同步存储算法。

基于FPGA的Viterbi译码器设计

/ 一 、

一 ,一

图2 ( , 1 )卷 积 码 状 态 图 2 ,3

结 合状 态 图可 得 出如 图3 示 的状 态 与 时 间 所

' 一/ 一 、

一\ ,一 一

关 系图 ,称为 网格 图。该 图设 输入 信 息数 目L 5 =, 所 以 画有 L N 8 时 间单 位 ( 点) + =个 节 ,图3 分别 中

并在Q atsI 进行 仿真 。首先 利用 编码 器对 已 ur 下 uI

知 的序列 进行 编码 ,产生 这个输 入序 列 的编码 码 字 ,并 对产 生 的编码码 字 进行人 为加 扰 ,用 以验 证 所 设 计 的V tri 码 器 对 错 误 信 息 的 纠错 能 i b译 e 力 。图5 示是该 译码 器 的仿真 图 ,对于 图5 所 ,通

t a 司的E 3 1 0 7 0 8 片的 (,1 )V tri e公 r P C 2F 8C 芯 2 ,7 i b译码 器 , 同时给 出 了时序 仿真 图。 e

关 键 词 :卷 积 码 ;V tri 码 ;F G i b译 e P A

0 引 言

在 现代 通信 系 统 中 ,要 使信 号 能够 更 可靠 地

法 。它 并不是 在 网格 图上一次 比较所 有可 能 的2

看 出 ,输入 的序 列 与译 码 输 出的序列 一致 ,故 可 证 明V t v 码器设 计 的正确性 。 i ri e 译

条 路径 ( 列) 序 ,而 是 接 收一 段 ,就 计算 、 比较 、

选 择一段 最可 能 的码 段 f 支) 分 ,从而使 整个 码序 列达到一个 有最 大似然 函数 的序列 。

第20 第5 1卷 年 月 2 期 0 5 1

从FPGA实现的角度对大约束度Viterbi译码器

从FPGA实现的角度对大约束度Viterbi译码器1 引言Viterbi译码算法是一种最大似然译码算法,目前广泛应用于各种数据传输系统,特别是卫星通信和移动通信系统中。

近年来随着FPGA技术的迅速发展,使得基于FPGA实现Viterbi译码的算法成为研究的热点。

由于Viterbi译码器的复杂性随约束长度k成指数增加,大约束度不但使Viterbi译码器硬件复杂度大为增加,同时也限制了译码速度。

而其中以加比选(Add Compareselect,ACS)运算为最主要的瓶颈,的递归运算使流水线结构的应用变得困难。

本文以(2,1,9)卷积码为例,用FPGA实现大约束度Viterbi译码器,其中ACS设计采用串并结合的方法来兼顾面积和速度,并用流水线结构来提高译码速度,对路径度量存储则采用同址存储方法,实现了在占用少量硬件资源的前提下,提高译码速度。

2 算法简述及系统结构分析Viterbi译码原理详见文献[1,2],下面仅作简要说明。

图1为(2,1,9)卷积码的2个状态之间的状态转移图。

根据输入路径的不同(图中实线表示输入为0,虚线表示输入为1),仅仅首位不同的两个状态可转移到仅仅末位不同的两个状态。

将所有状态的状态转移图按时间往前衍生,即可得到(2,1,9)卷积码的网格(Trellis)图。

Viterbi译码过程就是:根据接收序列,按照最大似然法则,分段地在网格图上计算寻找有最大度量的路径的过程。

一般来说,维特比泽码器主要有4个单元所组成,其结构框图如图2所示。

分支度量单元(BMU) 主要是计算分支度量值。

所谓分支度量值就是码字与接收码之间的距离。

加-比较-选择单元(ACSU) 主要是做路径度量值与分支度量值的叠加,并决定幸存路径度量值及决定位元(decision bit)。

路径度量存储单元(PMMU) 主要用来存储幸存路径度量值。

幸存路径存储单元(SMU) 主要用来存储决定位元。

如图2所示,接收序列先通过分支度量单元计算出各状态所有分支度量,然后经过ACS单元,将上一时刻的路径度量值与当前时刻的分支度量值作加-比较-选择等运算,计算出当前时刻的幸存路径和路径度量值,并找出决定位元(decision bit),把新的路径度量值存储到路径度量存储单元(PMMU),并把相应的幸存路径的决定位元(de-cision bit)存储到幸存路径存储单元(SMU),当译码到译码深度后,判决输出单元输出译码序列。

HDTV接收机中Viterbi译码器的FPGA实现

HDTV接收机中Viterbi译码器的FPGA实现高清晰度数字电视HDTV 技术是当今世界上最先进的图像压缩编码技术和数字通信技术的结合。

它代表一个国家的科技综合实力,蕴藏着巨大的市场潜力。

数字电视地面广播编码正交频分复用COFDM 传输系统以其较强的抗多径干扰性能、易于实现移动接收等优点在HDTV 的研究中占有很重要的地位。

而COFDM 系统中编、解码技术是影响系统性能的一个重要因素。

本文正是基于一种最大似然译码--Viterbi VB 译码算法思想,从FPGA 实现的角度探讨在COFDM 系统中内码(收缩卷积码)的解码。

1 设计算法简述在HDTV 地面广播COFDM 系统中,所用内码为收缩卷积码,除1/2 主码率外,还有2/3、3/4、5/6、7/8 码率的卷积编码。

在实际的传输信道中,噪声一般是加性高斯白噪声(AWGN),输入AWGN 信道的是二进制信号序列。

为了充分利用信道输出信号的信息,提高传输系统译码的可靠性,首先把信道的输出信号量化,将Q 电平量化序列输入Viterbi 译码器,因此本文采用的VB 译码算法为软判决译码算法。

1.1 主码率1/2 的卷积码编码目前,在国际卫星通信和很多通信系统中,(2,1,6)码是首选的使用VB 译码的标准卷积码。

由于该码能使误码率达到最小,且能克服相位误差,所以在HDTV 地面广播COFDM 传输系统中,内码采用(2,1,6)码,它的子生成元为(171,133),均为八进制。

对应的生成多项式G D=1+D+D2+D3+D6 1+D2+D3+D5+D6 df=10。

其编码器的实现框图如图1。

由于(2,1,6)码有64 个状态,为直观起见,采用列表的方法来表述它的篱笆图,如表1 所示。

1.2 收缩卷积码的实现为了实现多码率传输,在提高码率的情况下不致使译码器的复杂性增加,在本设计中对(2,1,6)码进行增信删余(Puncctured)。

如图1 所示,在经上述编码后,对输出码字中的特定位置予以删除。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DATA_OUT 即为译码后的结果 , 其速率是译码前 数据bit的1/2。

CLK C E DATA _IN0 DATA _IN1

D0_ 0 D1_ 0

D0_ 1 D1_ 1

D0_ 2 D1_ 2

ቤተ መጻሕፍቲ ባይዱ1.2 viterbi 译码

卷积编码的译码需要在一个预定的时间内 , 通过迭代算法选择各种可能的路径 , 以找到最佳 路径。通过把支路度量(局部距离)加到两个原状 态的最佳路径度量上 , 得到到达新状态 (J) 的两条 路径的度量值 , 从这两条路径的度量中选择一条 新状态(J)的路径和度量。Viterbi译码算法提供了 一种使数据-符号序列(格子路径)度量最小化的方 法。作为一种最大似然算法解码器,Viterbi译码算 法从接收序列中确定码序列 , 并使其和原发送序 列的匹配概率最高。 通常,Vit-erbi译码算法可分为 分支度量(局部距离)计算、状态度量更新和回溯跟 踪3个过程。 在卷积码译码中,Viterbi译码算法是纠错能力 很强的一种,已广泛应用于卫星通信系统。Viterbi 译码算法是一种最大似然译码算法。 Viterbi译码算法的步骤: 1) 根据接收码符号,计算出相应的分支量度 值; 2) 将进入某一状态的2条分支量度与其前面 的状态量度累加求和; 3) 比较到达同一状态的2条新的路径量度的 大小,选择最小者作为新的状态量度存储起来,并 记住与此路径(幸存路径)对应的信息码元; 4) 对所有的2m个状态都实施上述相加/比较 / 选择 (ACS) 运算; 路径量度最小的一条路径 ( 约为 以前码元长度的5倍)作为译码数据输出; 5) 将译码时刻向前延伸一步,重复以上步骤, 直至译码结束。

图1

(2,1,8)卷积码编码器基本结构

U ( D)G0 ( D ) 与时域运算 C1=u*g1 和 C0=u*g0 是等

作者简介:韩俊博(1987-),男,硕士研究生,研究方向:新型卫星导航信号接收处理。

第6期

韩俊博 等:基于 FPGA 的卫星导航信号 viterbi 译码方法研究

27

效的 ,* 代表卷积运算, 编码输出序列C1 、 C0 是输入 信息序列u与编码器生成多项式的卷积,这就是卷 积编码名称的由来。而卷积码生成码字的选择,往 往需要先确定码率 , 然后借助计算机来搜索性能 最好的码。本文所选用的(2,1,8)卷积码的码字就 是561,753。

26

机电技术

2012 年 12 月

基于 FPGA 的卫星导航信号 viterbi 译码方法研究

韩俊博 1 王 锋1 焦国太 1 耿生群 2

(1.中北大学机电工程学院,山西 太原 030051;2.北京航空航天大学电子信息工程学院,北京 100191) 摘 要:在介绍 Xilinx 公司 FPGA 的 Viterbi 译码器 IP 核译码模块设计的基础上,分析了广泛应用于卫星导航信号中

c0 d 0 d 2 d3 d 4 d8 c1 d 0 d1 d 2 d3 d5 d 7 d8

(1) (2)

1

编译码原理

1.1 卷积编码

卷积码是由连续输入的信息序列得到连续输 出的已编码序列。一个 (n,k,m)卷积编码器, 其中 k 为编码器输入数据的位数,n为编码器输出数据的 位数,m表示约束长度,R=k/n表示编码速率,它是衡 量卷积码传输信息有效性的一个重要参数。卷积 码把 k 个信息 bit 编成 n 个信息 bit, 但 k 和 n 通常都很 小,延时也较小,因此特别适合于传输串行形式的 信息。编码后的n个码元不但与当前段的k个信息 有关,而且与前面m段的信息有关。如果给定一个 卷积码的生成多项式 , 就可以根据这个生成多项 式将相应时刻输入的数据相异或 ( 模 2 加 ), 产生新 的编码输出。图1是一个(2,1,8)卷积码编码器的基 本结构。

c0

如果将参与异或的位设为1,不参与异或的位 设为 0, 那么对应于 c0 可以得到一个二进制码字 101110001, 对 应 于 c1 可 以 得 到 一 个 二 进 制 码 字 111101011。 这两个二进制码字用八进制来表示就 是561,753。 这就是卷积码的生成码字,只要生成码 字定了,该卷积码的码型也就选定了。 通常,在很多 资料文献中 , 生成码字还可用时延算子来表示就 是

G1 ( D) 1 D D 2 D 3 D 5 D 7 D8 G0 ( D) 1 D 2 D 3 D 4 D8

(3) (4)

式(4)中,D代表时延算子,D的幂表示延迟时间单元 数,D表示延迟1bit,即上个时刻输入码元,D2表示延 迟2bit,即上两个时刻输入码元,以此类推。假设输 入码元序列U为10111001……,用时延算子表示为

的卷积编码及 viterbi 译码过程,重点分析了关键问题,提出了具体模块设计方案,并进行仿真和硬件验证。 关键词:卷积编码;卫星通信;viterbi;译码 中图分类号:TJ85 文献标志码:A 文章编号:1672-4801(2012)06-026-03

目前,通信系统(包括各种数传系统、卫星通信 系统和第三代移动通信系统等 ) 在社会生活中占 有突出的地位。因此,如何提高信息传输的可靠性 就显得尤为重要,卷积编码和 Viterbi 译码是一种 高效的前向纠错技术 , 由于其具有很强的纠错性 能和适合硬件实现的编译码算法 , 卷积编码和软 判决维特比译码目前已经广泛应用于卫星通信系 统。在实际的工程应用中,纠错码正是提高信息传 输可靠性的一种重要手段。

U ( D) 1 D 2 D3 D 4 D 7

则输出编码序列也可用时延算子表示为

(5)

+

d0 d1 d2 d3 d4 d5 d6 d7 d8

C1 ( D) U ( D)G1 ( D) C0 ( D) U ( D)G0 ( D)

(6) (7)

+

c1

根据 C1(D),C2(D) 的时延算子表达式 , 即可求 出编码输出序列C1,C0。 可 以 证 明 , 在 C1 ( D)U ( D)G1 ( D) 和 C0 ( D)

图1中的寄存器d0,d1,d2,d3,d4,d5,d6,d7,d8分别存 储不同时刻输入的数据, 每来一个新的输入数据, 这8个寄存器中的数据就依次右移一位。 可以看出 编码输出c1、c0是分别将一些相应时刻输入的值取 出 来 相 异 或 得 到 的 。 编 码 输 出 c1,c0 与 d0,d1,d2,d3,d4,d5,d6,d7,d8的关系是