卷积码编码器及Viterbi译码器的设计

卷积码的编码及解码Viterbi解码Word版

卷积码的编码及解码(Viterbi 解码)一、实验目的1、了解卷积码的基本原理;2、掌握卷积码编码的电路设计方法;2、掌握卷积码 Viterbi 译码的基本方法和电路设计方法。

二、实验仪器1、移动通信实验箱一台;2、台式计算机一台;三、实验原理1.卷积码编码原理卷积码是一个有限记忆系统,它也将信息序列切割成长度 k的一个个分组,与分组码不同的是在某一分组编码时,不仅参看本时刻的分组而且参看本时刻以前的 L 个分组。

我们把 L+1 称为约束长度。

2.卷积码的译码算法(硬判决 Viterbi 译码)Viterbi译码算法是一种最大似然算法,它不是在网络图上依次比较所有可能的路径,而是接收一段,计算,比较一段,保留最有可能的路径,从而达到整个码序列是一个最大似然序列。

Viterbi解码算法的基本步骤如下:1、从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。

对每一状态,挑选并存储一条有最大度量的部分路径及其部分度量,称此部分路径为留选(幸存)路径。

2、j增加1,把此时刻进入每一状态的所有分支度量,和同这些分支相连的前一时刻的留选路径的度量相加,得到了此时刻进入每一状态的留选路径,加以存储并删去其他所有的路径。

因此留选路径延长了一个分支。

3、若j<L+m,则重复以上步骤,否则停止,译码器得到了有最大路径度量的路径。

上面的过程可以简单的总结为“加、比、选”(也称ACS)。

四、实验步骤1、将实验箱和计算机通过串行口连接好,为实验箱上电。

2、将与实验箱相连的电脑上的学生平台程序打开。

在“实验选择”栏中选择“卷积码”实验,点击确认键。

从而进入此实验界面。

3、在实验界面上点“生成数据”,让系统生成待编码的随机比特。

也可在界面上直接双击所显示的 bit,修改其值。

4、在界面上点击下发“原始数据”,该数据将被送入单片机(或 CPLD)进行卷积编码然后经过编码的数据被送回学生平台并显示在“编码数据”栏。

Viterbi译码的MATLAB仿真研究

BUPT卷积码编码及Viterbi译码班级:07114学号:070422姓名:吴希龙指导老师:彭岳星邮箱:FusionBupt@1. 序言卷积码最早于1955年由Elias 提出,稍后,1957年Wozencraft 提出了一种有效地译码方法即序列译码。

1963年Massey 提出了一种性能稍差但是比较实用的门限译码方法,使得卷积码开始走向实用化。

而后1967年Viterbi 提出了最大似然译码算法,它对存储级数较小的卷积码很容易实现,被称作Viterbi 译码算法,广泛的应用于现代通信中。

2. 卷积码编码及译码原理2.1 卷积码编码原理卷积码是一种性能优越的信道编码,它的编码器和解码器都比较易于实现,同时还具有较强的纠错能力,这使得它的使用越来越广泛。

卷积码一般表示为(n,k,K)的形式,即将k 各信息比特编码为n 个比特的码组,K 为编码约束长度,说明编码过程中相互约束的码段个数。

卷积码编码后的n 各码元不经与当前组的k 个信息比特有关,还与前K-1个输入组的信息比特有关。

编码过程中相互关联的码元有K*n 个。

R=k/n 是编码效率。

编码效率和约束长度是衡量卷积码的两个重要参数。

典型的卷积码一般选n,k 较小,但K 值可取较大(>10),以获得简单而高性能的卷积码。

卷积码的编码描述方式有很多种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述,树图描述,网格图描述等。

2.1.1 卷积码解析表示法卷积码的解析表示发大致可以分为离散卷积法,生成矩阵法,码多项式法。

下面以离散卷积为例进行说明。

卷积码的编码器一般比较简单,为一个具有k 个输入端,n 个输出端,m 级移位寄存器的有限状态有记忆系统。

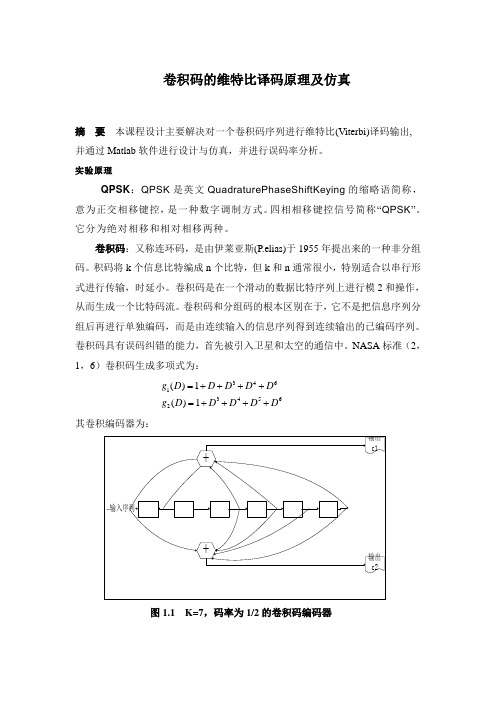

下图所示为(2,1,7)卷积码的编码器。

若输入序列为u =(u 0u 1u 2u 3……),则对应两个码字序列c ①=(c 0①c 1①c 2①c 3①……)和c ②=(c 0②c 1②c 2②c 3②……)相应的编码方程可写为c ①=u ∗g ①,c ②=u ∗g ②,c=(c ①,c ②)。

(2,1,7)卷积码Viterbi译码器FPGA实现方案

(2,1,7)卷积码Viterbi译码器FPGA实现方案韩可;邓中亮;施乐宁【摘要】移动通信系统标准中普遍采用卷积码作为信道编码方案.本文阐述了目前最常用的卷积码译码算法——Viterbi译码算法,然后给出了(2,1,7)卷积码编码电路FPGA实现方法.该方法给出了新的Viterbi幸运路径算法和高效的状态度量存储技术,可以充分利用FPGA的优势获得较好的译码结果.利用幸存路径交换寄存器模块,能有效减少存储量并降低功耗.【期刊名称】《现代电子技术》【年(卷),期】2007(030)015【总页数】4页(P90-92,96)【关键词】Viterbi译码;FPGA;卷积码;寄存器交换;回溯【作者】韩可;邓中亮;施乐宁【作者单位】北京邮电大学,电子工程学院,北京,100876;北京邮电大学,电子工程学院,北京,100876;北京航空航天大学,电子信息工程学院,北京,100083【正文语种】中文【中图分类】TN74在无线通信过程中,信道中的噪声干扰会造成接收端的一定的误码率,这必定会影响无线数据传输的精确性。

为了解决这一问题经常采用信道编码技术。

卷积编码和Viterbi译码是广泛使用的信道编码技术,具有一定的克服突发错误的能力,可以降低信道的误码率,带来很高的编码增益。

因而卷积编码和Viterbi译码也是目前移动通信中的重要组成部分。

1 (2,1,7)卷积码Viterbi译码原理卷积码的译码方式有3种[1]:Viterbi译码、序列译码、门限译码。

Viterbi译码具有最佳性能。

Viterbi译码的主要思想就是根据产生卷积码的网格图[2](或称为状态图),图1以(2,1,3)码为例,确定最可能的发送序列,这个最可能的发送序列对应网格图上的某一特殊路径。

译码时,将接收序列与网格图上所有可能的传输路径相比较,求其汉明距离,从中选择具有最小距离的发送序列,距离最小表示接收码取此序列的可能性最大。

假设为(n,k,N)码,下面详细叙述Viterbi译码算法。

卷积编码及Viterbi译码的低时延FPGA设计实现

卷积编码及Viterbi译码的低时延FPGA设计实现张健,吴倩文,高泽峰,周志刚(杭州电子科技大学电子信息学院袁浙江杭州310018)摘要:针对毫米波通信的高速率和低时延设计要求,设计实现1/2码率(2,1,7)卷积码的低时延译码。

采用高度并行优化实现框架、低延时的最小值选择方式,获得Viterbi硬判决译码算法的输出遥利用基于Xilinx公司的Artix7-xc7a200t芯片综合后,译码器的数据输出延时约89个时钟周期,最高工作频率可达203.92MHz遥结果表明,该译码器可支持吉比特级的数据传输速率,实现了低延时、高速率的编译码器遥关键词:毫米波通信;卷积码;Viterbi译码;system generator中图分类号:TN911.22文献标识码:A DOI:10.16157/j.issn.0258-7998.201025中文引用格式:张健袁吴倩文,高泽峰袁等.卷积编码及Viterbi译码的低时延FPGA设计实现[J].电子技术应用,2021,47 (6):96-99.英文弓I用格式:Zhang Jian,Wu Qianwen,Gao Zefeng,et al.Low-latency FPGA design and implementation of convolutional coding and Viterbi decoding[J].Application of Electronic Technique,2021,47(6):96-99.Low-latency FPGA design and implementation of convolutionalcoding and Viterbi decodingZhang Jian,Wu Qianwen,Gao Zefeng,Zhou Zhigang(School of Electronic Information,Hangzhou Dianzi University,Hangzhou310018,China)Abstract:Aiming at the high-speed and low-delay design requirements of millimeter wave communications,this paper designs low-delay decoding of convolutional codes with1/2code rate(2,1,7).A highly parallel optimization implementation framework and a low-latency minimum selection method are adopted to obtain the output of the Viterbi hard decision decoding algorithm.After synthesis using the Artix7-xc7a200t chip based on Xilinx,the data output delay of the decoder is about89clock cycles,and the highest operating frequency can reach203.92MHz.The results show that the decoder can support gigabit-level data transmission rates,and realizes a low-latency,high-rate codec.Key words:millimeter wave communication;convolutional code;Viterbi decoding;system generator0引言近年来,5G移动通信技术的发展受到人们的广泛关注,高速率、高可靠、低时延的高能效通信成为毫米波通信中的重要因素[1-2」。

数字通信中的卷积编码及Viterbi译码器设计

必 须 采 用 差 错 控 制 编码 等信 道 编码 技 术 ,使 误 码

率 进 一步 降低 。 差错 控 制 编 码 的基 本 过 程 是 :在 发 送 端 被 传

的标 准 中等 等 。当然 , 可 以应用 在 有线 通 信 的数 也 字视 频 广播 ( V 系统 之 中 。在 欧 洲制 定 的 D B D B) V — C标准 中 ,采 取 了卷积 码 和 分组 码 级 联 的方 法 , 即 以 约 束 长 度 为 7的卷 积 码 作 为外 码 , R ( e d 以 S R e— S l m n 码 作 为 内码 。 oi o ) o

1 差错 控制编 码的概 述

数 字信息 在有 噪声 的信道 中传输 时 ,会受 到噪

声 干扰 的影响 , 码总 是不可 避免 的 。 码率 的大小 误 误

差 错 控 制 编 码 所 要 解 决 的 问题 就是 探 索 各 种

Hale Waihona Puke 编码 和译 码 方 法 。其基 本 方 法有 两 种 , 种 是 自动 一 重 发 请 求 ( Q: uo t e et R q et方 法 , AR A tma c R p a e u s) i

即在 接 收端 能够 通 过 检验 约束 关 系来 发 现 错误 , 然

后 通 知发 送 端重 新 发送 出错 的部 分 ; 另一 种 是前 向 纠错 ( E F r ad E rr C r ci ) 法 , 收 端 F C: ow r r or t n 方 o e o 接

与许 多 因素有关 ,最基 本 的就是 信道 中随机干扰 的 大 小相 对 于有 用信 号 的强 度 比 , 即信 噪 比( v 。 E 0 ) 根 据 香 农 信 息 理 论 , 要 使 只 足 够 大 , 可 以 就

通过Viterbi译码算法实现译码器优化实现方案

通过Viterbi译码算法实现译码器优化实现方案

1 引言

由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。

卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。

从工程应用角度看,对Viterbi译码器的性能*价指标主要有译码速度、处理时延和资源占用等。

本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。

测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。

2 卷积编码网格图特点

图1所示为卷积编码网格图结构,图中每一状态有两条输入支路和两条输出支路。

2.1 输入支路的特点

任意一个状态节点Si都有两条输入支路,且这两条输入支路对应的源节点分别为:

此外,i为偶数时,两条输入支路的输入信息都为‘1’;i为奇数时,两条输入支路的输入信息都为‘0’。

2.2 输出支路的特点

任意一个状态节点Si都有两条输出支路,且两条输出支路对应的目的节点分别为:

此外,目的节点是Sj1的输出支路对应的输入信息都为‘0’;目的节点是Sj2的输出支路对应的输入信息都为‘1’。

3 Viterbi译码器的优化算法

3.1 判决信息比特与路径信息向量同步存储算法。

卷积码的维特比译码原理及仿真

卷积码的维特比译码原理及仿真摘 要 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab 软件进行设计与仿真,并进行误码率分析。

实验原理QPSK :QPSK 是英文QuadraturePhaseShiftKeying 的缩略语简称,意为正交相移键控,是一种数字调制方式。

四相相移键控信号简称“QPSK ”。

它分为绝对相移和相对相移两种。

卷积码:又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

积码将k 个信息比特编成n 个比特,但k 和n 通常很小,特别适合以串行形式进行传输,时延小。

卷积码是在一个滑动的数据比特序列上进行模2和操作,从而生成一个比特码流。

卷积码和分组码的根本区别在于,它不是把信息序列分组后再进行单独编码,而是由连续输入的信息序列得到连续输出的已编码序列。

卷积码具有误码纠错的能力,首先被引入卫星和太空的通信中。

NASA 标准(2,1,6)卷积码生成多项式为: 346134562()1()1g D D D D D g D D D D D=++++=++++其卷积编码器为:图1.1 K=7,码率为1/2的卷积码编码器维特比译码:采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果接收到L 组信息比特,每个符号包括v 个比特。

接收到的Lv 比特序列与2L 条路径进行比较,汉明距离最近的那一条路径被选择为最有可能被传输的路劲。

当L 较大时,使得译码器难以实现。

维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。

下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

卷积编码和Viterbi译码

卷积编码和Viterbi译码摘要本文的目的是向读者介绍了前向纠错技术的卷积编码和Viterbi译码。

前向纠错的目的(FEC)的是改善增加了一些精心设计的冗余信息,正在通过信道传输数据的通道容量。

在添加这种冗余信息的过程称为信道编码。

卷积编码和分组编码是两个主要的渠道形式编码。

简介前向纠错的目的(FEC)的是改善增加了一些精心设计的冗余信息,正在通过信道传输数据的通道容量。

在添加这种冗余信息的过程称为信道编码。

卷积编码和分组编码是两个主要的渠道形式编码。

卷积码串行数据操作,一次一个或数位。

分组码操作比较大(通常,多达几百个字节的情侣)消息块。

有很多有用的分组码和卷积多种,以及接收解码算法编码信息的DNA序列来恢复原来的各种数据。

卷积编码和Viterbi译码前向纠错技术,是一种特别适合于在其中一个已损坏的发射信号加性高斯白噪声(AWGN)的主要通道。

你能想到的AWGN信道的噪声,其电压分布也随着时间的推移,可以说是用高斯,或正常,统计分布特征,即一钟形曲线。

这个电压分布具有零均值和标准差这是一个信号与噪声比接收信号的信噪比(SNR)函数。

让我们承担起接收到的信号电平是固定的时刻。

这时如果信噪比高,噪声标准偏差小,反之亦然。

在数字通信,信噪比通常是衡量Eb /N的它代表噪声密度双面能源每比特除以之一。

卷积码通常是描述使用两个参数:码率和约束长度。

码率k/n,是表示为比特数为卷积编码器(十一)信道符号卷积编码器输出的编码器在给定的周期(N)的数量之比。

约束长度参数,钾,表示该卷积编码器的“长度”,即有多少K位阶段提供饲料的组合逻辑,产生输出符号。

K是密切相关的参数米,这表明有多少位的输入编码器周期被保留,用于编码后第一次在卷积编码器输入的出现。

的m参数可以被认为是编码器的记忆长度。

在本教程中,并在此示例的源代码,我集中精力率1 / 2卷积码。

Viterbi译码是一种两个卷积编码与解码,其他类型的算法类型的顺序解码。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.

卷积码是一种性能优越的信道编码。(n ,k ,N) 表示把 k 个信息比特编成 n 个比特,N 为编码约束长度,说明编码过程中互相约束的码段个数。卷积码编码后的 n 个码元不仅与当前组的 k 个信息比特有关,而且与前 N - 1 个输入组的信息比特有关。编码过程中相互关联的码元有 N ×n 个。R = k/ n 是卷积码 的码率,码率和约束长度是衡量卷积码的两个重要参数。 卷积码的编码描述方式有很多种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述,树图描述,网格图描述等。卷积码的纠错能力随着 N 的增加而增大,而差错率随着 N 的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。分组码的译码算法可以由其代数特性得到。卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码[5]。

Abstract:This course design mainly resolves to a convolutional code sequence for Viterbi Viterbi decoding output, and through the Matlab software to carry on the design and simulation, and analysis of bit error rate. In curriculum design, system development platform for Windows Vista Ultimate, program design and simulation using Matlab R2007a(7.4), and finally the simulation list is consistent with theoretical analysis.

1.

图1一种卷积码编码器方框图

图1卷积码的编码器一般都比较简单。下图1是一般情况下的卷积码编码器框图。它包括:一个由 N 段组成的输入移位寄存器,每段有 k 级,共 Nk 位寄存器; 一组 n 个模 2 和相加器;一个由 n 级组成的输出移位寄存器。对应于每段 k 个比特的输入序列,输出 n 个比特。由图可知,n 个输出比特不但与当前 k 个比特的输入比特有关,而且与以前的(N-1)k 个输入信息有关。整个编码过程可以看成是输入信息序列与由移位寄存器和模 2 加法器的连接方式所决定的另一个序列的卷积,卷积码由此得名。

随着现代通信的发展,高速信息传输和高可靠性传输成为信息传输的两个主要方面,而可靠性尤其重要。卷积码以其高速性和可靠性在实际应用中越来越广泛。1967年Viterbi译码算法的提出,使卷积码成为信道编码中最重要的编码方式之一[1]。

在对卷积码的研究中,其中编码器较简单,模式也很统一。主要是研究提高卷积码的译码速度和可靠度。译码算法中最重要的卷积码的Viterbi算法问世以来,软件仿真和实现都得到了迅速发展。目前,利用计算机仿真Viterbi算法,模拟在各种不同情况下(使用不同码率、不同约束度等)卷积编码时的译码性能,寻找Viterbi算法的最佳适用信道和不同要求(如误码率)下最优编码。在卷积码中,因为Viterbi算法效率高,速度快,结构相对简单等特点,被广泛应用于各种数据传输系统。特别是深空通信、卫星通信系统中。在现代信息处理系统中,需要处理的信息量越来越大,实时性要求越来越高。为减少对主处理器各种资源的占用,要求通信模块方面的大部分工作能独立完成。因此采用Viterbi译码算法具有非常现实的意义[2]。

毕业论文(设计)

题目:卷积码编码器及Viterbi译码器的设计

学生姓名:琳

学号:

所在系别:电气信息工程学院

专业名称:通信工程

届次:

指导教师:

卷积码编码器及Viterbi译码器的设计

学生:陈琳(指导老师:王千春)

(淮南师范学院电气信息工程学院)

摘要:本毕业设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输,并通过Matlab软件进行设计与仿真,并进行误码率分析。在毕业设计中,系统开发平台为Windows Vista Ultimate,程序设计与仿真均采用Matlab R2007a(7.4),最后仿真详单与理论分析一致。

这次毕业设计研究卷积码的编码方法和解码方式。编写卷积码的编码和解码程序。掌握卷积码编码及Viterbi译码的基本原理。分析卷积码编码及Viterbi译码的关键技术。对卷积码编码器及Viterbi译码器进行设计。用卷积码编码器及Viterbi译码器进行仿真,并进行性能分析。理解卷积码的编码和解码原理和过程,会通过编码和解码程序对一些卷积码进行仿真。对卷积码编码器及Viterbi译码器进行仿真验证,并分析性能。尽可能对系统进行优化。能运用MATLAB软件进行仿真[4]。

Key words:graduation thesis; Convolutional code decoder; Matlab; Design and simulation

前

本毕业设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真。卷积码的译码有两种方法——软判决和硬判决,此毕业设计采用硬判决的维特比译码。

由于卷积码的优良特性,被广泛的应用于深邃通信,卫星通信和2G及3G移动通信中,卷积码有三种译码方法:门限译码,概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。Viterbi译码充分发挥了卷积码的特点,使译码错误概率达到最小,在码的约束度教小时,它有译码算法效率高,速度快,译码也简单的特点[3]。

关键词:毕业论文;卷积码译码器;Matlab;设计与仿真

Design of the ViterbiConvolutionalCodeEncoder andDecoder

Student: Chen Lin(Instructor:WANG qian chun)

(Electrical and information engineering college of communication engineering)