FPGA综合设计报告

FPGA实验设计报告—广东技术师范学院

实验报告课程名称:FPGA设计及应用实验项目:FPGA设计实验时间:2014.12.8-2014.12.31实验班级:12应用师3班总份数:共 5 份指导教师:李豪彦电子与信息学院工业中心504 实验室二〇〇四年十二月十七日广东技术师范学院实验报告学院: 电信学院 专业: 应用电子技术教育 班级: 12应用师3班 成绩: 姓名: 张文斌 学号: 2012045344209 组别:组员:实验地点: 工业中心实验日期:指导教师签名:实验 (一) 项目名称: D 分 频 器设计一、实验目的1.学习分频器的设计,进一步了解、熟悉和掌握FPGA 开发软件Quartus II 的使用方法2.学习Verilog HDL 和VHDL 的编程方法二、实验内容编写一个分频器的Verilog 代码和VHDL 代码并仿真。

三、实验原理在数字电路中, 时钟信号的分频是很常见的电路。

分频器除了可以对时钟信号频率做除以二的计算外,分频器同时很类似涟波计数器。

涟波计数器是计数器的一种,它属于异步设计。

因为触发器并非皆由同一个时钟信号同步操作,所以它非常节省电路面积。

本实验要设一个带选择的分频时钟D[7:0]用于选择是几分频。

D 分频器设原理框图如图1所示:图1.D 分频器原理框图预习情况操作情况 考勤情况 数据处理情况四、实验步骤1.新建工程,取名为DVF,如下图2所示。

图2 新建工程DVF2.新建VHDL设计文件,选择“File|New ”,在New 对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol ”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol ”以及输入输出管脚,最后完整的系统顶层模块图如图 3 所示。

图3 DVF 顶层模块图5.保存文件,使用qsf或者tcl 进行管脚分配。

FPGA设计的报告课程设计

FPGA课程设计实验报告实验一:设计一个可控的100进制可逆计数器一、实验要求用DE2-115开发板下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用clr plus minus 功能0 ××复位为01 1 0 递增计数1 0 1 递减计数1 1 1 暂停计数二、关键词可控制、可逆、100进制、复位、暂停、递增、递减三、内容摘要module updown_count(qout,reset,clk,plus,minus);output[7:0] qout;/*定义一个8位的输出,其目的是低四位和高四位分别表示计数器的个位和十位。

*/input clk,plus,minus,reset;//定义四个输入,时钟,加计数,减计数和清零reg[7:0] qout;//qout的数据类型为寄存器型always @(posedge clk)//当clk上升沿到来时执行一遍下列程序beginif(!reset) qout<=0;//当reset为低电平时,计数器执行清零功能,否则跳过elsebegincase({minus,plus})//case语句模块,包含加,减和暂停四个模块2'b10:if (qout[3:0]==0)//判断个位是否为零,若不为零,跳到个位减一beginqout[3:0]<=9;//给个位赋值if(qout[7:4]==0) qout[7:4]<=9;//判断十位是否为零,并且给十位赋值elseqout[7:4]<=qout[7:4]-1;//由于个位赋9,相当于向十位借一,因而十位减一endelseqout[3:0]<=qout[3:0]-1;//个位减一/*这一部分是减计数模块,其思路是:首先判断个位是否为零,若为零,则执行后面的程序,个位直接赋9,并且十位减一;否则个位减一*/ 2'b01:if (qout[3:0]==9)//判断个位是否为9,否则跳到个位加一beginqout[3:0]<=0;//若上面个位为9判断成立,则给个位赋值if(qout[7:4]==9) qout[7:4]<=0;//判断十位是否为9,若为9,则赋0elseqout[7:4]<=qout[7:4]+1;//若十位不为9,十位加一endelseqout[3:0]<=qout[3:0]+1;//个位加一/*这一部分是加计数模块,首先判断个位是否为9,若不为9,个位加1;否侧,再判断十位是否为9,若为9,十位赋0,否侧十位加1。

fpga实验报告

fpga实验报告FPGA实验报告引言随着科技的发展和计算机应用的广泛应用,人们对于计算机硬件的需求也越来越高。

在这个背景下,FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,被广泛应用于数字电路设计和嵌入式系统开发。

本篇文章将就FPGA的基本原理、实验设计和实验结果进行探讨。

一、FPGA的基本原理FPGA是一种可编程逻辑器件,它由一系列可编程逻辑单元(PLU)和可编程互连资源(PIM)组成。

PLU可以根据用户的需求进行编程,实现不同的逻辑功能。

PIM则用于连接不同的PLU,构成用户所需的电路结构。

FPGA的可编程性使得它能够根据不同的应用需求进行灵活的配置和重构,具有很高的可扩展性和适应性。

二、FPGA实验设计在FPGA实验设计中,我们通常需要进行电路设计、编程和仿真等步骤。

1. 电路设计FPGA实验中的电路设计是实验的核心环节。

我们需要根据实验要求,设计出符合要求的逻辑电路。

在设计过程中,我们可以使用硬件描述语言(HDL)如Verilog或VHDL来描述电路结构和功能。

通过对电路进行分析和优化,我们可以得到满足实验要求的电路设计。

2. 编程在电路设计完成后,我们需要将电路设计转化为FPGA可识别的编程文件。

这一步骤通常使用专门的软件工具来完成,如Xilinx ISE或Quartus II。

通过这些软件工具,我们可以将电路设计转化为FPGA可执行的bit文件。

3. 仿真在将编程文件下载到FPGA之前,我们通常需要进行仿真验证。

通过仿真,我们可以验证电路设计的正确性和性能。

仿真可以帮助我们发现潜在的问题和错误,从而提前解决,确保实验的顺利进行。

三、FPGA实验结果在实验过程中,我们通过将编程文件下载到FPGA上,使其实现我们设计的逻辑电路。

通过实验,我们可以获得电路的输出结果,并对其进行验证和分析。

1. 输出验证通过与设计预期结果进行比对,我们可以验证电路的输出是否符合预期。

FPGA综合设计报告

FPGA综合设计报告载波信号发生器设计一、实验目的1. 熟悉Quaturs II软件的使用。

2. 掌握正余弦查找表的用途、设计和使用方法。

3. 掌握用VerilogHDL硬件描述语言建模时序逻辑电路的能力。

二、实验内容1.计算正余弦信号采样值用C/C++编写程序,计算一个周期内的正余弦信号的采样值,一个周期采样32次。

要求对采样值和2的幂次倍(例如16、32、64、128等)进行倍乘后处理成适当的整数值,对每个整数值进行8位二进制编码。

注意:计算机中对负数用补码表示。

计算正弦信号采样值的C语言程序及注释:#include<iostream>#include<cstdio>#include<cmath>using namespace std; //C++及C 语言库函数头文件#define PI 3.141592653 //宏定义PI数值#define N 32 //定义放大倍数及累加变量为32,可以修改为64或者是128 int main(){double sinValue[N]; //sinValue为的抽样的数值int outValue[N];for(int i=0;i<N;i++)sinValue[i]=N*sin(i/(N+0.0)*2*PI); //得到放大32倍的抽样数值for(i=0;i<N;i++){outValue[i]=(int)sinValue[i]; //对得到的数值进行整数化cout<<"LUT[ "<<i<<" ] "<<"<="<<outValue[i]<<";"<<endl; //以标准格式输出文件}cout<<endl;return 0;}2.设计查找表用VerilogHDL 建模一个载波信号发生模块,将第 1 步中得到的采样值写入查找表。

FPGA课程设计报告

FPG课程设计—256个8位计数器技术规范一、实现功能:用一个8×256的单口RAM完成256个8位计数器,计数器的初值分别为0-255,时钟频率为10MHz,计数器计数频率为5/256MHz。

具体功能描述如下:1、分频模块:时钟频率为10MHz,要实现计数器计数频率为5/256MHz,将其时钟频率进行2分频送入。

每来一个时钟,计数器计一个数。

第一个时钟来时,第一个计数器计1,此时,此计数器中的值变为1,其余的计数器中的值不变,以此类推,直到第256个时钟来时,第256个计数器计1,计数器中的值255变为0,以此类推,完成256个8位计数器,得到计数器计数频率即为5/256MHz。

2、8x256的单口RAM模块:定义一块内存为8x256的单口RAM,只有一条地址线,读写共用一个地址单元,当使能信号we=1时,写有效,可以将数据写入RAM,当使能信号we=0,读有效,可以将RAM中的值输出。

3、写模块:当时能信号we=1时,写有效,当clk的上升沿到来时,可以将数据写入寄存器,在时钟的上升沿和reset的下降沿时,如果reset=0,则地址addr=0,计数器a=0;否则,如果使能信号we=1,地址addr递加,当addr大于255时,addr=0,计数器a=a+1,将addr+a送入数据输入data_in.。

二、系统I/O管脚的描述:三、拟选用的FPGA类型:ep1cq240c8n总体设计方案一、整体设计方案我构想了如下两个总体设计方案:第一个总体设计方案:将10MHz的时钟clk_in通过分频器进行2分频送入系统clk,触发条件是clk的上升沿,这就可以实现计数器计数频率为5/256MHz。

由于是单口RAM,所以只有一条地址线,要么只能写入数据,要么只能读出数据。

因此,我先将所有的寄存器清零,将0—255这256个计数器初值分别送入256个寄存器,此时采用一个加法计数器完成。

然后每来一个时钟clk,计数器中的值计1,同时地址加1,即第一个寄存器的0变成1,地址加到第二个寄存器,以此类推,完成256个8位计数器的计数,并且将计数器的值读出。

FPGA实验报告 系统设计综合实践 自动售货机

FPGA实验报告系统设计综合实践自动售货机引言本实验报告旨在介绍FPGA实验中关于系统设计综合实践的内容,以及针对自动售货机的设计和实现过程。

本项目的目标是通过FPGA实现一个基本的自动售货机,能够接受货币投入并显示余额,实现商品选择和出货的功能。

设计概述在本项目中,我们使用FPGA作为硬件平台进行实现,采用VHDL语言进行编程。

整个设计主要分为三个模块:货币处理模块、商品选择模块和出货控制模块。

货币处理模块货币处理模块负责接收和处理投入的货币,并显示当前的余额。

具体实现过程如下:1.接收货币输入:使用FPGA板载的GPIO接口连接硬币接收器,将接收到的信息传递给FPGA。

2.处理货币信息:通过计算接收到的货币数量和面额,计算出当前的余额。

3.显示余额:使用FPGA板载的数码管显示当前的余额。

根据计算得到的余额,将其显示在数码管上。

商品选择模块商品选择模块负责接收用户的商品选择,并计算选中商品的价格。

具体实现过程如下:1.接收商品选择:使用FPGA板载的按键输入接口,接收用户按下的相应按键,确定用户选择的商品。

2.计算商品价格:根据用户选择的商品,从预先配置的商品价格表中查找相应的价格。

3.显示选中商品价格:使用FPGA板载的数码管显示选中商品的价格。

根据查找到的价格,将其显示在数码管上。

出货控制模块出货控制模块负责控制商品的出货和相关信息的提示。

具体实现过程如下:1.判断余额是否足够:根据当前余额和选中商品的价格,判断余额是否足够购买商品。

2.控制商品出货:如果余额足够购买商品,则触发相应的出货机构,实现商品的出货。

3.提示用户相关信息:根据出货情况,通过数码管显示相关信息,如余额不足、出货成功等提示。

实验结果经过对上述三个模块的设计和实现,我们成功地完成了自动售货机的基本功能。

在实验过程中,我们选取了几种常见的商品,并配置了相应的价格表。

通过按下相应的按键,用户可以选择购买的商品,并通过投币的方式支付。

FPGA实验报告5篇

FPGA实验报告5篇第一篇:FPGA实验报告FPGA实验报告专业:XXX 姓名:XXX 学号:XX一:实验目的1.熟悉Modelsim和Quartus II软件的运行环境和使用2.熟练使用Quartus II仿真软件生成网表。

3.熟悉FPGA前仿真和后仿真的整个流程。

二:实验内容编写counter计数器,在Quartus II仿真软件中生成网表,再在Modelsim中进行后仿真。

三: 实验步骤1.在Modelsim编写源程序(counter计数器及激励),编译源文件,确保程序的正确性,并进行前仿真,生成波形图如下:附:源程序如下:module counter(q,clk,reset);input clk,reset;output [3:0] q;reg [3:0] q;always @(posedge reset or negedge clk)if(reset)q <= 4'b0;elseq <= q + 1;endmodule module top;reg CLK,RESET;wire [3:0] Q;counter c1(Q,CLK,RESET);initialCLK=1'b0;always#1 CLK=~CLK;initial$monitor($time,“Q=%d”,Q);initialbeginRESET=1'b1;#5 RESET=1'b0;#180 RESET=1'b1;end endmodule 2.新建文件夹,将源程序counter.v放进去。

然后启动Quartus II仿真软件,生成网表。

1).在【File】下拉菜单中选中New Project Wizard选项,出现对话框。

并指定工程工作目录、工程名称和顶层模块名,如图(a)所示。

2).添加(Add)counter.v文件。

如图(b)所示。

3).选择器件系列4).指定其它EDA工具,如图(d)所示。

《FPGA系统设计》实验报告》有限状态机的设计

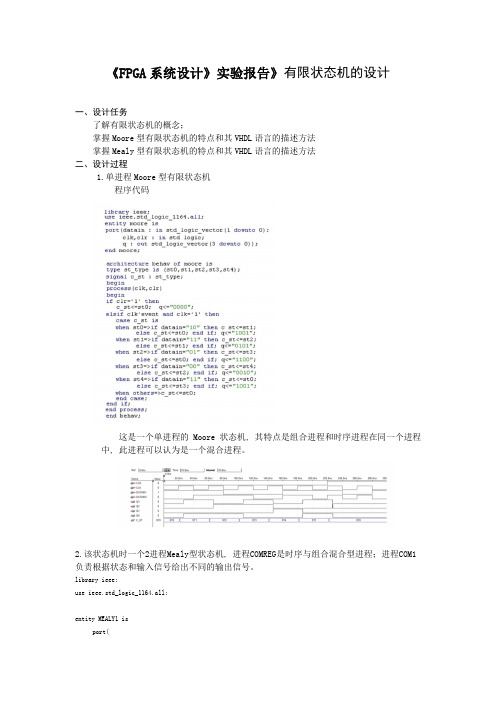

《FPGA系统设计》实验报告》有限状态机的设计一、设计任务了解有限状态机的概念;掌握Moore型有限状态机的特点和其VHDL语言的描述方法掌握Mealy型有限状态机的特点和其VHDL语言的描述方法二、设计过程1.单进程Moore型有限状态机程序代码这是一个单进程的Moore状态机, 其特点是组合进程和时序进程在同一个进程中, 此进程可以认为是一个混合进程。

2.该状态机时一个2进程Mealy型状态机, 进程COMREG是时序与组合混合型进程;进程COM1负责根据状态和输入信号给出不同的输出信号。

library ieee;use ieee.std_logic_1164.all;entity MEALY1 isport(clk,datain,reset : in std_logic;q : out std_logic_vector(4 downto 0));end MEALY1;architecture one of MEALY1 istype states is (st0,st1,st2,st3,st4);signal stx : states;begincomreg : process(clk,reset,datain,stx) --主控时序进程beginif reset = '1' then stx <= st0;elsif clk'event and clk = '1' thencase stx iswhen st0 => if datain = '1' then stx <= st1;end if;when st1 => if datain = '0' then stx <= st2;end if;when st2 => if datain = '1' then stx <= st3;end if;when st3 => if datain = '0' then stx <= st4;end if;when st4 => if datain = '1' then stx <= st0;end if;when others => stx <= st0;end case;end if;end process comreg;com1 : process(stx,datain) --主控组合进程begincase stx iswhen st0 => if datain = '1' then q <= "10000"; else q <= "01010"; end if;when st1 => if datain = '0' then q <= "10111"; else q <= "10100"; end if;when st2 => if datain = '1' then q <= "10101"; else q <= "10011"; end if;when st3 => if datain = '0' then q <= "11011"; else q <= "01001"; end if;when st4 => if datain = '1' then q <= "11101"; else q <= "01101"; end if;when others => q <= "00000";end case;end process com1;end one;3.该状态机属于Moore型状态机, 由两个主控进程构成, 其中进程REG是主控时序进程, COM是主控组合进程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA综合设计报告载波信号发生器设计一、实验目的1. 熟悉Quaturs II软件的使用。

2. 掌握正余弦查找表的用途、设计和使用方法。

3. 掌握用VerilogHDL硬件描述语言建模时序逻辑电路的能力。

二、实验内容1.计算正余弦信号采样值用C/C++编写程序,计算一个周期内的正余弦信号的采样值,一个周期采样32次。

要求对采样值和2的幂次倍(例如16、32、64、128等)进行倍乘后处理成适当的整数值,对每个整数值进行8位二进制编码。

注意:计算机中对负数用补码表示。

计算正弦信号采样值的C语言程序及注释:#include<iostream>#include<cstdio>#include<cmath>using namespace std; //C++及C 语言库函数头文件#define PI 3.141592653 //宏定义PI数值#define N 32 //定义放大倍数及累加变量为32,可以修改为64或者是128 int main(){double sinValue[N]; //sinValue为的抽样的数值int outValue[N];for(int i=0;i<N;i++)sinValue[i]=N*sin(i/(N+0.0)*2*PI); //得到放大32倍的抽样数值for(i=0;i<N;i++){outValue[i]=(int)sinValue[i]; //对得到的数值进行整数化cout<<"LUT[ "<<i<<" ] "<<"<="<<outValue[i]<<";"<<endl; //以标准格式输出文件}cout<<endl;return 0;}2.设计查找表用VerilogHDL 建模一个载波信号发生模块,将第 1 步中得到的采样值写入查找表。

要求能从任意主要相位处(0、π/4、π/2、3π/4、π、5π/4、3π/2、7π/4)输出载波信号。

载波信号发生模块的完整VerilogHDL代码及注释:module bdpsk(clk,reset,datain,dataout); //模块名为bdpsk,定义时钟、复位、输出端口信号名input clk; //clk为输入信号input reset; //reset为输入信号input [ 4 : 0 ] datain; //datain为输入信号output [ 7 : 0 ] dataout; //dataout为8位输出信号,最高位为符号位,补码表示reg [ 4 : 0 ] index; //从0到31的脚标变量reg [ 7 : 0 ] LUT [ 0 : 31 ]; //存储32个采样值reg [ 7 : 0 ] dataout;always @( posedge clk ) //时钟上升沿为触发信号beginif( reset ) //复位信号为高电平有效begin //码表,32个采样值LUT[ 0 ] <= 8'b0000_0000;LUT[ 1 ] <= 8'b0000_0110;LUT[ 2 ] <= 8'b0000_1100;LUT[ 3 ] <= 8'b0001_0010;LUT[ 4 ] <= 8'b0001_0111;LUT[ 5 ] <= 8'b0001_1011;LUT[ 6 ] <= 8'b0001_1110;LUT[ 7 ] <= 8'b0001_1111;LUT[ 8 ] <= 8'b0010_0000;LUT[ 9 ] <= 8'b0001_1111;LUT[ 10 ] <= 8'b0001_1110;LUT[ 11 ] <= 8'b0001_1011;LUT[ 12 ] <= 8'b0001_0111;LUT[ 13 ] <= 8'b0001_0010;LUT[ 14 ] <= 8'b0000_1100;LUT[ 15 ] <= 8'b0000_0110;LUT[ 16 ] <= 8'b0000_0000;LUT[ 17 ] <= 8'b1111_1010;LUT[ 18 ] <= 8'b1111_0100;LUT[ 19 ] <= 8'b1110_1110;LUT[ 20 ] <= 8'b1110_1001;LUT[ 21 ] <= 8'b1110_0101;LUT[ 22 ] <= 8'b1110_0010;LUT[ 23 ] <= 8'b1110_0001;LUT[ 24 ] <= 8'b1110_0000;LUT[ 25 ] <= 8'b1110_0001;LUT[ 26 ] <= 8'b1110_0010;LUT[ 27 ] <= 8'b1110_0101;LUT[ 28 ] <= 8'b1110_1001;LUT[ 29 ] <= 8'b1110_1110;LUT[ 30 ] <= 8'b1111_0100;LUT[ 31 ] <= 8'b1111_1010;endendalways @( posedge clk ) //时钟上升沿触发beginif( reset )beginindex <= 5'b0_0000; //复位信号为高电平时index清零endelsebeginindex <= datain;endendalways @( posedge clk ) //时钟上升沿触发beginif( reset)begindataout <= 8'bzzzz_zzzz; //当复位信号为高电平时输出高阻态endelsebegindataout <= LUT[ index ]; //当复位信号为低电平时输出采样值endendendmodule三、实验结果1.C++运行得到查找表的数值2.在Quaturs II软件下运行并仿真载波信号模块,得到功能仿真和时序仿真的波形,其波形截图为:功能仿真:时序仿真:BDPSK 调制器设计一、实验目的1. 熟悉 Quaturs II 软件的使用。

2. 掌握 BDPSK 原理的实现方法。

3. 掌握用 VerilogHDL 硬件描述语言建模时序逻辑电路的能力。

二、实验内容1.设计 BDPSK 调制器根据 BDPSK 调制原理,设计其调制器的外引脚和内部结构。

用Micorsoft Visio 软件画出外引脚图和内部结构图。

外引脚图:内部结构图:2.Quartus 软件设计的原理图3.用 VerilogHDL 建模根据设计的调制器引脚和结构,用VerilogHDL建模一个BDPSK调制模块。

能够根据连续输入的二进制数据,正确实现BDPSK调制。

(1)差分编码模块:module bdpsk_chafen (clk, reset ,bn,an); //在调制之前进行差分编码input clk; //定义时钟变量(分频模块的输出时钟)input reset; //定义复位信号input bn; //输入的绝对码output an; //差分编码输出reg pre_an; //相对码assign an=bn^pre_an; //描述逻辑方程_=⊕an bn pre an always@(posedge clk) //在时钟上升沿触发下进行差分编码beginif(an )pre_an<=1; //当复位信号为1时,pre_an清零elsepre_an<=0; //当复位信号为0时,pre_an存储差分编码结果an endendmodule(2)分频模块:module bdpsk_fenpin(clk_in,reset,clk) //时钟分频模块input clk_in; //定义输入时钟input reset; //定义复位信号output clk; //定义分频输出reg clk;wire i; //定义线型变量reg [4:0] count; //定义计数变量assign i=count[0]&&count[1]&&count[2]&&count[3]&&count[4];//为符合硬件实现方式而设计的方法,即当count=1111时,i=1 always@(posedge clk_in) //时钟上升沿触发beginif(reset) //当复位信号为1时,分频时钟输出为0,计数值清零beginclk<=0;count<=5'd0;endelsebegincount<=count+1; //当复位信号为0时,计数变量加1if(i) //当i=1时,表示count为1111,计数已经达到32,计数变量清零,clk翻转,实现64分频begincount<=5'd0;clk<=~clk;endendendendmodule(3)载波发生模块:module bdpsk_carry (clk_in,reset,datain,dataout); //模块名为bdpsk,定义时钟、复位、输出端口信号名input clk_in; //定义时钟输入信号input reset; //reset为复位信号output [ 7 : 0 ] dataout; //dataout为8位输出信号,最高位为符号位,补码表示reg [ 4 : 0 ] index; //从0到31的脚标变量reg [ 7 : 0 ] LUT [ 0 : 31 ]; //存储32个采样值reg [ 4 : 0 ] datain;reg [ 7 : 0 ] dataout;always @( posedge clk _in) //时钟上升沿为触发信号beginif( reset ) //复位信号为高电平有效begin //码表,32个采样值LUT[ 0 ] <= 8'b0000_0000;LUT[ 1 ] <= 8'b0000_0110;LUT[ 2 ] <= 8'b0000_1100;LUT[ 3 ] <= 8'b0001_0010;LUT[ 4 ] <= 8'b0001_0111;LUT[ 5 ] <= 8'b0001_1011;LUT[ 6 ] <= 8'b0001_1110;LUT[ 7 ] <= 8'b0001_1111;LUT[ 8 ] <= 8'b0010_0000;LUT[ 9 ] <= 8'b0001_1111;LUT[ 10 ] <= 8'b0001_1110;LUT[ 11 ] <= 8'b0001_1011;LUT[ 12 ] <= 8'b0001_0111;LUT[ 13 ] <= 8'b0001_0010;LUT[ 14 ] <= 8'b0000_1100;LUT[ 15 ] <= 8'b0000_0110;LUT[ 16 ] <= 8'b0000_0000;LUT[ 17 ] <= 8'b1111_1010;LUT[ 18 ] <= 8'b1111_0100;LUT[ 19 ] <= 8'b1110_1110;LUT[ 20 ] <= 8'b1110_1001;LUT[ 21 ] <= 8'b1110_0101;LUT[ 22 ] <= 8'b1110_0010;LUT[ 23 ] <= 8'b1110_0001;LUT[ 24 ] <= 8'b1110_0000;LUT[ 25 ] <= 8'b1110_0001;LUT[ 26 ] <= 8'b1110_0010;LUT[ 27 ] <= 8'b1110_0101;LUT[ 28 ] <= 8'b1110_1001;LUT[ 29 ] <= 8'b1110_1110;LUT[ 30 ] <= 8'b1111_0100;LUT[ 31 ] <= 8'b1111_1010;endendalways @( posedge clk_in ) //时钟上升沿触发beginif( reset )beginindex <= 5'b0_0000; //复位信号为高电平时index清零endelsebeginindex <= datain;endendalways @( posedge clk_in ) //时钟上升沿触发beginif( reset)begindataout <= 8'bzzzz_zzzz; //当复位信号为高电平时输出高阻态endelsebegindataout <= LUT[ index ]; //当复位信号为低电平时输出正弦波的采样值endendendmodule(4)调制模块:module dpsk_modulator (clk, an, carr, dataout);input clk; //时钟输入input an; //差分编码输入input [7:0] carr; //载波信号输入output [7:0] dataout; //调制波形输出reg [7:0] dataout;always @( posedge clk) //时钟上升沿触发beginif( an ) //如果差分编码输入为1,调制波形输出正弦波dataout<=carr;elsedataout<=-carr; //如果差分编码输入为0,调制波形输出余弦波endendmodule三、实验结果1.在Quaturs II软件下运行并仿真载波信号模块,得到功能仿真和时序仿真的波形,其波形截图为:功能仿真:时序仿真:。