位置比较脉冲调制输出

脉冲编码调制

脉冲编码调制* 脉码调制(Pulse Code Modulation)。

是一种对模拟信号数字化的取样技术,将模拟语音信号变换为数字信号的编码方式,特别是对于音频信号。

PCM 对信号每秒钟取样8000 次;每次取样为8 个位,总共64 kbps。

取样等级的编码有二种标准。

北美洲及日本使用Mu-Law 标准,而其它大多数国家使用A-Law 标准。

* PCM主要经过3个过程:抽样、量化和编码。

抽样过程将连续时间模拟信号变为离散时间、连续幅度的抽样信号,量化过程将抽样信号变为离散时间、离散幅度的数字信号,编码过程将量化后的信号编码成为一个二进制码组输出。

相关概念:所谓抽样,就是对模拟信号进行周期性扫描,把时间上连续的信号变成时间上离散的信号。

所谓量化,就是把经过抽样得到的瞬时值将其幅度离散,即用一组规定的电平,把瞬时抽样值用最接近的电平值来表示。

所谓编码,就是用一组二进制码组来表示每一个有固定电平的量化值。

脉冲编码调制(PCM,Pulse Code Modulation)。

)Claude E. Shannon于1948年发表的“通信的数学理论”奠定了现代通信的基础。

同年贝尔实验室的工程人员开发了PCM技术,虽然在当时是革命性的,但今天脉冲编码调制被视为是一种非常单纯的无损耗编码格式,音频在固定间隔内进行采集并量化为频带值,其它采用这种编码方法的应用包括电话和CD。

PCM主要有三种方式:标准PCM、差分脉冲编码调制(DPCM)和自适应D PCM。

在标准PCM中,频带被量化为线性步长的频带,用于存储绝对量值。

在DPCM中存储的是前后电流值之差,因而存储量减少了约25%。

自适应DPCM改变了DPCM的量化步长,在给定的信造比(SNR)下可压缩更多的信息。

希望我的回答对你有用biwaywbdk2009-08-18 23:02:50FANUC数控系统的操作及有关功能(北京发那科机电有限公司王玉琪)发那科有多种数控系统,但其操作方法基本相同。

freescale MC9S12P128中文手册

1Chapter1 Device Overview MC9S12P-Family 1.1介绍The MC9S12P 系列单片机是经过优化后有着低成本、高性能、低引脚数的汽车专业级单片机产品,该产品倾向于弥补高端16位单片及产品如MC9S12XS和低端8位单片机产品之间的空缺。

MC9S12P 主要针对于要求使用CAN 或者LIN/J2602通讯接口的汽车应用产品,典型的应用案例包括车身控制器、乘坐人员检测、车门控制、座椅控制、遥控车门开关信号接收器、智能执行器、车灯模块、智能接线器。

The MC9S12P 系列单片机使用了很多MC9S12XS系列单片机相同的功能,包括片内闪存错误纠正代码(ECC)、一个专为数据诊断或者数据存储的单独的数据闪存模块、高速AD转换器和高频调制锁相环(IPLL)有效改善电磁兼容性能。

MC9S12P系列单片机提供的所有16为单片机优点和微处理器效率,同时保持飞思卡尔用户熟悉的8位及16位单片机,低成本,功耗,EMC和高效的代码80针QFP、64针LQFP、40针QFN封装产品,最大限度的与MC9S12尺寸的优点,如同MC9S12XS一样可以无需等待外围设备和内存的状态既可以运行16为带款的寻址,MC9S12P系列单片机主要有XS引脚兼容. I/O口在各种模式下都可以使用,同时具有中断功能的I/O口还可以在停止或等待模式下唤醒。

1.2 芯片特性表一:提供了MC9S12P家庭成员特征摘要,1.P或D寄存器擦除或者编程需要最低总线频率为1MHZ1.2.2 芯片功能• S12 CPU 内核• 高达128 KB具有ECC功能的片上闪存• 4 Kbyte带ECC功能的数据闪存• 高达6 Kb片上静态存储器(SRAM)• 具有内部滤波器的锁相环倍频器(IPLL)• 4–16 MHz 皮尔斯振荡器• 1 MHz内部RC振荡器• 定时器(TIM) 具有16位输入捕捉、输出比较、计数器脉冲累加器功能• 具有8位6通道的脉冲调制模块(PWM)• 10通道12位分辨率的逐次逼近AD转换器• 1个串行通信外部接口(SPI)• 1个支持局域网通讯串行通信(SCI) 模块•一个多可扩展控制器区域网络(MSCAN) 模块(支持CAN 协议2.0A/B)•片上电压调节器(VREG) 可对内部供电及内部电压整流• 自主周期中断(API)1.3 模块特征1.3.1 CPUS12 CPU 是一个高速的16位处理单元:•全16-bit数据通道提供有效的数学运算和高速的数学执行• 包含很多单字节指令,可以有效的利用ROM空间• 宽域变址寻址功能:—采用堆栈指针作为所有变址操作的变址寄存器—除了在自增或自减模式下都可以利用程序计数器作为变址寄存器—使用A\B\D累加器做累加器偏移—自动变址,前递增(++a)、前递减(--a)、后递减(a--)、后递增(a++)(by –8 to +8)1.3.2 带ECC功能的片内闪存• 高达128 Kb程序闪存空间— 32 位数据加7 位ECC (纠错码) 允许单字节纠错和双字节纠错— 512字节擦出扇区空间—自动编程和擦除算法—用户设置读写页面边界—具有可以防止偶然编程或者擦除的保护结构• 4 Kb 数据闪存空间— 16 位数据加6位纠错码允许单字节和双字节纠错功能— 256 字节的擦出扇区空间—自动编程和擦除算法—用户设置读写页面边界1.3.3 片内静态存储器3高达6kb通用RAM1.3.4 外部晶振(XOSC)• 闭环控制皮尔斯晶振频率为4MHZ---16MHZ—振幅增益控制输出电流—低谐波失真信号Signal with low harmonic distortion—低功耗—良好的噪声免疫—无需外部限流电阻—跨导尺寸优化提供良好的振荡器启动保证1.3.5 内部RC晶振(IRC)• 可调的内部参考时钟—频率: 1 MHz—在–40°C to +125°C环境温度范围内调节精度达: 1.5%1.3.6 内部锁相环倍频器(IPLL)—无需外部元件—参考分频器和倍频器提供大变化量的时钟频率—自动带宽控制低频率抖动操作—自动锁定频率—可配置的选项,扩频减少电磁干扰EMC (频率调制frequency modulation) —参考时钟源:–外部4–16 MHz 共振器/晶振(XOSC)–内部RC晶振1 MHz (IRC)1.3.7 系统支撑• 上电复位(POR)• 系统复位发生器• 非法寻址复位•低电压检测中断或复位• 实时中断(RTI)• 计算机正常工作复位(COP) 开门狗—可通过相应窗口设置COP用以采用错误侦测复位通过位操作对闪存进行初始化复位•时钟监控器监控晶振功能正常工作1.3.8 定时器(TIM)• 8通道16位定时器可进行输入捕捉和输出比较• 16-bit带有7位精度预分频器的自由运行计数器•一通道16-bit 脉冲累加器1.3.9 脉冲带宽调制器(PWM)• 6通道8位or 3 通道16-bit脉宽调制器—每个通道都可以对周期和占空比进行编程—中心对齐或者左对齐输出—宽频率范围内可编程逻辑时钟1.3.10 局域网控制器(MSCAN)•速率达1Mbit/s, 满足CAN 2.0 A, B 协议—标准和扩展数据帧— 0–8 字节长度—可编程比特率达1 Mbps•5个FIFO(先进先出)的接收缓冲器•三个内部优先发送缓冲器• 灵活的标识符可编程选通滤波器s:— 2 x 32-bit— 4 x 16-bit— 8 x 8-bit•集成了低通滤波器的唤醒操作• 闭环反馈自检测• CAN 总线监听•总线关闭可通过软件干预或者自动恢复• 16-bit 接收发送信息时钟戳1.3.11 串行通信接口(SCI)•可选择全双工或单工模式•标准的不归零格式•通过可编程脉宽调制选用IrDA 1.4 反转归零格式• 13位波特率可选•可编程字符长度•可编程改变其接收和发送极性for transmitter and receiver•边沿触发接收唤醒•支持LIN总线的间隔检测和传输冲突检测1.3.12 Serial Peripheral Interface Module (SPI) •可配置8- or 16-bit 数据大小•全双工或单线双向•全双工接收和发送• Master or slave 模式•最高位优先or 最低位优先可换• 并口时钟频率相位和极性选择1.3.13 AD转换(ATD)• 10通道12位AD转换器— 3微妙转换时间— 8-/10-/12-位解决方案5—数据结果左对齐或右对齐—停止模式下使用内部晶振作为转换器晶振—低功耗模式下模拟信号比较唤醒—连续转换模式e—多通道扫描•引脚可作为IO口1.3.14 片内电压调节器(VREG)•具有带隙标准的线性电压稳压器• 具有低电压中断功能的低压检测器•上电复位(POR) 电路•低电压复位功能(LVR)•高温传感器1.3.15 背景调试(BDM)• 非插入内存访问指令• 支持在线对片内非易始性存储单元编程1.3.16 调试器(DBG)•64个入口跟踪缓冲器• 三个比较器(A, B and C)—比较器A比较全16位地址总线额16位数据总线—精确寻址和寻址范围比较•两种匹配比较类型—标记位—程序强行置位该类型是在一数学公式出现后一个指令边界可用•四个跟踪模式•四个阶段状态序列发生器stage state sequencer1.4 内部结构框图71.5 引脚图1.6 存储器映像表Table 1-2. Device Register Memory Map注意在表1-2中保留的寄存器空间不分配给任何模块,该寄存器的保留空间是留给以后使用的,对这些保留空间写操作没有任何效果,读该空间返回值都为零。

脉冲幅度调制(PAM)及系统实验

CUST 通信工程专业实验室

实验一 脉冲幅度调制(PAM)及系统实验

六、实验内容

1、脉冲幅度调制实验

a 观察被调制信号正弦波形、取样脉冲波形和已调信号波形的相 互之间的关系及特点,特别是音频带内各频率点的情况。(测1个 测量点)

波形的正确画法:

CUST 通信工程专业实验室

实验一 脉冲幅度调制(PAM)及系统实验

八、讨论思考题

1、结合实验简述取样定理 2、记录所看到的TP601的陷幅 波形,并说明其产生原因 3、结合实验计算本组实验箱的 输入信号最高频率

CUST 通信工程专业实验室

实验一 脉冲幅度调制(PAM)及系统实验

CUST 通信工程专业实验室

实验一 脉冲幅度调制(PAM)及系统实验

M() m(t)

t

-H O H

(a)

s(t)

|S()|

A

T

t

(b)

ms(t)

t

(c)

CUST

£ -

2

-2H O2H2源自|Ms()|£ -

2

-2H O

2H

2

通信工程专业实验室

实验一 脉冲幅度调制(PAM)及系统实验

五、实验原理电路图

实验一 脉冲幅度调制(PAM)及系统实验

四、实验原理知识点3: PAM

• PAM是脉冲载波的幅度随基带信号变化的一种调制方式。若脉 冲载波是冲激脉冲序列,则前面讨论的抽样定理就是脉冲振幅调制 的原理。也就是说,按抽样定理进行抽样得到的信号就是一个PAM 信号。

• 但是,用冲激脉冲序列进行抽样是一种理想抽样的情况,是不

pwm调速系统工作原理

pwm调速系统工作原理

PWM调速系统是基于脉宽调制(Pulse Width Modulation)原

理进行的调速系统。

其工作原理如下:

1. 输入信号:首先,系统会接收来自控制器的输入信号,该信号代表了需要调整转速的目标值。

2. 参考信号生成:系统会将输入信号与某个参考信号进行比较,生成一个误差信号。

这个参考信号可以是一个固定频率的方波信号。

3. 比较器:误差信号会被送入一个比较器中,与一个可调的正弦波或三角波信号进行比较。

4. 脉冲调制:比较器的输出信号会传递给脉冲调制器,通过调整它的输入信号的占空比,可以得到一个与误差信号幅度成正比的脉冲宽度。

5. 脉冲产生:脉冲调制器会产生一串脉冲信号,其宽度与误差信号的幅度成比例。

脉冲信号的频率通常为固定值,而占空比会随误差信号变化。

6. 控制信号输出:脉冲信号会被传递到一个功率放大器,然后经过滤波器去除高频噪声。

最后,滤波后的信号会被转换为适合电机的控制信号,用于调整电机的转速。

通过以上工作原理,PWM调速系统可以实现精确的转速控制,

可以应用于各种需要调速的设备和系统,如电机驱动、照明控制等。

脉冲输出指令库用法

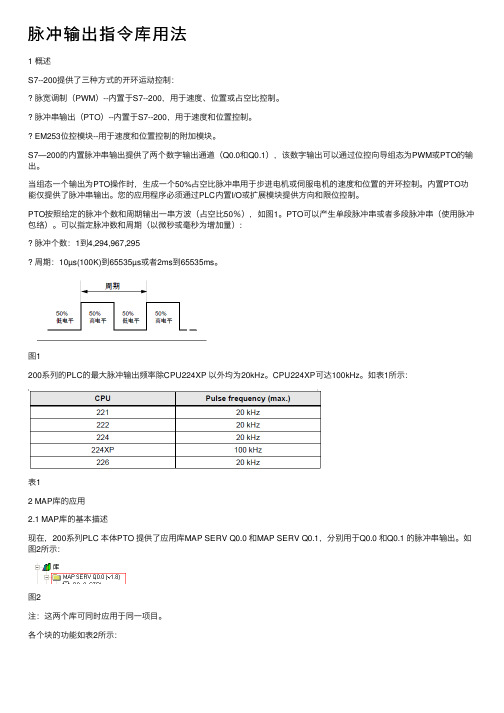

脉冲输出指令库⽤法1 概述S7--200提供了三种⽅式的开环运动控制:脉宽调制(PWM)--内置于S7--200,⽤于速度、位置或占空⽐控制。

脉冲串输出(PTO)--内置于S7--200,⽤于速度和位置控制。

EM253位控模块--⽤于速度和位置控制的附加模块。

S7—200的内置脉冲串输出提供了两个数字输出通道(Q0.0和Q0.1),该数字输出可以通过位控向导组态为PWM或PTO的输出。

当组态⼀个输出为PTO操作时,⽣成⼀个50%占空⽐脉冲串⽤于步进电机或伺服电机的速度和位置的开环控制。

内置PTO功能仅提供了脉冲串输出。

您的应⽤程序必须通过PLC内置I/O或扩展模块提供⽅向和限位控制。

PTO按照给定的脉冲个数和周期输出⼀串⽅波(占空⽐50%),如图1。

PTO可以产⽣单段脉冲串或者多段脉冲串(使⽤脉冲包络)。

可以指定脉冲数和周期(以微秒或毫秒为增加量):脉冲个数:1到4,294,967,295周期:10µs(100K)到65535µs或者2ms到65535ms。

图1200系列的PLC的最⼤脉冲输出频率除CPU224XP 以外均为20kHz。

CPU224XP可达100kHz。

如表1所⽰:表12 MAP库的应⽤2.1 MAP库的基本描述现在,200系列PLC 本体PTO 提供了应⽤库MAP SERV Q0.0 和MAP SERV Q0.1,分别⽤于Q0.0 和Q0.1 的脉冲串输出。

如图2所⽰:图2注:这两个库可同时应⽤于同⼀项⽬。

各个块的功能如表2所⽰:表2总体描述该功能块可驱动线性轴。

为了很好的应⽤该库,需要在运动轨迹上添加三个限位开关,如图3:⼀个参考点接近开关(home),⽤于定义绝对位置C_Pos 的零点。

两个边界限位开关,⼀个是正向限位开关(Fwd_Limit),⼀个是反向限位开关(Rev_Limit)。

绝对位置 C_Pos 的计数值格式为DINT ,所以其计数范围为(-2.147.483.648 to +2.147.483.647).如果⼀个限位开关被运动物件触碰,则该运动物件会减速停⽌,因此,限位开关的安置位置应当留出⾜够的裕量 ΔSmin 以避免物件滑出轨道尽头。

伺服电机总线和脉冲分类_解释说明以及概述

伺服电机总线和脉冲分类解释说明以及概述1. 引言1.1 概述在现代工业自动化领域,伺服电机作为一种关键的执行器,广泛应用于各种机械设备中。

而要使伺服电机能够准确、高效地控制运动,在实际应用中需要借助于一个特定的通信协议或控制方式来实现。

其中,伺服电机总线和脉冲控制是两种常见且重要的控制方式。

1.2 文章结构本文将对伺服电机总线和脉冲分类进行详细阐述和解释,并对二者之间的联系与区别进行分析。

具体而言,文章将首先介绍伺服电机总线的定义和基本原理,然后列举并分析常见的伺服电机总线类型以及它们各自的优缺点与应用场景。

接着,文章将深入解释脉冲分类原理,并比较开环与闭环控制这两种不同方式在实际应用中的差异。

最后,本文将讨论伺服电机总线和脉冲控制之间的联系与区别,并对它们在工业自动化中的应用场景进行比较分析。

文章最后将给出未来发展趋势和展望。

1.3 目的本文旨在帮助读者深入理解伺服电机总线和脉冲分类的知识,了解它们在工业自动化领域中的应用和作用。

通过对伺服电机总线和脉冲控制的详细解释和比较,读者将能够清晰地认识到这两种控制方式的优缺点,并在实际应用场景中选择适合自己需求的控制方案。

最后,本文还将给出未来发展方向的启示和建议,为读者提供指导和思路。

2. 伺服电机总线分类:2.1 定义与基本原理:伺服电机总线是指用于连接控制器和伺服电机的数据传输线路。

通过该总线,控制器可以向伺服电机发送指令并接收状态反馈信息,实现对伺服电机的精确控制。

其基本原理是通过特定的通信协议将控制信号传输到伺服电机,并从伺服驱动器中获取位置、速度、力矩等反馈信息。

2.2 常见的伺服电机总线类型:目前市场上常见的伺服电机总线类型主要包括以下几种:a) CAN总线:CAN(Controller Area Network)总线是一种高可靠性、实时性较好的串行通信总线,广泛应用于工业领域。

它具有较高的抗干扰能力和扩展性,并支持多设备之间的通信。

b) EtherCAT:EtherCAT(Ethernet for Control Automation Technology)是一种基于以太网技术的开放式实时以太网通信协议。

PWM基本原理及其实现方法

PWM基本原理及其实现方法PWM(脉宽调制)是一种常用的控制电子设备的方法,通过调整电信号的脉冲宽度来控制电信号的平均功率。

PWM的基本原理是通过改变信号的占空比来实现对设备的控制。

PWM实现的基本步骤是:先产生一个固定频率的正弦波信号(一般采用震荡器或定时器),然后通过比较器对正弦波信号与参考电平进行比较,根据比较结果来产生脉冲信号。

具体来说,PWM的实现方法有以下几种:1. 单脉冲宽度调制(Single Pulse Width Modulation):这种方法是最简单直接的方式,通过控制脉冲信号的宽度来实现对设备的控制。

宽度越大,输出功率越大,宽度越小,输出功率越小。

2. 多脉冲宽度调制(Multiple Pulse Width Modulation):该方法是在单脉冲宽度调制的基础上,引入多个脉冲,通过调整各个脉冲的宽度和间隔,实现更精细的控制。

例如,可以通过改变每个脉冲的宽度来实现设备的加速和减速。

3. 脉冲位置调制(Pulse Position Modulation):与脉冲宽度调制不同,该方法是通过改变脉冲信号的位置来控制设备的平均功率。

脉冲信号的位置决定了信号的相位,从而控制了输出功率。

4. 脉冲频率调制(Pulse Frequency Modulation):该方法是通过改变脉冲信号的频率来控制设备的平均功率。

频率越高,平均功率越高,频率越低,平均功率越低。

以上四种方法都是基于对脉冲信号的宽度、位置或频率进行调制,从而实现对设备的控制。

这些方法广泛应用于各种电子设备的控制,例如模拟调制器、电机速度控制器、灯光调光器等。

总结起来,PWM通过改变脉冲信号的宽度、位置或频率来实现对设备的平均功率控制。

根据需求不同,可以选择不同的PWM实现方法。

由于PWM具有高效、精度高的特点,所以被广泛应用于各种电子设备的控制中。

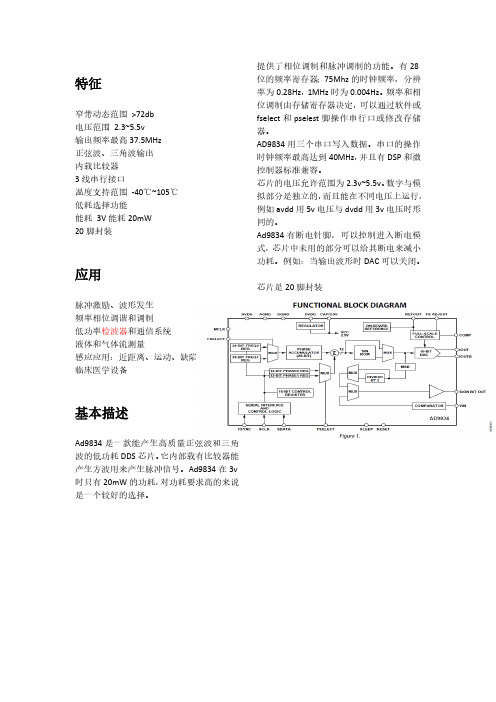

AD9834调制和脉冲调制介绍

特征窄带动态范围>72db电压范围 2.3~5.5v输出频率最高37.5MHz正弦波、三角波输出内载比较器3线串行接口温度支持范围-40℃~105℃低耗选择功能能耗3V能耗20mW20脚封装应用脉冲激励、波形发生频率相位调谐和调制低功率检波器和通信系统液体和气体流测量感应应用:近距离、运动、缺陷检波临床医学设备基本描述Ad9834是一款能产生高质量正弦波和三角波的低功耗DDS芯片。

它内部载有比较器能产生方波用来产生脉冲信号。

Ad9834在3v 时只有20mW的功耗,对功耗要求高的来说是一个较好的选择。

提供了相位调制和脉冲调制的功能。

有28位的频率寄存器;75Mhz的时钟频率,分辨率为0.28Hz,1MHz时为0.004Hz。

频率和相位调制由存储寄存器决定,可以通过软件或fselect和pselest脚操作串行口或修改存储器。

AD9834用三个串口写入数据。

串口的操作时钟频率最高达到40MHz,并且有DSP和微控制器标准兼容。

芯片的电压允许范围为2.3v~5.5v。

数字与模拟部分是独立的,而且能在不同电压上运行,例如avdd用5v电压与dvdd用3v电压时形同的。

Ad9834有断电针脚,可以控制进入断电模式,芯片中未用的部分可以给其断电来减小功耗。

例如:当输出波形时DAC可以关闭。

芯片是20脚封装目录特点 (1)应用 (1)概述 (1)原理框图 (1)修订 (3)说明 (4)时序参数 (6)各最大额定值 (7)防静电警告 (7)内部结构和功能描述 (8)典型表现值 (10)专业术语解释 (14)操作原理 (15)电路描述 (16)数控振荡器正相调制 (16)Sin rom (16)DA转换 (16)比较器 (16)校时器 (17)输出电压一致性 (17)功能描述 (18)串行接口 (18)AD9834带电特性 (18)时序周期。

18 修订(略)控制寄存器。

18频率和香味寄存器。

20写入频率寄存器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

位置比较脉冲调制输出在Turbo PMAC 系统中PMAC2型伺服IC 有自动脉冲宽度调制(PWM )和脉冲频率调制(PFM )两种电路。

有些情况下,这些也不能提供所需要的频率和/或脉冲宽度范围。

然而,对于一个备用的编码器通道,它可能使用位置比较输出的自动增加功能得到一个灵活的脉冲宽度或脉冲频率调制信号。

这个技术使用通道内部的PFM 电路,以固定比率增加通道编码器的计数。

然后,通过调整A 和B 比较寄存器之间的距离,我们可以控制脉冲宽度,通过调整自动增加的值,我们可以控制脉冲频率。

分析计数器频率是时钟频率的一个简单函数,这个时钟频率就是PFM 电路的时钟频率(PFMCLK )并且这个指令值在PFM 寄存器里。

默认的9.8304 MHz PFMCLK 频率几乎适合大多数应用。

等式需要16位的PFM 指令值(使用24位字的高16位,与标准的M-变量定义一样)得到一个指定的计数器频率是:PFMCLKcounter PFM f f C *216= 如果希望写整个的24位PFM 指令寄存器,比如在MACRO 站点,仅将以上等式中的216用224替代。

比较电路的输出频率是计数器频率和比较电路自动增加位置值的函数。

根据给定的输出频率得到需要的自动增加值的等式是:outputcounter comp f f P =∆ 比较输出的占空比是A 和B 比较寄存器之间的距离和自动增加值的比例。

根据给定的占空比(表示成百分比)和自动增加值得到这个距离的等式是:100%DutyCycle P AB comp comp ∆=∆ 注意的是当写A 和B 比较寄存器时,它们必须是在当前计数值的两侧;否则自动增加功能将不能正确工作。

简单设置和编程以下的设置和程序部分可以用于实现这个功能。

在这个示例中,我们设置一个计数器频率是500kHz ,它给我们一个占空比1%的分辨率或比较好的5kHz 的脉冲频率。

注意的是实现一个特定脉冲配置的指令可以在一个运动程序或一个PLC 程序里执行;它们甚至可以作为在线指令发送。

通常它们将被嵌入到一个运动子程序的传递参数。

; 设置和定义I7203=2258 ; IC2的默认时钟频率I7204=2 ; IC2的PFM脉冲宽度I7210=8 ; IC2通道1内部仿真I7216=3 ; IC2通道1的AB为DAC输出C为PFM输出#define ServoCycCtr M100 ; 每个伺服周期的增量ServoCycCtr->X:$0,0,24,S#define SIC2Ch1EncPos M101 ; 当前计数器值SIC2Ch1EncPos->X:$078201,0,24,S#define SIC2Ch1OutC M107 ; C寄存器PFM输出SIC2Ch1OutC->Y:$078204,8,16,S ; 定义寄存器高16位#define SIC2Ch1CompPosA M108 ; 比较A寄存器SIC2Ch1CompPosA->Y:$078207,0,24,S#define SIC2Ch1CompPosB M109 ; 比较B寄存器SIC2Ch1CompPosB->X:$078207,0,24,S#define SIC2Ch1CompIncr M110 ; 比较自动增加SIC2Ch1CompIncr->X:$078206,0,24,S#define SIC2Ch1CompInitSta M111 ; 比较初始状态SIC2Ch1CompInitSta->Y:$078205,11#define SIC2Ch1CompInitEna M112 ; 比较初始化使能SIC2Ch1CompInitEna->Y:$078205,12#define Now P106 ; 当前伺服计数器#define CounterFreq P107 ; 计数频率为Hz#define PulseFreq P108 ; 输出频率为Hz#define DutyCycle P109 ; %接通时间(0 – 100)CounterFreq=500000 ; 计数频率,常数; 用指令来实现特定的频率和占空比,这些可以在运动程序,PLC程序,或作为一个在; 线指令(包括WHILE/ENDWHILE,不能以任何方式作为在线指令使用)SIC2Ch1OutC=0 ; 冻结计数器用于设置Now=ServoCycCtr ; 记录当前时间WHILE (ServoCycCtr=Now) ; 为冻结提供延时ENDWHILESIC2Ch1CompInitSta=0 ; 设置输出关闭SIC2Ch1CompInitEna=1 ; 强制初始的输出状态SIC2Ch1CompIncr=InternalFreq/PulseFreq ; 设置输出频率SIC2Ch1CompPosA=SIC2Ch1EncPos+SIC2Ch1CompIncr*(100-DutyCycle)/200 SIC2Ch1CompPosB=SIC2Ch1EncPos-SIC2Ch1CompIncr*(100-DutyCycle)/200 SIC2Ch1OutC=CounterFreq*65536/98304000 ; 输出频率的PFM值选通输出通过设置通道n的I7mn1等于1,同一块IC上的其余的编码器比较电路可以设置为只作用于IC上的第一个编码器。

如果任何的这些电路被分配到第一个通道的编码器,第一个通道的比较输出是所有被分配给它的比较电路的逻辑或(如果任何一个电路是“1”状态,输出就是1)。

这个可以用于选通第一个比较输出。

在这一节,我们使用第二个比较输出的“内部状态”写功能控制第一个比较输出是否一直打开,或输出一个频率。

; 额外设置和定义I7221=1 ; IC2通道2的比较使用编码器1#define SIC2Ch2CompInitSta M211 ; 比较的初始状态SIC2Ch2CompInitSta->Y:$07820D,11#define SIC2Ch2CompInitEna M212 ; 比较初始化使能SIC2Ch2CompInitEna->Y:$07820D,12; 命令输出一直打开SIC2Ch2CompInitSta=1SIC2Ch2CompInitEna=1; 命令第一个比较电路驱动输出SIC2Ch2CompInitSta=0SIC2Ch2CompInitEna=1Position-Compare Pulse-Modulated OutputThe PMAC2-style Servo ICs in Turbo PMAC systems have both automatic pulse-width-modulation (PWM) and pulse-frequency modulation (PFM) circuits. There are some cases in which neither of these can provide the required range of frequencies and/or pulse widths.However, with a spare encoder channel, it is possible to use the position-compare output with its “auto-increment” feature to get a very flexible pulse-width or pulse-frequency modulated signal. This technique uses the channel’s PFM circuit internally to increment the channel’s encoder counter at a fixed rate. Then, by adjusting the distance between the “A” and “B” compare registers, we can control the pulse width, and by adjusting the “auto-increment” value, we can control the pulse frequency.AnalysisThe counter frequency is simply a function of the clock frequency for the PFM circuit’s clock frequency (“PFMCLK”) and the command value in the PFM register. The default PFMCLK frequency of 9.8304 MHz is almost always suitable. The equation for the required 16-bit PFM command value (using the high 16 bits of the 24-bit word, as with the standard M-variable definition) to get a specified counter frequency is:PFMCLKcounter PFM f f C *216= If you want to write to the entire 24-bit PFM command register, as in the MACRO Station, just substitute 224 for 216 in the above equation.The output frequency from the compare circuit is a function of the counter frequency and the compare circuit’s auto-increment position value. The equation for the required auto-increment value to obtain a given output frequency is:outputcounter comp f f P =∆ The duty cycle of the compare output is the ratio of the distance between the “A” and “B”compare registers and the auto-increment value. The equation for this distance for a given duty cycle (expressed as a percent) and auto-increment value is:100%DutyCycle P AB comp comp ∆=∆ Note that when writing to the “A” and “B” compare registers, they must be on opposite sides of the present counter value; otherwise the auto-increment feature will not work properly.Sample Setup and ProgramThe following setup and program section can be used to implement this functionality. In this example, we set up a counter frequency of 500 kHz, which gives us a duty cycle resolution of 1% or better at pulse frequencies up to 5 kHz.Note that the commands that implement a particular pulse configuration can be implemented in either a motion program or a PLC program; they could even be sent as on-line commands. Commonly they would be embedded in a motion program subroutine with passed arguments.; Setup and definitionsI7203=2258 ; IC2 default clock frequencies I7204=2 ; IC2 PFM pulse widthI7210=8 ; IC2 Ch1 internal pulse decode I7216=3 ; IC2 Ch1 AB DAC C PFM output#define ServoCycCtr M100 ; Increments each servo cycle ServoCycCtr->X:$0,0,24,S#define SIC2Ch1EncPos M101 ; Present counter valueSIC2Ch1EncPos->X:$078201,0,24,S#define SIC2Ch1OutC M107 ; C PFM output registerSIC2Ch1OutC->Y:$078204,8,16,S ; Define as high 16 bits#define SIC2Ch1CompPosA M108 ; Compare A registerSIC2Ch1CompPosA->Y:$078207,0,24,S#define SIC2Ch1CompPosB M109 ; Compare B registerSIC2Ch1CompPosB->X:$078207,0,24,S#define SIC2Ch1CompIncr M110 ; Compare auto-incrementSIC2Ch1CompIncr->X:$078206,0,24,S#define SIC2Ch1CompInitSta M111 ; Compare initial stateSIC2Ch1CompInitSta->Y:$078205,11#define SIC2Ch1CompInitEna M112 ; Compare initialize enableSIC2Ch1CompInitEna->Y:$078205,12#define Now P106 ; Present servo counter#define CounterFreq P107 ; Counter freq in Hz#define PulseFreq P108 ; Output freq in Hz#define DutyCycle P109 ; % on-time (0 – 100)CounterFreq=500000 ; Counter freq, constant for app ; Commands to implement particular frequency and duty cycle; These could be in motion program, PLC program, or as on-line; commands (except for the WHILE/ENDWHILE, which would not be; needed anyway in on-line commands)SIC2Ch1OutC=0 ; Freeze counter for setupNow=ServoCycCtr ; Log present timeWHILE (ServoCycCtr=Now) ; Provide delay for freeze ENDWHILESIC2Ch1CompInitSta=0 ; Set for output offSIC2Ch1CompInitEna=1 ; Force initial output stateSIC2Ch1CompIncr=InternalFreq/PulseFreq ; Set for out freqSIC2Ch1CompPosA=SIC2Ch1EncPos+SIC2Ch1CompIncr*(100-DutyCycle)/200 SIC2Ch1CompPosB=SIC2Ch1EncPos-SIC2Ch1CompIncr*(100-DutyCycle)/200 SIC2Ch1OutC=CounterFreq*65536/98304000 ; PFM value for freqGating the OutputThe compare circuits for subsequent encoders on the same IC can be set up to act on the first encoder on the IC by setting I7mn1 for Channel n to 1. If any of these circuits is assigned to the first channel’s encoder, the first channel’s compare output is the logical OR of all of the compare circuits assigned to it (if any of the circuits are in a “1” state, the output is 1). This can be used to “gate” the first compare output. In this section, we use the “initial-state” write feature of the second compare output to control whether the first compare output is always on, or outputting a frequency.; Additional setup and definitionsI7221=1 ; IC2 Ch2 compare use Enc1#define SIC2Ch2CompInitSta M211 ; Compare initial stateSIC2Ch2CompInitSta->Y:$07820D,11#define SIC2Ch2CompInitEna M212 ; Compare initialize enableSIC2Ch2CompInitEna->Y:$07820D,12; Commands to force output always onSIC2Ch2CompInitSta=1SIC2Ch2CompInitEna=1; Commands to let first compare circuit drive outputSIC2Ch2CompInitSta=0SIC2Ch2CompInitEna=1。