锁相环路参数测试

锁相调频电路实验

锁相调频电路实验实验六锁相调频电路实验一、实验目的1、进一步了解锁相环路的工作原理及性能特点。

2、初步熟悉锁相环路及其基本组成的部件性能指示的测试方法。

二、实验原理1、我们知道锁相环路由鉴相器(Phase Detector)环路滤波器(Loop Fifter)和压控振荡器(voltage control oscillator)三个基本部分组成。

锁相环路实际上是一个相位自动调节系统(ω≠ωR)进入锁定状态ωV=ωR的捕捉过程,与环路保持锁定状态的同步和跟踪过程。

锁相环锁定和失锁的基本标志是:锁定时ω=ωV,△ω=0鉴相器输出一直流电压Vd可以用直流电压表测出,也可以用示波器观察。

失锁时,ω≠ωV鉴相器输出一个交变的交流电压,用直流电压表测量时,其Vd为零,用示波器观察则Vd为交变的交流信号电压,鉴相器的鉴相灵敏度,VCO的控制特性,环路滤波器的滤波性能等参数都对锁相环的性能有很大的影响。

同步过程:起始条件是环路已处于动态平衡中由于不稳定因素的影响,使ωV 产生缓慢漂移时,环路内所发生的使ωV继续锁定在ωR 上的过程,同步过程的进行受一定的限制当起始频差δωV达到一定值时,环路是不能再锁定而失锁,这一边界ΔωH成为同步带。

捕捉过程:起始条件是环路失锁既ωR≠ωV的情况下,环路由失锁进入锁定时环路内所发生的运动过程。

捕捉过程分为快捕和慢捕,通常所指为快捕过程。

捕捉带,它是指环路失锁已既进入锁定的两个边界频率之差的1/2。

2、实验电路介绍实验电路如图6—1所示:限幅器:对输入的方波信号进行整形,消除毛刺、寄生调幅。

用7LS00与非门来完成。

鉴相器:比较两个信号的相位产生与相位差成下比例的电压、它也利用与非门来完成。

(74LS00)74LS00是二输入端四与非门。

图6—1 锁相环路实验电路方框图滤波器:选出反映相位差的直流分量去控制VCO,本滤波器为比例滤波器。

放大器:由LM741组成的基极定时多谢振荡器,它的振荡频率相位受到控制得以调整输出反馈到鉴相器。

锁相环路参数测试

测相位比较器的鉴相灵敏度Kd

fr △ U(v)

此表格在SW404开关1、7处测一组数据,实验报告要求 画出相位比较器特性图(鉴相灵敏度),如图1坐标 。 简便方法:用测同步带的方法测试.先测频率、相位差纪 录下数据后,再测相应频率和电压。

测VCO压控振荡器的灵敏度KO

在实验报告用表中数据画出压控特性图如图2坐标。

• 观察环路的锁定情况 1、测试条件:k402置“1” ,N分频器置001,8位开关的4,7位置on 时,环路的工作情况,打开直流电源。 2、先找到环路的锁定频率点,将INPUT端的输入信号去掉,测出压控 振荡器的自然振荡频率,使信号源的输出频率等于该频率,并将其接 到INPUT端,此时环路为锁定状态,用示波器观察有:

实验电路图

测同步带和捕捉带 同步带测试:

在环路锁定状态下,改 变信号源频率 f r ,使环路保 持锁定时,找到最大fH、最小 fL锁定频率点,计入表中。

捕捉带测试:

在环路处于失锁状态下,

改变信号源频率 f r,分别找到 环路捕捉到的最大fH’、最小fL’ 锁定点的频率,计入表中。

锁相环实验报告

锁相环实验报告引言在电子、通信和控制系统中,锁相环(Phase-Locked Loop,PLL)是一种广泛应用的反馈控制系统,用于提供稳定的频率和相位锁定。

本实验旨在探究锁相环的原理、结构和性能,并通过实际实验验证其工作原理。

锁相环原理锁相环是一种负反馈控制系统,通常由相频控振荡器(VCO)、相锁环比较器、波形整形电路和滤波器组成。

其基本原理是:通过不断调节VCO的频率,使其输出信号与参考信号的相位差保持在一个稳定的工作范围内。

实验目的1.了解锁相环的基本原理和结构;2.学习锁相环在频率和相位锁定中的应用;3.通过实际实验验证锁相环的工作原理。

实验器材1.锁相环实验台;2.函数信号发生器;3.示波器;4.电压表;5.连接线等。

实验步骤搭建实验平台1.将锁相环实验台与函数信号发生器、示波器和电压表连接;2.正确接入电源,打开锁相环实验台的电源开关; 3.确认各仪器仪表的正常工作。

设置参考信号1.使用函数信号发生器产生一个正弦波信号作为参考信号;2.设置参考信号的频率和幅度。

调节锁相环参数1.调节锁相环的增益参数,观察VCO输出信号的变化;2.尝试不同的锁相环参数组合,观察系统的稳定性和响应性。

改变输入信号1.改变函数信号发生器输出信号的频率;2.观察锁相环的相位锁定和频率锁定过程。

测量锁相环性能1.使用示波器观察锁相环输入信号、输出信号和参考信号的波形;2.使用电压表测量VCO输出信号的频率。

实验结果与分析通过实验我们可以观察到锁相环的工作原理和性能。

在不同的锁相环参数设置下,VCO输出信号的频率和相位与参考信号的变化情况不同。

根据实验数据,我们可以分析锁相环的稳定性、响应速度和抗干扰能力等性能。

结论锁相环是一种广泛应用于电子、通信和控制系统中的反馈控制系统。

通过本实验,我们深入了解了锁相环的原理和结构,并通过实际实验验证了其工作原理。

锁相环具有稳定的频率和相位锁定能力,可以在信号处理和调节控制中起到重要作用。

锁相实验指导内容

实验一 锁相环单元实验一、实验目的1、掌握通用单片集成锁相环LM565的工作原理和应用。

2、了解锁相环LM565参数的计算方法。

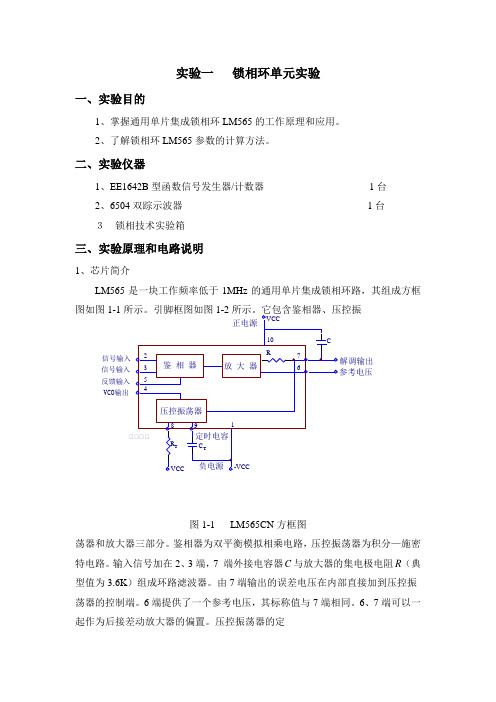

二、实验仪器1、EE1642B 型函数信号发生器/计数器 1台2、6504双踪示波器 1台 3 锁相技术实验箱三、实验原理和电路说明1、芯片简介LM565是一块工作频率低于1MHz 的通用单片集成锁相环路,其组成方框图如图1-1图1-1 LM565CN 方框图荡器和放大器三部分。

鉴相器为双平衡模拟相乘电路,压控振荡器为积分—施密特电路。

输入信号加在2、3端,7 端外接电容器C 与放大器的集电极电阻R (典型值为3.6K )组成环路滤波器。

由7端输出的误差电压在内部直接加到压控振荡器的控制端。

6端提供了一个参考电压,其标称值与7端相同。

6、7端可以一起作为后接差动放大器的偏置。

压控振荡器的定¸¸¸¸¸¸¸¸VCO¸¸¸·¸¸¸¸¸¸¸¸¸÷¸¸图1-2 LM565CN 引脚图时电阻T R 接在8端,定时电容T C 接在9端,振荡信号从4端输出。

压控振荡器的输出端4与鉴相器反馈输入端5是断开的,允许插入分频器来做频率合成器。

对LM565而言,压控振荡器振荡频率可近似表示为:TT C R f 42.1≈压控灵敏度为 :C E f K 500=式中C E 是电源电压(双向馈电时则为总电压)。

鉴相灵敏度为:π4.1=d K放大器增益为 :4.1=ALM565工作频率范围为0.001Hz~500KHz ,电源电压为±6~±12V ,鉴频失真低于0.2%,最大锁定范围为±60%f ,输入电阻为10K ,典型工作电流为8mA 。

锁相环原理与应用实验

厦门大学电子工程系课程设计说明书题目___锁相环原理与应用实验_______专业_______通信工程___________学生姓名陈杨龙2011年7 月21 日一、实验原理一、锁相环基本组成一个典型的锁相环(PLL )系统,是由鉴相器(PD ),压控荡器(VCO )和低通滤波器(LPF )三个基本电路组成Ud = Kd (θi –θo) UF = Ud F (s )P DL PFV COU iU o二.鉴相器(PD ) Ud = Kd *∆θ Kd 为鉴相灵敏度三.压控振荡器(VCO ) (P2) ωo (t )= ωom + K 0 U F (t )K 0——VCO 控制特性曲线的斜率,常称为VCO 的控制灵敏度,或称压控灵敏度。

四、环路滤波器这里仅讨论无源比例积分滤波器 其传递函数为:式中:τ 1 = R1 Cτ 2 = R2 CR 1R 2CU iU o五、锁相环的同步和捕捉:同步状态:锁相环的输出频率(或VCO 的频率)ωo 能跟踪输入频率ωi 的工作状态,称为同步状态(或锁定状态)。

同步带:在锁相环保持同步的条件下,输入频率ωi 的最大变化范围,称为同步带宽,用∆ωH 表示。

超出此范围,环路则失锁。

捕捉带:失锁时,ωo ≠ωi ,如果从两个方向设法改变ωi ,使ωi 向ωo 靠拢,进而使∆ωo =(ωi -ωo )↓,当∆ωo 小到某一数值时,环路则从失锁进入锁定状态。

F O oU K dtd =θ1)(1)()()(212+++==τττs s s U s U s K i O F二、实验内容实验一、PLL 参数测试一、压控灵敏度K O 的测量123456789101112131415169V9V 10K1M1n1K10K 4046数字电压表频率计当V(9)=4.5时,中心频率f o =74.354KHZ二、同步带,捕捉带的测量实验中测出:f HH =127.29KHZ ,f HL =2.78KHZ ,f PH =93.81KHZ ,f PL =51.77KHZ由此可算得:ΔfH =127.29-2.78=124.51KHE , ΔfH =93.81-51.77=42.04KHZ 。

实验五锁相环测试及应用实验报告

:锁相环测试及应用实验试验目的:1.了解锁相环的组成、基本原理及性能特点。

2.掌握集成锁相环4046芯片的使用方法。

3.掌握锁相环路及各部件性能(鉴相特性、压控特性、同步带和捕捉带)的测试方法。

4.掌握锁相调频、锁相鉴频电路的构成、基本原理及参数测试测试方法。

5.掌握简单锁相频率合成器的基本原理及性能指标的测试方法实验设备:1.调幅与调频发射模块。

2.直流稳压电压GPD-3303D3.F20A 型数字合成函数发生器/计数器 4.DSO-X 2014A 数字存储示波器实验原理:1. 锁相环的组成及基本原理锁相环路(PLL )亦称自动相位控制(APC )电路,它是一种利用相位误差消除频率误差的反馈控制系统。

如图1所示,由鉴相器(相位比较器)、环路滤波器(低通滤波器)和压控振荡器三个基本部件组成。

若o i f f ≠,瞬时相位差ϕ∆将随时间而变化;若i of f ϕ∆=保持固定值。

锁相环就是利用两个信号之间相位差的变化,控制压控振荡器的输出信号频率,最终使两个信号相位差保持为常数,达到频率相等。

锁相环的工作过程:如图1所示,若o i f f ≠,必将引起ϕ∆的变化,鉴相器输出正比于ϕ∆的误差电压()d u t 。

经环路滤波器滤除()d u t 中的高频分量和噪声,产生缓慢变动的直流电压()c u t 。

VCO 受控于()c u t ,使得振荡频率o f 与输入参考频率i f 的频差逐渐减小,直到o i f f =,电路达到稳定平衡状态,即锁定状态。

此时,ϕ∆保持一个不变的稳态相差ϕ∞,以维持电路的平衡状态。

需要指出,环路能达到锁定状态,是在o f 与i f 相差不大的范围内。

2. 几个重要概念 ⑴ 失锁与锁定开始工作时, o i f f ≠,ϕ∆不固定,环路处于不稳定状态,称为失锁。

当o i f f =时,ϕ∆保持常数,电路进入稳定状态,称为锁定。

⑵ 跟踪过程与捕捉过程在环路锁定状态下,如果输入信号频率i f 发生变化,环路通过自身的调节作用,使输出信号频率o f 以同样的规律跟随着变化,并且始终保持o i f f =,这个过程称为跟踪过程或同步过程。

模拟锁相环实验

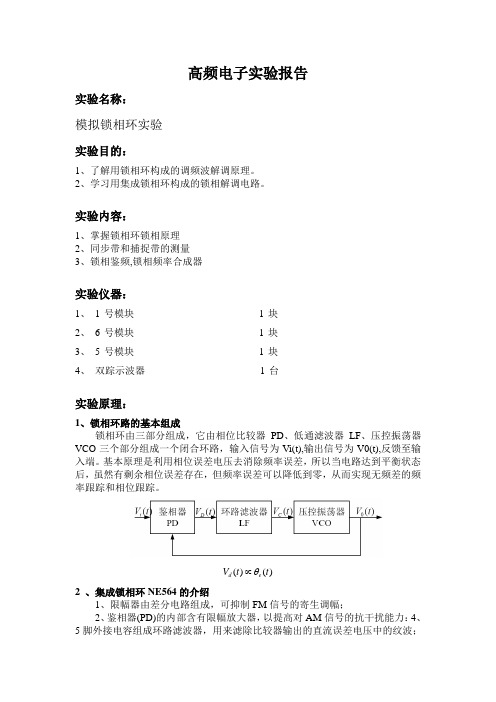

高频电子实验报告实验名称:模拟锁相环实验实验目的:1、了解用锁相环构成的调频波解调原理。

2、学习用集成锁相环构成的锁相解调电路。

实验内容:1、掌握锁相环锁相原理2、同步带和捕捉带的测量3、锁相鉴频,锁相频率合成器实验仪器:1、 1 号模块 1 块2、 6 号模块 1 块3、 5 号模块 1 块4、 双踪示波器 1 台实验原理:1、锁相环路的基本组成锁相环由三部分组成,它由相位比较器PD 、低通滤波器LF 、压控振荡器VCO 三个部分组成一个闭合环路,输入信号为Vi(t),输出信号为V0(t),反馈至输入端。

基本原理是利用相位误差电压去消除频率误差,所以当电路达到平衡状态后,虽然有剩余相位误差存在,但频率误差可以降低到零,从而实现无频差的频率跟踪和相位跟踪。

)()(t t V e d θ∝2 、集成锁相环NE564的介绍1、限幅器由差分电路组成,可抑制FM 信号的寄生调幅;2、鉴相器(PD)的内部含有限幅放大器,以提高对AM 信号的抗干扰能力:4、5脚外接电容组成环路滤波器,用来滤除比较器输出的直流误差电压中的纹波;2脚用来改变环路的增益;3脚为VCO的反馈输入端;3、VCO是改进型的射极耦合多谐振荡器,有两个电压输出端,9脚输出TTL 电平,11脚输出ECL电平。

VCO内部接有固定电阻,只需外接一个定时电容就可产生振荡;4、施密特触发器的回差电压可通过15脚外接直流电压进行调整,以消除16脚输出信号的相位抖动。

3、电路原理图4、同步带与捕捉带同步带是指从PLL锁定开始,改变输入信号的频率fi (向高或向低两个方向变化),直到PLL失锁(由锁定到失锁),这段频率范围称为同步带。

捕捉带是指锁相环处于一定的固有振荡频率f V,并当输入信号频率fi偏离f V上限值或下限值时,环路还能进入锁定,则称为捕捉带。

测量的方法是从J4输入一个频率接近于VCO自由振荡频率的高频调频信号,先增大载波频率直至环路刚刚失锁,记此时的输入频率为f H1 ,再减小fi ,直到环路刚刚锁定为止,记此时的输入频率为f H2,继续减小fi ,直到环路再一次刚刚失锁为止,记此时的频率为f L1 ,再一次增大fi,直到环路再一次刚刚锁定为止,记此时频率为f L2由以上测试可计算得:同步带为:f H1-f L1捕捉带为:f H2-f L2实验步骤:1、锁相环自由振荡频率的测量将5号板开关S1依次设为“1000”,“0100”,“0010”,“0001”(即选择不同的定时电容)2、同步带和捕捉带的测量设置S2(为0010,即VCO的自由振荡频率为4.5MHz),并连线。

通信电子线路课程设计讲义

通信电子线路课程设计—锁相环的测量与应用一、锁相环的组成及工作原理二、CMOS-CD4046数字锁相环内部电路介绍三、环路参数测量四、锁相环的应用--频率合成器锁相环(Phase lock loop)简称PLL,是广泛应用于广播通讯、自动控制、电子检测等领域内的一种功能部件。

随着电子控制技术,自动化程度的不断提高,锁相环部件的应用得到迅速发展。

目前一种价格比较便宜、功能也比较好的CMOS锁相环CD4046(国产的5G4046)应用比较广泛。

本课程设计的目的是使学生通过实际测量锁相环的参数,熟悉一种集成电路锁相环并通过典型应用——频率合成器来巩固、扩展、深化已学理论知识、培养学生把功能电路应用于工程实践的能力。

一、锁相环的组成与工作原理二、CMOS CD4046数字锁相环内部电路介绍三、环路参数测量3.环路同步带和捕捉带的测量同步带和捕捉带分别测量2次,记录2次的测量值,并计算2次测量的平均值。

4.鉴相器测试在环路锁定情况下测量相位比较器P c I和相位比较器P c II的鉴相特性曲线。

测试方法:在环路同步带内14脚接高频信号源,输入正弦波信号,改变14脚输入信号的频率,从小到大变化。

用示波器分别测试14脚和3脚的电压波形,观察它们之间相位差的变化,同时测出9脚对应的输出电压值。

针对相位比较器P c I和相位比较器P c II分别展开测试,测试数据填入下表,分别作出相位比较器P c I和相位比较器P c II的鉴相特性曲线。

表5-1 鉴相器P c I相位差Δθ(弧度)0V d(V)表5-2 鉴相器P c II相位差Δθ(弧度)0V d(V)5.锁相系统静态测量测试环路在锁定状态时,相位比较器输出的误差电压与输入频率之间的关系。

四、锁相环的应用—频率合成器2122。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验电路图

测同步带和捕捉带 同步带测试:

在环路锁定状态下,改 变信号源频率 f r ,使环路保 持锁定时,找到最大fH、最小 fL锁定频率点,计入表中。

捕捉带测试:

在环路处于失锁状态下,

改变信号源频率 f r,分别找到 环路捕捉到的最大fH’、最小fL’ 锁定点的频率,计入表中。

此表格在SW404(8位)开关处,4、7,1、7分别各测一组数据

实验十七、锁相环路参数测试

• 一、实验目的 • 1、掌握基本锁相环工作原理 • 鉴相器将两个输入信号进行相位比较,鉴相器输出Ud电压 正比于两路输入信号的相位差,环路滤波器得到一个平均 电压Uc, Uc 控制压空振荡器输出频率f0的变化,使鉴相器 的两路输入信号的相位不断减小,直到鉴相器的输出相位 差为0,或为某一固定值即直流,环路锁定,输出频率为f0 • 滤波器:起平滑鉴相器输出电压的作用。 • 压控振荡器:输出频率受电压VC控制的振荡器。 • 可见:锁相环是依据一定的相位差来调整压控振荡器的频 率的,当环路锁定时,鉴相器的输入频率相等,相位差确 定。 • 2、熟悉锁相环的电路组成与工作原理。

• 观察环路的锁定情况 1、测试条件:k402置“1” ,N分频器置001,8位开关的4,7位置on 时,环路的工作情况,打开直流电源。 2、先找到环路的锁定频率点,将INPUT端的输入信号去掉,测出压控 振荡器的自然振荡频率,使信号源的输出频率等于该频率,并将其接 到INPUT端,此时环路为锁定状态,用示波器观察有:

测相位比较器的鉴相灵敏度Kd

fr △ U(v)

此表格在SW404开关1、7处测一组数据,实验报告要求 画出相位比较器特性图(鉴相灵敏度),如图1坐标 。 简便方法:用测同步带的方法测试.先测频率、相位差纪 录下数据后,再测相应频率和电压。

测VCO压控振荡器的灵敏度KO

在实验报告用表中数据画出压控特性图如图2坐标。