建立时间与保持时间

建立时间和保持时间

建立时间和保持时间X 数据∣÷-1 SIr^l<~th~~时钟「tsu:建立时间th:保持时间信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,Setup/Hold time是测试芯片对输入信号和时钟信号之间的时间要求, 也就是它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是芯片本身的特性。

建立时间是指触发器的时钟信号提升沿到来以前,数据稳定不变的时间。

输入信号应提前时钟提升沿(如提升沿有效)T时间到达芯片,这个T就是建立时间Setup time.如不满意Setup time,这个数据就不能被这一时钟打入触发器, 只有在下一个时钟提升沿,数据才能被打入触发器;保持时间是指触发器的时钟信号提升沿到来以后,数据也必需保持一段时间,数据保持不变以便能够稳定读取(信号在器件内部通过连线和规律单元时,都有行定的延时。

延时的大小与连线的长短和规律单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。

信号的凹凸电平转换也需要肯定的过渡时间假如hold time 不够,数据便不能被有效读取并转换为输出。

假如数据信号在时钟边沿触发前后持续的时间分别超过建立时间和保持时间,那么这部分超过的重量分别称为建立时间裕量和保持时间裕量。

(这期间其实还涉及到竞争冒险的问题,也就是毛刺,稍后在讨论,建立保持时间的存在即是触发器内部的特性又在屏蔽毛刺方面起到了肯定的作用。

)其实建立时间就是在脉冲信号到来时,输入信号已经稳定等待的时间;而保持时间是信号脉冲到来后,而输入信号还没有到达下降沿的时间。

举个例子:建立时间就是你到伴侣家做客去早了,但是仆人还没回来,你等待的时间就是建立时间;保持时间就是进入房子后,逗留的(有效)时间。

当然在实际测试中我发觉时钟信号也是存在抖动和偏移的。

虽然系统时序设计中对时钟信号的要求特别严格,由于我们全部的时序计算都是以恒定的时钟信号为基准。

关于setup time和hold time的区别

关于setup time和hold time2007-10-07 18:58建立时间:决定了触发器之间的组合逻辑的最大延迟保持时间:决定了触发器之间的组合逻辑的最小延迟只有满足了这两个条件触发器的值才会和你希望的一样建立时间:触发器在时钟沿来到前,其数据输入端的数据必须保持不变的时间;保持时间:触发器在时钟沿来到后,其数据输入端的数据必须保持不变的时间因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。

这就是为什么要用两级触发器来同步异步输入信号。

这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。

同步器有效的条件:第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 < = 时钟周期。

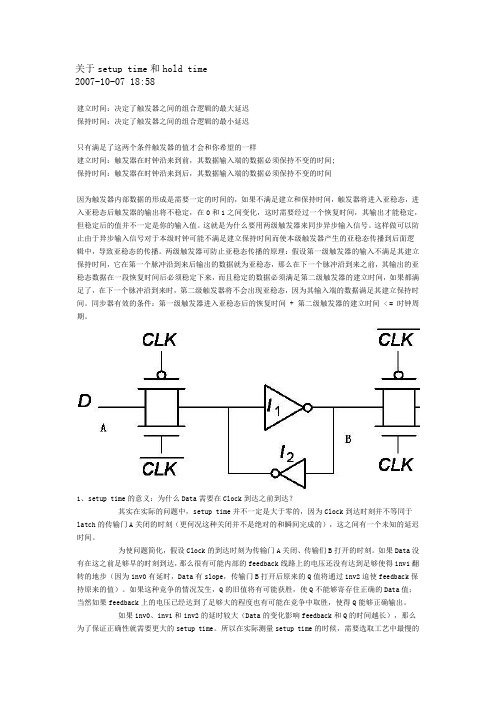

1、setup time的意义:为什么Data需要在Clock到达之前到达?其实在实际的问题中,setup time并不一定是大于零的,因为Clock到达时刻并不等同于latch 的传输门A关闭的时刻(更何况这种关闭并不是绝对的和瞬间完成的),这之间有一个未知的延迟时间。

为使问题简化,假设Clock的到达时刻为传输门A关闭、传输们B打开的时刻。

如果Data没有在这之前足够早的时刻到达,那么很有可能内部的feedback线路上的电压还没有达到足够使得inv1翻转的地步(因为inv0有延时,Data有slope,传输门B打开后原来的Q值将通过inv2迫使feedback保持原来的值)。

QuartusII时序约束

03

动态时序分析的优点是准确度 高,适用于精确分析和优化电 路性能。

时序分析的步骤

01

02

03

04

建立时序模型

根据电路的逻辑功能和结 构,建立相应的时序模型 ,包括建立时间、保持时 间和时钟周期等参数。

时序约束设置

根据时序模型,设置相应 的时序约束,包括时钟源 、时钟网络、触发边沿、 建立时间和保持时间等。

时钟策略优化

选择适当的时钟策略,如多源 时钟、时钟分频等,以满足时 序要求。

参数调整

调整编译器的参数设置,如设 置更严格的时序约束或调整时

序例外等。

优化工具

Quartus II 软件

Altera(现Intel)提供的集成开发环境(IDE),包含多种时序约束 和优化的工具和功能。

逻辑合成工具

如Yosys、ABC等开源逻辑合成工具,可以用于优化设计的逻辑结构 。

时序约束的分类

建立时间(Setup Time):指信号在时钟边沿前应该 稳定的时间。

时钟周期(Clock Period):指时钟信号的周期性时间 间隔。

保持时间(Hold Time):指信号在时钟边沿后应该保 持稳定的时间。

偏斜(Skew):指时钟信号或数据信号在不同路径上 的延迟差异。

02

CATALOGUE

时序约束是数字逻辑设计和 FPGA编程中的重要概念,它确 保了电路在时序上的正确性。

时序约束的重要性

1

时序约束是确保数字电路正常工作的关键因素。

2

在FPGA设计中,如果不进行正确的时序约束, 可能会导致时序违规、数据传输错误等问题。

3

通过合理的时序约束,可以优化设计,提高电路 的工作效率,降低功耗和减小面积。

建立时间、保持时间和时序约束条件

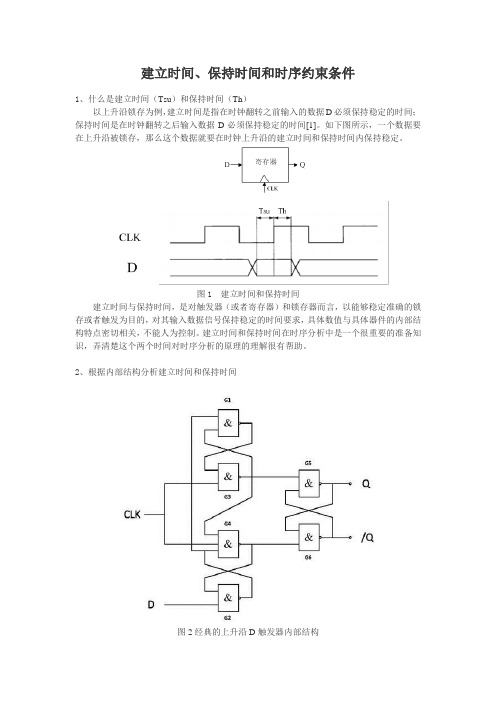

建立时间、保持时间和时序约束条件1、什么是建立时间(Tsu)和保持时间(Th)以上升沿锁存为例,建立时间是指在时钟翻转之前输入的数据D必须保持稳定的时间;保持时间是在时钟翻转之后输入数据D必须保持稳定的时间[1]。

如下图所示,一个数据要在上升沿被锁存,那么这个数据就要在时钟上升沿的建立时间和保持时间内保持稳定。

图1 建立时间和保持时间建立时间与保持时间,是对触发器(或者寄存器)和锁存器而言,以能够稳定准确的锁存或者触发为目的,对其输入数据信号保持稳定的时间要求,具体数值与具体器件的内部结构特点密切相关,不能人为控制。

建立时间和保持时间在时序分析中是一个很重要的准备知识,弄清楚这个两个时间对时序分析的原理的理解很有帮助。

2、根据内部结构分析建立时间和保持时间图2 经典的上升沿D触发器内部结构关于为什么会有建立时间和保持时间,我曾试图从触发器或锁存器内部的结构去分析和证实,但是看了许多资料,由于触发器的内部结构有很多,所以分析方法很多,说法也很多。

下面我选两个比较经典的结构来分析一下建立时间和保持时间。

以经典边沿触发的D触发器为例子,从内部结构上分析一下D触发器建立时间和保持时间。

这个说明主要来源于EETOP的一篇帖子,其结构在维基百科的触发器词条可以得到验证。

如上图所示,这是一个上升沿触发的D触发器,需要注意的是,图中的6个与非门都是有延迟的,也就是在某一时刻输入组合逻辑的数据,在一段时间之后才能影响其输出,这是产生建立时间和保持时间要求的最根本原因。

首先,我们在假设所有的与非门的延迟为0,叙述一下这个触发器的整体工作流程。

当CLK=0时,与非门G3和G4的输出均为1,输出的1反馈到G1和G2作为输入,导致G1和G2的输出分别为D和/D,输出的D和/D又反馈到G3和G4;而G5和G6在此期间一直锁存着之前的数据,不受输入影响。

图3 CLK=0时触发器内部信号详情当CLK=1时,与非门G3和G4的输出变为/D和D,输出到G5和G6作为输入,根据锁存器的原理,G5和G6最终会稳定的输出Q和/Q。

建立时间与保持时间

欢迎讨论!

图

建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变 的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;

保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的 时间,如果保持时间不够,数据同样不能被打入触发器。

下面用数字来说明一下加深理解(以下举例暂不考虑hold time):

建立时间

假设Tco(触发器固有的建立时间)=2ns

假设

假设2,Clock delay="0",data Delay = 3ns,那么数据port的新数据必须 在时钟port的时钟沿到来之前5ns就得赶到数据port,其中的3ns用来使新数据 从数据port赶到触发器的D端(由于data Delay),剩下的2ns用来满足触发器 的Tco。

从图中可以看出如果:

T-Tco-Tdelay>T3

即:

那么就满足了建立时间的要求,其中T为时钟的周期,这种情况下第二个触

图3符合要求的时序图

如果组合逻辑的延时过大使得

T-Tco-Tdelay<T3

那么将不满足要求,第二个触发器就在第二个时钟的升沿将采到的是一个不 定态,如图4所示。那么电路将不能正常的工作。

下面通过时序图来分析:设第一个触发器的输入为D1,输出为Q1,第二个触 发器的输入为D2,输出为Q2;

时钟统一在上升沿进行采样,为了便于分析我们讨论两种情况即第一:假设 时钟的延时Tpd为零,其实这种情况在FPGA设计中是常常满足的,由于在FPG A设计中一般是采用统一的系统时钟,也就是利用从全局时钟管脚输入的时钟, 这样在内部时钟的延时完全可以忽略不计。这种情况下不必考虑保持时间,因为 每个数据都是保持一个时钟节拍同时又有线路的延时,也就是都是基于CLOCK的延迟远小于数据的延迟基础上,所以保持时间都能满足要求,重点是要关心建 立时间,此时如果D2的建立时间满足要求那么时序图应该如图3所示。

如何建立一个健康的作息时间表

如何建立一个健康的作息时间表建立一个健康的作息时间表是确保身体和心理健康的重要一步。

以下是一个简单的指南,帮助你创建一个有效的作息时间表。

1. 规律的睡眠时间:每天保持规律的睡眠时间是建立健康作息时间表的关键。

尽量选择每晚相同的时间入睡和起床,确保获得充足的睡眠。

2. 早晨的活动:早晨是一天中最重要的时段之一。

尽量在早晨进行一些轻松的活动,比如晨跑、瑜伽或者简单的伸展运动,来帮助你唤醒身体和提升注意力。

3. 合理的工作时间:在制定作息时间表时,要合理安排工作时间。

避免长时间连续工作,每隔一段时间就要休息一下,避免疲劳和压力积累。

4. 午餐和休息:午餐时间是身体补充能量和放松的时刻。

确保有充足的时间吃饭,并在午餐后进行一段短暂的休息,以提高身体和思维的效率。

5. 适当的运动时间:在作息时间表中安排适当的运动时间非常重要。

根据个人喜好和身体状况,选择适合自己的运动方式,并将其纳入日常的作息时间表中。

6. 晚间放松:在晚上要安排一段时间用于放松身心。

可以选择阅读、听音乐、冥想或者进行其他你喜欢的放松活动,帮助你缓解压力和准备好入睡。

7. 限制使用电子设备的时间:在睡前的两个小时内,尽量避免使用电子设备,因为它们的蓝光会影响睡眠质量。

可以选择阅读纸质书籍或者进行其他不需要电子设备的活动。

8. 睡前的准备:在睡前可以进行一些准备工作,比如洗漱、放松瑜伽或者喝一杯温牛奶来帮助入睡。

确保睡眠环境舒适、安静,避免噪音和过度亮光。

记住,每个人的作息时间表可能会有所不同。

关键是找到适合自己的作息时间,坚持养成良好的作息习惯,才能获得最佳的身心健康效果。

1 什么是 和Holdup 时间? Hold time)。建立时间是指在

1 什么是Setup 和Holdup时间?建立时间(Setup Time)和保持时间(Hold time)。

建立时间是指在时钟边沿前,数据信号需要保持不变的时间。

保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。

见图1。

如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现metastability的情况。

如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

图1 建立时间和保持时间示意图2什么是竞争与冒险现象?怎样判断?如何消除?在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。

产生毛刺叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

3 用D触发器实现2倍分频的逻辑电路?Verilog描述:module divide2( clk , clk_o, reset);input clk , reset;output clk_o;wire in;reg out ;always @ ( posedge clk or posedge reset)if ( reset)out <= 0;elseout <= in;assign in = ~out;assign clk_o = out;endmodule图形描述:4 什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?线与逻辑是两个输出信号相连可以实现与的功能。

在硬件上,要用oc门来实现,由于不用oc门可能使灌电流过大,而烧坏逻辑门。

同时在输出端口应加一个上拉电阻。

5 什么是同步逻辑和异步逻辑?同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系。

6 请画出微机接口电路中,典型的输入设备与微机接口逻辑示意图(数据接口、控制接口、所存器/缓冲器)。

建立时间和保持时间

图1建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间。

个人理解:1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。

2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。

关于建立时间保持时间的考虑华为题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。

组合逻辑电路最大延迟为T2max,最小为T2min。

问:触发器D2的建立时间T3和保持时间T4应满足什么条件?分析:Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。

Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。

Tsetup:建立时间Thold:保持时间Tclk:时钟周期建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。

保持时间容限:保持时间容限也要求大于等于0。

由上图可知,建立时间容限=Tclk-Tffpd(max)-Tcomb(max)-Tsetup,根据建立时间容限≥0,也就是Tclk-Tffpd(max)-Tcomb(max)-Tsetup≥0,可以得到触发器D2的Tsetup≤Tclk-Tffpd(max)-Tcomb(max),由于题目没有考虑Tffpd,所以我们认为Tffpd=0,于是得到Tsetup≤T-T2max。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关于建立时间和保持时间的完全理解时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错;因而明确FPGA设计中决定系统时钟的因素,尽量较小时钟的延时对保证设计的稳定性有非常重要的意义。

建立时间与保持时间建立时间(Tsu:set up time)是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;保持时间(Th:hold time)是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。

建立与保持时间的简单示意图如下图1所示。

图1 保持时间与建立时间的示意图在FPGA设计的同一个模块中常常是包含组合逻辑与时序逻辑,为了保证在这些逻辑的接口处数据能稳定的被处理,那么对建立时间与保持时间建立清晰的概念非常重要。

下面在认识了建立时间与保持时间的概念上思考如下的问题。

举一个常见的例子。

图2 同步设计中的一个基本模型图2为统一采用一个时钟的同步设计中一个基本的模型。

图中Tco是触发器的数据输出的延时;Tdelay是组合逻辑的延时;Tsetup是触发器的建立时间;Tp d为时钟的延时。

如果第一个触发器D1建立时间最大为T1max,最小为T1min,组合逻辑的延时最大为T2max,最小为T2min。

问第二个触发器D2立时间T3与保持时间T4应该满足什么条件,或者是知道了T3与T4那么能容许的最大时钟周期是多少。

这个问题是在设计中必须考虑的问题,只有弄清了这个问题才能保证所设计的组合逻辑的延时是否满足了要求。

下面通过时序图来分析:设第一个触发器的输入为D1,输出为Q1,第二个触发器的输入为D2,输出为Q2;时钟统一在上升沿进行采样,为了便于分析我们讨论两种情况即第一:假设时钟的延时Tpd为零,其实这种情况在FPGA设计中是常常满足的,由于在FPG A 设计中一般是采用统一的系统时钟,也就是利用从全局时钟管脚输入的时钟,这样在内部时钟的延时完全可以忽略不计。

这种情况下不必考虑保持时间,因为每个数据都是保持一个时钟节拍同时又有线路的延时,也就是都是基于CLOCK的延迟远小于数据的延迟基础上,所以保持时间都能满足要求,重点是要关心建立时间,此时如果D2的建立时间满足要求那么时序图应该如图3所示。

从图中可以看出如果:T-Tco-Tdelay>T3即:Tdelay< T-Tco-T3那么就满足了建立时间的要求,其中T为时钟的周期,这种情况下第二个触发器就能在第二个时钟的升沿就能稳定的采到D2,时序图如图3所示。

图3 符合要求的时序图如果组合逻辑的延时过大使得T-Tco-Tdelay<T3那么将不满足要求,第二个触发器就在第二个时钟的升沿将采到的是一个不定态,如图4所示。

那么电路将不能正常的工作。

图4 组合逻辑的延时过大时序不满足要求从而可以推出T-Tco-T2max>=T3这也就是要求的D2的建立时间。

从上面的时序图中也可以看出,D2的建立时间与保持时间与D1的建立与保持时间是没有关系的,而只和D2前面的组合逻辑和D1的数据传输延时有关,这也是一个很重要的结论。

说明了延时没有叠加效应。

第二种情况如果时钟存在延时,这种情况下就要考虑保持时间了,同时也需要考虑建立时间。

时钟出现较大的延时多是采用了异步时钟的设计方法,这种方法较难保证数据的同步性,所以实际的设计中很少采用。

此时如果建立时间与保持时间都满足要求那么输出的时序如图5所示。

图5 时钟存在延时但满足时序从图5中可以容易的看出对建立时间放宽了Tpd,所以D2的建立时间需满足要求:Tpd+T-Tco-T2max>=T3由于建立时间与保持时间的和是稳定的一个时钟周期,如果时钟有延时,同时数据的延时也较小那么建立时间必然是增大的,保持时间就会随之减小,如果减小到不满足D2的保持时间要求时就不能采集到正确的数据,如图6所示。

这时即T-(Tpd+T-Tco-T2min)<T4,就不满足要求了,所以D2的保持时间应该为:T-(Tpd+T-Tco-T2min)>=T4 即Tco+T2min-Tpd>=T4从上式也可以看出如果Tpd=0也就是时钟的延时为0那么同样是要求Tco +T2min>T4,但是在实际的应用中由于T2的延时也就是线路的延时远远大于触发器的保持时间即T4,所以不必要关系保持时间。

图6 时钟存在延时且保持时间不满足要求下面用数字来说明一下加深理解(以下举例暂不考虑hold time):建立时间Tsetup=Tdelay+ Tco- Tpd假设Tco(触发器固有的建立时间)= 2ns假设1,Clock Delay =0,Data delay="0",那么数据port的新数据必须在时钟port的时钟沿到来之前2ns赶到数据port,才能满足触发器的Tco。

假设2,Clock delay="0",data Delay = 3ns,那么数据port的新数据必须在时钟port的时钟沿到来之前5ns就得赶到数据port,其中的3ns用来使新数据从数据port赶到触发器的D端(由于data Delay ),剩下的2ns用来满足触发器的Tco。

假设3,Clock delay="1ns",data Delay = 3ns,由于时钟port的时钟沿推后1ns到达触发器的时钟端,那么数据port的新数据只需在时钟port的时钟沿到来之前4ns赶到数据port即可。

假设4,假设时钟的周期T=4ns,即你的系统需要运行在250M频率上,那么以上的假设中,假设2显然是不成立的,也就是说在假设2的情况下,你的系统运行频率是低于250M的,或者说在250M系统里是有setup time violation的。

在假设2的情况下,由于Tco及Tpd均是FPGA的固有特性,要想满足4ns的T,那么唯一你能做的就是想方设法减小Tdelay,也就是数据路径的延时。

即所谓的找出关键路径,想办法优化之。

总结,在实际的设计中,对于一个给定的IC,其实我们很容易看到T,Tpd,T setup,Th都是固定不变的(在跨时钟域时,Tpd会有不同),那么我们需要关心的参数就是Tdelay,即数据路径的延时,控制好了这个延时,那我们的设计就不会存在建立时间和保持时间不满足的情况了!后记:有个著名的笔试题,这样说道:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min,该触发器的数据输出延时为Tco。

组合逻辑电路最大延迟为T2max,最小为T2min。

假设D1在前,D2去采样D1的数据(实际就是对图2的文字描述),问,触发器D2的建立时间T3和保持时间应满足什么条件。

这里给出一个简易公式供大家死记一下,以下两个公式确定了D2的Tsetup和Thold:1) D1的Tco + max数据链路延时+ D2的Tsetup < T(即T3 < T - Tco - T2max)2) D1的Tco + min数据链路延时> D2的Thold(即T4< Tco + T2min)其实上面的式2可以从T3+T4=T推出,不过要注意把1)中的T2max改为T2min 即可。

总之,建立时间长了,保持时间就短了。

实际中,某条数据链路延时是一个定值,只不过要求它落在区间{T2min,T2max}。

这也是T2min和T2max的实际意义。

从现实设计出发,个人觉得这个题改为考T2max和T2min更合适,那是不是有更多人犯晕呢?!hoho如果是那样的话,大家自己变个形吧^_^欢迎讨论!图1建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间。

个人理解:1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。

2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。

关于建立时间保持时间的考虑华为题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。

组合逻辑电路最大延迟为T2max,最小为T2min。

问:触发器D2的建立时间T3和保持时间T4应满足什么条件?分析:Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。

Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。

Tsetup:建立时间Thold:保持时间Tclk:时钟周期建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。

保持时间容限:保持时间容限也要求大于等于0。

由上图可知,建立时间容限=Tclk-Tffpd(max)-Tcomb(max)-Tsetup,根据建立时间容限≥0,也就是Tclk-Tffpd(max)-Tcomb(max)-Tsetup≥0,可以得到触发器D2的Tsetup≤Tclk-Tffpd(max)-Tcomb(max),由于题目没有考虑Tffpd,所以我们认为Tffpd =0,于是得到Tsetup≤T-T2max。

由上图可知,保持时间容限+Thold=Tffpd(min)+Tcomb(min),所以保持时间容限=Tffpd(min)+Tcomb(min)-Thold,根据保持时间容限≥0,也就是Tffpd(min)+Tcomb(min)-Thold≥0可以得到触发器D2的Thold≤Tffpd(min)+Tcomb(min),由于题目没有考虑Tffpd,所以我们认为Tffpd=0,于是得到Thold≤T2min。

关于保持时间的理解就是,在触发器D2的输入信号还处在保持时间的时候,如果触发器D1的输出已经通过组合逻辑到达D2的输入端的话,将会破坏D2本来应该保持的数据。

setup violation主要就是设法剪掉critical path的delay,要么pipeline,要么retiming,要么把combination往前后级挪一挪。