半导体制造工艺期末考试重点复习资料

苏州大学半导体工艺复习期末复习

半导体工艺期末复习针对性总结第一部分:论述题1、集成电路的工艺集成:晶体生长(外延)、薄膜氧化、气相沉积、光刻、扩散、离子注入、刻蚀以及金属化等。

☆2、工艺目的:①形成薄膜:化学反应,PVD,CVD,旋涂,电镀;②光刻:实现图形的过渡转移;③刻蚀:最后的图形转移;④改变薄膜:注入,扩散,退火;3、单晶硅制备的方法:直拉法、磁控直拉技术、悬浮区熔法(FZ)。

☆4、直拉法的关键步骤以及优缺点(1)关键步骤:熔硅、引晶、收颈、放肩、等径生长、收晶。

熔硅:将坩埚内多晶料全部熔化;引晶:先预热籽晶达到结晶温度后引出结晶;收颈:排除接触不良引起的多晶和尽量消除籽晶内原有位错的延伸;放肩:略降低温度(15-42℃),让晶体逐渐长到所需的直接为止;等径生长:提高拉速收肩,收肩后保持晶体直径不变,就是等径生长;收晶:拉速不变、升高熔体温度或熔体温度不变、加速拉速,使晶体脱离熔体液面。

(2)优点:①所生长单晶的直径较大,成本相对较低;②通过热场调整及晶体转速、坩埚转速等工艺参数的优化,可较好控制电阻率径向均匀性。

(3)缺点:石英坩埚内壁被熔硅侵蚀及石墨保温加热元件的影响,易引入氧、碳等杂质,不易生长高电阻率的单晶。

5、磁控直拉技术的优点:①减少温度波动;②减轻熔硅与坩埚作用;③降低了缺陷密度,氧的含量;④使扩散层厚度增大;⑤提高了电阻分布的均匀性。

6、悬浮区熔法制备单晶体:特点:①不需要坩埚,污染少;②制备的单晶硅杂质浓度比直拉法更低;③主要用于需要高电阻率材料的器件。

缺点:单晶直径不及CZ法☆7、晶体生长产生的缺陷种类及影响种类:点缺陷、线缺陷、面缺陷、体缺陷;影响:点缺陷…… 影响杂质的扩散运动;线缺陷…… 金属杂质容易在线缺陷处析出,劣化器件性能;面缺陷…… 不能用于制作集成电路;体缺陷…… 不能用于制作集成电路。

8、外延生长①常用的外延技术:化学气相淀积(CVD)、分子束外延(MBE)。

②化学气相淀积:通过气体化合物间的化学作用而形成外延的工艺;分类:常压(APCVD)、低压(LPCVD);③分子束外延:在超高真空下(约10−8Pa),一个或多个热原子或热分子束在晶体表面反应的外延技术;优点:(1)MBE能够非常精准地控制化学组成和掺杂浓度粉分布;(2)能够制作厚度只有原子层量级的单晶多层结构。

半导体工艺复习重点2.doc

1、投影式曝光技术(Projection exposure technology)答:投影式曝光是利用投影的方式,将掩模板上图案投影至相距好几厘米的晶片上。

2、化学机械抛光(CMP)答:化学机械抛光工艺是在晶片与抛光垫之间加入抛光液,并持续移动要平坦的晶片面摩擦抛光垫。

3、平衡分凝系数(Equilibrium segregated coefHcient)答:由于晶体是从融体中拉出来的,混合在晶体中(固态)的掺杂浓度通常和在界面处的融体(液体)中的是不同的。

此两种状态下的掺杂浓度的比例定义为平衡分凝系数。

4、磷硅玻璃回流(Phosphorus silicon glass)答:由于低温淀积的磷硅玻璃(掺杂二氧化硅)受热后变得较软易流动,可提供一平滑的表面,所以常作为邻近两金属层间的绝缘层。

此工艺称为磷硅玻璃回流。

5、台阶覆盖(The steps cover)答:台阶覆盖指的是淀积薄膜的表面几何形貌(拓补图)与半导体表面的各种台阶形状的关系。

6、分子束外延生长(MBE)答:分子束外延是在超高真空下一个或多个热原子或热分子束和晶体表面反应的外延工艺。

7、MESFET技术(名解)答:金属半导体场效应晶体管8、晶体中的点缺陷答:任何外来的原子合并到晶格中,无论在替代位置还是在间隙位置,晶格中若有原子丢失产生空位,一个主原子位于规则的晶格位置,并邻近一空位时称为弗兰克缺陷都是点缺陷。

9、退火(anneal)答:退火是一种金属热处理工艺,指的是奖金属缓慢加热到一定温度,保持足够时间,然后以适宜速度冷却。

10、非本征扩散(extrinsic diffusion)答:扩散受外界因素,如杂质离子的电价和浓度等控制的而非本征因素,即结构中本征热缺陷提供的空位浓度远小于杂质空位浓度的扩散,称为非本征扩散。

11、BiCMOS 技术答:BiCMOS是一种结合CMOS与双极性器件结构在单一集成电路内的技术。

12、等离子体答:等离子体是部分或完全电离的气体,包含正离子、负离子与一些未被电离的分子。

半导体制造技术期末复习

微电子期末复习集成电路开展历史:1947年。

贝尔实验室,点接触晶体管,1956年诺贝尔物理奖。

1948年W. Shockley 提出结型晶体管概念1950年第一只NPN结型晶体管1959年第一个集成电路集成电路--将多个电子元件〔晶体管、二极管、电容、电阻、电抗等〕集成到〔硅〕衬底上。

集成电路的制造步骤:1硅片制备2硅芯片制造〔重点〕3硅片测试/拣选4装配与封装5终测关键尺寸(CD):集成电路中半导体器件能够加工的最小尺寸。

它是衡量集成电路设计和制造水平的重要尺度,关键尺寸越小,芯片的集成度越高,速度越快,性能越好。

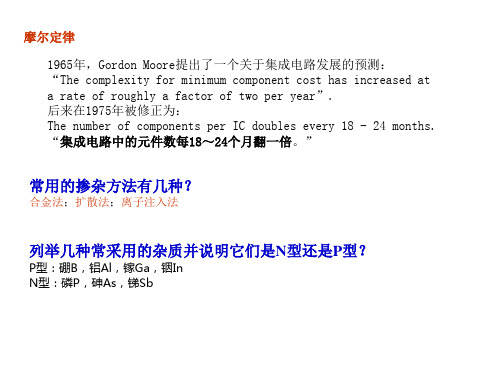

摩尔定律:Moore 定律是在1965 年由INTEL公司的Gordon Moore 提出的,其内容是:硅集成电路按照4 年为一代,每代的芯片集成度要翻两番、工艺线宽约缩小30%,IC工作速度提高1.5倍等开展规律开展。

单晶硅:单晶硅,也称硅单晶,具有根本完整的点阵构造的晶体。

不同的方向具有不同的性质,是一种良好的半导材料。

1用高纯度的多晶硅在单晶炉内拉制而成2纯度要求到达99.9999%,甚至到达99.9999999%以上。

用于制造半导体器件、太阳能电池等3半导体市场中95%以上的半导体器件及99%以上的集成电路用硅多晶硅:1:多晶硅硬度介于锗和石英之间,室温下质脆,切割时易碎裂2:主要用做半导体的原料,是制做单晶硅的主要原料,可作各种晶体管、整流二极管、可控硅、太阳能电池、集成电路、电子计算机芯片以及红外探测器等。

非晶硅:非晶硅是一种直接能带半导体,它的构造内部有许多所谓的“悬键〞,也就是没有和周围的硅原子成键的电子,这些电子在电场作用下就可以产生电流,并不需要声子的帮助,因而非晶硅可以做得很薄,还有制作本钱低的优点。

单晶硅的制备方法主要有:1:CZ法〔直拉法〕2:悬浮区熔法〔CF法〕其本质都是把熔融硅冷却成硅晶体CZ法:1:CZ法生长单晶硅把熔化的半导体级硅液体变成有正确晶向并且被掺杂成n或p型的固体硅锭,85%以上的单晶硅是采用CZ法生长,籽晶为所需晶向的单晶硅。

半导体制造工艺期末考试重点复习资料

1、三种重要的微波器件:转移型电子晶体管、碰撞电离雪崩渡越时间二极管、MESFET.2、晶锭获得均匀的掺杂分布:较高拉晶速率和较低旋转速率、不断向熔融液中加高纯度多晶硅,维持熔融液初始掺杂浓度不变。

3、砷化镓单晶:p型半导体掺杂材料镉和锌,n型是硒、硅和锑硅:p型掺杂材料是硼,n型是磷。

4、切割决定晶片参数:晶面结晶方向、晶片厚度(晶片直径决定)、晶面倾斜度(从晶片一端到另一端厚度差异)、晶片弯曲度(晶片中心到晶片边缘的弯曲程度)。

5、晶体缺陷:点缺陷(替位杂质、填隙杂质、空位、Frenkel,研究杂质扩散和氧化工艺)、线缺陷或位错(刃型位错和螺位错,金属易在线缺陷处析出)、面缺陷(孪晶、晶粒间界和堆垛层错,晶格大面积不连续,出现在晶体生长时)、体缺陷(杂质和掺杂原子淀积形成,由于晶体固有杂质溶解度造成).6、最大面为主磨面,与<110>晶向垂直,其次为次磨面,指示晶向和导电类型。

7、半导体氧化方法:热氧化法、电化学阳极氧化法、等离子化学汽相淀积法。

8、晶体区别于非晶体结构:晶体结构是周期性结构,在许多分子间延展,非晶体结构完全不是周期性结构.9、平衡浓度与在氧化物表面附近的氧化剂分压值成正比。

在1000℃和1个大气压下,干氧的浓度C0是5。

2x10^16分子数/cm^3,湿氧的C0是3x10^19分子数/cm^3。

10、当表面反应时限制生长速率的主要因素时,氧化层厚度随时间呈线性变化X=B(t+)/A线性区(干氧氧化与湿氧氧化激活能为2eV,);氧化层变厚时,氧化剂必须通过氧化层扩散,在二氧化硅界面与硅发生反应,并受扩散过程影响,氧化层厚度与氧化时间的平方根成正比,生长速率为抛物线X^2=B(t+)抛物线区(干氧氧化激活能是1。

24Ev,湿氧氧化是0.71eV). 11、线性速率常数与晶体取向有关,因为速率常数与氧原子进入硅中的结合速率和硅原子表面化学键有关;抛物线速率常数与晶体取向无关,因为它量度的是氧化剂穿过一层无序的非晶二氧化硅的过程。

(完整版)半导体工艺复习题..

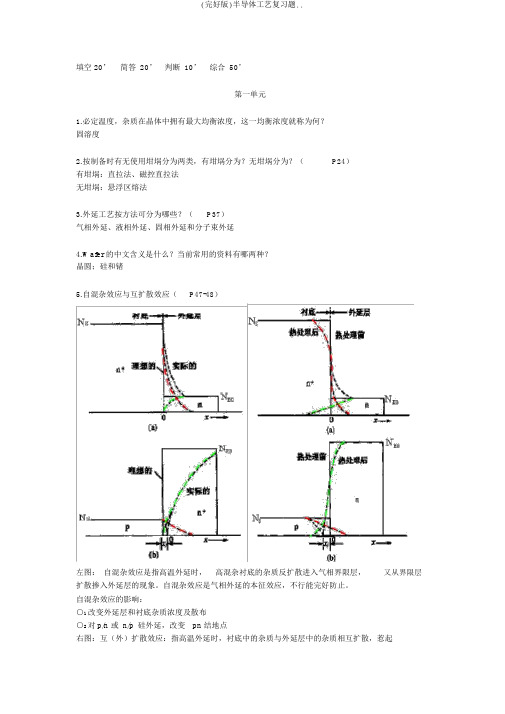

填空 20’简答20’判断10’综合50’第一单元1.必定温度,杂质在晶体中拥有最大均衡浓度,这一均衡浓度就称为何?固溶度2.按制备时有无使用坩埚分为两类,有坩埚分为?无坩埚分为?(P24)有坩埚:直拉法、磁控直拉法无坩埚:悬浮区熔法3.外延工艺按方法可分为哪些?(P37)气相外延、液相外延、固相外延和分子束外延4.Wafer 的中文含义是什么?当前常用的资料有哪两种?晶圆;硅和锗5.自混杂效应与互扩散效应(P47-48)左图:自混杂效应是指高温外延时,高混杂衬底的杂质反扩散进入气相界限层,又从界限层扩散掺入外延层的现象。

自混杂效应是气相外延的本征效应,不行能完好防止。

自混杂效应的影响:○1改变外延层和衬底杂质浓度及散布○2对p/n或n/p硅外延,改变pn 结地点右图:互(外)扩散效应:指高温外延时,衬底中的杂质与外延层中的杂质相互扩散,惹起衬底与外延层界面邻近的杂质浓度迟缓变化的现象。

不是本征效应,是杂质的固相扩散带来(低温减小、消逝)6.什么是外延层?为何在硅片上使用外延层?1)在某种状况下,需要硅片有特别纯的与衬底有同样晶体构造的硅表面,还要保持对杂质类型和浓度的控制,经过外延技术在硅表面堆积一个新的知足上述要求的晶体膜层,该膜层称为外延层。

2)在硅片上使用外延层的原由是外延层在优化pn 结的击穿电压的同时降低了集电极电阻,在适中的电流强度下提升了器件速度。

外延在 CMOS集成电路中变得重要起来,由于跟着器件尺寸不停减小它将闩锁效应降到最低。

外延层往常是没有玷辱的。

7.常用的半导体资料为何选择硅?1)硅的充裕度。

硅是地球上第二丰富的元素,占地壳成分的25%;经合理加工,硅能够提纯到半导体系造所需的足够高的纯度而耗费更低的成本。

2)更高的融化温度同意更宽的工艺容限。

硅1412 ℃>锗3)更宽的工作温度。

用硅制造的半导体件能够用于比锗937℃。

更宽的温度范围,增添了半导体的应用范围和靠谱性。

半导体工艺技术复习题

CK0712半导体工艺技术复习指导考试时间:11月23日(13周周一)下午2:30-5:00, 东九楼B403考试范围:《半导体制造基础》、讲义、作业题考试题型:名词解释、选择、简答、问答考试请携带:钢笔或圆珠笔、铅笔、尺、计算器、橡皮几点注意:1.重点掌握各章节的器件或工艺原理2.公式需记忆,但不超过作业题的范围;以下为复习要点:★首先,各章布置的习题要会做,所有习题都是考试范围。

第一章绪论1.简单叙述微电子学对人类社会的作用2.解释微电子学、集成电路的概念3.列举出你见到的、想到的不同类型的集成电路及其主要作用第二章半导体及其基本特性1.半导体、N型半导体、P型半导体、本征半导体、非本征半导体2.载流子、电子、空穴、平衡载流子、非平衡载流子、过剩载流子3.能带、导带、价带、禁带4.掺杂、正掺杂、负掺杂、施主、受主5.输运、漂移、扩散、产生、复合第三章半导体器件1.描述二极管的工作机理2.描述双极晶体管的工作机理3.描述MOSFET的工作原理第四章集成电路制造工艺概述1. 集成电路工艺主要分为哪几大类,每一类中包括哪些主要工艺,并简述各工艺的主要作用第五章晶体生长1.简述晶圆制造过程。

2.简述CZ(直拉法)生长单晶硅的过程。

3.简述悬浮区熔法(区熔法)的原理4.晶圆切割时的主标志面和次标志面指什么,有何作用?5.识别晶圆标志面。

第六章硅氧化1.硅热氧化的基本模型2.生长氧化层的两个阶段:线性阶段和抛物线阶段3.叙述干氧氧化和湿氧氧化的工艺过程和优缺点。

4.氧化层厚度表征方法第七章光刻1.光刻刻蚀光刻胶(光致抗蚀剂)正光刻胶负光刻胶反应离子刻蚀2.超净间分级3.光刻的最小线宽(临界尺寸)、分辨率、聚焦深度等主要参数的含义与计算4.掩膜材料及制作方法。

5.光刻胶(光致抗蚀剂)的主要成分及它们的作用。

6.描述正性和负性光刻胶在曝光过程中的变化。

7.遮蔽式曝光、接触式曝光、接近式曝光、投影式曝光8.紫外光谱的大致范围是?紫外光曝光光源的种类。

半导体制造技术期末题库参考答案

RVD 和 GILD 的原理, 它们的优缺点及应用方向。

答:快速气相掺杂(RVD, Rapid Vapor-phase Doping)是一种掺杂剂从气相直接向硅中扩散、 并能形成超浅结的快速掺杂工艺。 原理是利用快速热处理过程(RTP)将处在掺杂剂气氛中 的硅片快速均匀地加热至所需要的温度,同时掺杂剂发生反应产生杂质院子,杂质原子 直接从气态转变为被硅表面吸附的固态,然后进行固相扩散,完成掺杂目的。 RVD 技术的优势(与离子注入相比,特别是在浅结的应用上) :RVD 技术并不受注入所 带来的一些效应的影响,如:沟道效应、晶格损伤或使硅片带电。 RVD 技术的劣势:对于选择扩散来说,采用 RVD 工艺仍需要掩膜。另外,RVD 仍然要在 较高温度下完成。杂质分布是非理想的指数形式,类似固态扩散,其峰值处于表面处。 应用方向:主要应用在 ULSI 工艺中,例如对 DRAM 中电容的掺杂,深沟侧墙的掺杂, 甚至在 CMOS 浅源漏结的制造中也采用 RVD 技术。 气体浸没激光掺杂(GILD: Gas Immersion Laser Doping)的工作原理:使用激光器照射处 于气态源中的硅表面,使硅表面因吸收能量而变为液体层,同时气态掺杂源由于热解或 光解作用产生杂质原子,杂质原子通过液相扩散进入很薄的硅液体层,当激光照射停止 后,掺有杂质的液体层通过固相外延转变为固态结晶体,从而完成掺杂。 GILD 的优点:杂质在液体中的扩散速度非常快,使得其分布均匀,因而可以形成陡峭的 杂质分布形式。由于有再结晶过程,所以不需要做进一步的热退火。掺杂仅限于表面, 不会发生向内扩散,体内的杂质分布没有任何扰动。可以用激光束的能量和脉冲时间决 定硅表面融化层的深度。在一个系统中相继完成掺杂,退火和形成图形,极大简化了工 艺,降低系统的工艺设备成本。 GILD 的缺点:集成工艺复杂,技术尚不成熟。 GILD 的应用:MOS 与双极器件的制造,可以制备突变型杂质分布,超浅深度和极低的 串联电阻。 2. 集成电路制造中有哪几种常见的扩散工艺?各有什么特点? 答:按照原始扩散杂质源在室温下的相态可将扩散分为三类:固态源扩散,液态源扩散 与气态源扩散。 (1) 固态源扩散:常见的主要有开管扩散、箱法扩散和涂源法扩散 a.开管扩散是把杂质源和硅片分开放置在扩散炉管中,通过惰性气体将杂质蒸汽输 运只硅片表面。其特点是温度对杂质浓度和杂质分布有着直接的影响,重复性与稳 定性都很好。 b.箱法扩散是把杂质源和硅片壮在由石英或者硅做成的箱内,在氮气或氩气的保护 下进行扩散。其特点是扩散源多为杂质的氧化物,箱子具有一定的密闭性。含有杂 质的蒸汽与硅表面反应,形成含有杂质的薄氧化层,杂质由氧化层直接向硅内扩散。 其硅表面浓度基本由扩散温度下杂质在硅中的固溶度决定,均匀性较好。 c.涂源法扩散是把溶于溶剂的杂质源直接涂在待扩散的硅片表面,在高温下由遁形 其他保护进行扩散。其特点是杂质源一般是杂质的氧化物或者杂质的氧化物与惰性 氧化物的混合物,当溶剂挥发后在硅表面形成一层杂质源。这种方法的表面浓度难 以控制,且不均匀。可以通过旋转涂源工艺或化学气象淀积法改善 (2) 液态源扩散是使用携带气体通过液态源,把杂质源蒸汽带入扩散炉管。其特点是载 气除了通过携带杂质气体进入扩散炉内之外,还有一部分直接进入炉管,起到稀释

半导体工艺总复习

试问MOS器件制作中用得最多的是哪种方向晶面的材料?双极器件 呢?

(100)晶面:表面陷阱密度和Si/SiO2界面电荷数量较少,MOS器件采用。 (111)晶面:单晶生长容易,扩散结平坦,双极工艺多采用。

制造硅单晶的两种常用方法?

直拉(CZ)法和区熔(FZ)法

请列出二氧化硅在电路制作过程中的六种应用

12

画出N阱和P阱硅栅CMOS基本单元和双极型集成电路中NPN管的剖面结构图。

N阱CMOS基本单元

14

双极型集成电路中NPN晶体管的基本结构

15

写出硅局部氧化(LOCOS)的基本工艺流程,绘出剖面图。 答:a.热氧化生长一层薄的二氧化硅缓冲层; b.淀积氮化硅; c.刻蚀氮化硅,形成氧化窗口; d.湿氧氧化,形成厚的场氧区域,横向的氧化形成鸟嘴结构,通过控制二氧 化硅层和氮化硅层的厚度及湿氧氧化调节可减小鸟嘴尺寸; e.去掉氮化硅层。

硅化物(SALICIDE)自对准工艺

17

N阱CMOS工艺基本流程图

1.在P型衬底上离子注入,形成N阱

2.氮化硅掩蔽进行场氧氧化,形成有源区

18

N阱CMOS工艺基本流程图

3.淀积形成多晶硅栅

4.P+离子注入自对准形成PMOS管源漏区和NMOS管衬底连接区

19

N阱CMOS工艺基本流程图

5.N+离子注入自对准形成NMOS管源漏区和PMOS管衬底连接区

氧化分干氧氧化和湿氧氧化: •采用干氧法生长的SiO2薄膜,其质量最好,但生长速率太慢; •湿氧法生长速率快, 但不够致密,存在较多的位错和腐蚀坑; •干氧氧化用于对氧化层质量要求较高的场所,如MOS管的栅氧,LOCOS工艺中的衬垫氧等。 湿氧氧化用于较厚氧化层的生长,如MOS工艺中的场氧。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、三种重要的微波器件:转移型电子晶体管、碰撞电离雪崩渡越时间二极管、MESFET。

2、晶锭获得均匀的掺杂分布:较高拉晶速率和较低旋转速率、不断向熔融液中加高纯度多晶硅,维持熔融液初始掺杂浓度不变。

3、砷化镓单晶:p型半导体掺杂材料镉和锌,n型是硒、硅和锑硅:p型掺杂材料是硼,n型是磷。

4、切割决定晶片参数:晶面结晶方向、晶片厚度(晶片直径决定)、晶面倾斜度(从晶片一端到另一端厚度差异)、晶片弯曲度(晶片中心到晶片边缘的弯曲程度)。

5、晶体缺陷:点缺陷(替位杂质、填隙杂质、空位、Frenkel,研究杂质扩散和氧化工艺)、线缺陷或位错(刃型位错和螺位错,金属易在线缺陷处析出)、面缺陷(孪晶、晶粒间界和堆垛层错,晶格大面积不连续,出现在晶体生长时)、体缺陷(杂质和掺杂原子淀积形成,由于晶体固有杂质溶解度造成)。

6、最大面为主磨面,与〈110>晶向垂直,其次为次磨面,指示晶向和导电类型.7、半导体氧化方法:热氧化法、电化学阳极氧化法、等离子化学汽相淀积法。

8、晶体区别于非晶体结构:晶体结构是周期性结构,在许多分子间延展,非晶体结构完全不是周期性结构。

9、平衡浓度与在氧化物表面附近的氧化剂分压值成正比。

在1000℃和1个大气压下,干氧的浓度C0是5。

2x10^16分子数/cm^3,湿氧的C0是3x10^19分子数/cm^3。

10、当表面反应时限制生长速率的主要因素时,氧化层厚度随时间呈线性变化X=B(t+)/A线性区(干氧氧化与湿氧氧化激活能为2eV,);氧化层变厚时,氧化剂必须通过氧化层扩散,在二氧化硅界面与硅发生反应,并受扩散过程影响,氧化层厚度与氧化时间的平方根成正比,生长速率为抛物线X^2=B(t+)抛物线区(干氧氧化激活能是1.24Ev,湿氧氧化是0.71eV).11、线性速率常数与晶体取向有关,因为速率常数与氧原子进入硅中的结合速率和硅原子表面化学键有关;抛物线速率常数与晶体取向无关,因为它量度的是氧化剂穿过一层无序的非晶二氧化硅的过程。

12、较薄的氧化层MOSFET栅氧化层用干氧氧化,较厚的用湿氧氧化,如MOS集成电路中的场氧化层和双极型器件,以获得适当隔离和保护,20nm为界限。

13、给定氧化条件下,在<111>晶面衬底上生成的氧化层厚度大于<100>晶面衬底,因为<111〉方向线性速率常数更大。

值得注意的是温度和时间相同时,湿氧氧化厚度是干氧的5~10倍。

14、氧化掩膜厚度一般用实验测量方法获得,主要取决于特定温度和时间下,不能使低掺杂硅衬底发生反型,典型厚度为0。

5um~1.0um。

15、二氧化硅中各掺杂杂质扩散常数依赖氧的密度、性能和结构。

16、MOS器件受氧化层中的电荷和位于二氧化硅—硅界面处势阱影响。

17、势阱和电荷的基本类别:界面势阱电荷Qit(由于二氧化硅-硅界面特性产生,取决于这个界面的化学组分,势阱位于二氧化硅—硅界面处,能态在硅禁带中,界面势阱密度有取向性,用低温450℃氢退火进行钝化处理);固定电荷Qf(很稳定,难充电或放电,一般是阳性);氧势阱电荷Qot(与二氧化硅缺陷有关,可以通过低温退火处理消除);可移动离子电荷Qm(由于钠或其它碱性离子玷污导致,高温和高电场时可在氧化层中移动,改变阀值电压)。

18、测量氧化层厚度:表面光度法、椭圆偏光法和颜色对比法(主观化,不精确)。

19、光刻:将掩膜上的几何图形转移到涂在半导体晶片表面的敏光薄层材料上的工艺过程。

20、级别为M3.5的洁净室(公制),每立方米直径≥0.5um的尘埃粒子数不超过10^3.5,,大约为3500粒子数/m^3。

21、曝光设备性能参数:分辨率、对准精度和生产效率.分辨率指能精确转移到半导体表面光刻胶上的最小特征尺寸值;对准精度指各个掩膜与先前刻在硅片上的图形相互套准的程度;生产效率指某次光刻中掩膜在1小时内能曝光的硅片数.22、光学曝光法:遮蔽式曝光和投影式曝光;遮蔽式曝光掩膜和硅片彼此直接接触为接触式曝光(由尘埃粒子引起的缺点:掩膜与硅片接触时,硅片上的尘埃粒子或硅渣会嵌入掩膜,使掩膜永久性损伤,使随后使用它曝光的每个硅片有缺陷),彼此非常靠近为接近式曝光(将掩膜受损程度减至最小).23、一个完整的集成电路工艺流程需要15~20层不同的掩膜.24、标准尺寸的掩膜衬底是由15x15cm^2,厚度为0。

6cm的玻璃平板制成。

25、掩膜的主要指标是密度缺陷,掩膜制造过程或以后的图形曝光过程可能会给掩膜带来缺陷。

26、光刻胶是一种对辐照敏感的化合物,可分为正性和负性,正胶的曝光部分在显影时更易于溶解而去掉,所得图形与掩膜上相同,负胶曝光部分在显影时不易被溶解,所得图形与掩膜上相反。

正胶组成:感光剂、树脂基片和有机溶剂,曝光前,感光剂不易溶于显影液,曝光后,曝光区内的感光剂由于吸收了能量导致化学结构发生变化,在显影液中可被溶解,显影后,曝光区内的光刻胶被去掉.负胶是一种含感光剂的聚合物。

曝光后,感光剂吸收光能转变为化学能引起链接反应,是聚合物分子间发生交联,不易溶于显影液,经显影,未曝光部分被溶解,负胶缺点是显影时光刻胶吸收显影液溶剂膨胀,限制了负胶分辨率.27、分辨率增强技术:相移掩膜和光学邻近效应校正.28、电子束曝光优点:能生成亚微米线宽的光刻胶图形,自动化程度高,控制精确,比化学曝光法的聚焦好,而且能直接在半导体晶片上形成图形而不需掩膜;缺点电子束曝光机的产出率低,在分变率小于0.25μm时,每小时只能加工10片左右的晶片,只适于生产掩膜或制造少量定制电路或者验证设计之用。

29、聚焦电子束扫描方式:光栅扫描和矢量扫描(节省时间)。

30、光学曝光中,分辨率受光衍射限制,电子束曝光中则受电子散射限制。

31、电子束在某处的辐照影响邻近区域的辐照现象为邻近效应。

32、离子束曝光由于离子质量较大,散射只用比电子若,故其比光学、X射线或电子束曝光技术有更高的分辨率。

离子束曝光系统:扫描焦聚束系统和掩膜束系统。

33、曝光法:电子束曝光、超紫外光曝光、X射线曝光、离子束曝光和光学曝光。

34、湿法化学刻蚀机理:反应物通过扩散运输到反应表面、化学反应发生在此表面、通过扩散将反应生成物从表面移除.35、最常用的刻蚀剂是硝酸和氢氟酸在水或醋酸中的混合液。

36、对硅晶格,<111〉晶面比<110>晶面和〈100〉晶面的每隔单元上有更多的化学键,故〈111>晶面上的刻蚀速率应该较小.37、二氧化硅的湿法刻蚀通常使用添加或不添加氟化铵的HF稀释溶液.38、室温下浓HF溶液、HF稀释溶液或煮沸的磷酸溶液可对硅的氮化物薄膜进行刻蚀.39、典型刻蚀液是73%的磷酸、4%的硝酸、3。

5%的醋酸和19.5%的去离子水混合溶液,温度在30℃到80℃间。

40、湿法刻蚀进行图形转移的缺点是掩膜层下有横向钻蚀,导致刻蚀后图形分辨率下降。

41、干法刻蚀就是等离子体辅助刻蚀,利用低压放电等离子体技术刻蚀方法,包括等离子体刻蚀、反应离子刻蚀、溅射刻蚀、磁增强反应离子刻蚀,反应离子束刻蚀和高密度等离子体刻蚀。

42、等离子体刻蚀工艺步骤:刻蚀反应剂在等离子体中产生;反应剂以扩散方式通过不流动的气体边界层到达表面;反应剂吸附在表面;发生化学反应和离子轰击等物理效应生成可挥发性化合物;这些化合物从表面解析出来,通过扩散回到等离子体气体中,然后由真空装置抽出。

43、等离子体刻蚀技术基于低压时在气体中产生的等离子体.基本方法是物理方法和化学方法;44、大部分等离子体工艺释放红外线到紫外线范围内的射线。

45、硅沟槽刻蚀:随着器件特征尺寸的减小,由于需要在电路器件与DRAM存储单元的贮存电容之间进行隔离,硅片表面面积也相应减少了。

这些表面隔离区可以通过对硅衬底刻蚀出沟槽,并用适当的电介质或导电材料填充来减少,深沟槽(<5μm)主要形成存储电容,浅沟槽(〈1μm)用来隔离。

46、氯基和溴基的化学剂对硅有较高的硅刻蚀速率,且对二氧化硅掩膜具有较高的刻蚀选择性。

HBr+NF3+SF6+O2的混合气体来形成大约7μm深的沟槽电容,这种气体可以用于浅沟槽隔离的刻蚀。

47、在铝刻蚀过程中加入含碳的气体CHF3或N2以形成侧壁钝化,获得各向异性刻蚀效果。

48、掺杂是将一定数量的杂质掺入半导体材料的工艺,作用是改变半导体材料的电学特性。

扩散和离子注入是主要掺杂方法.49、对于硅扩散,硼常用作p型杂质,砷和磷为n型杂质。

50、高温下,晶格原子在格点平衡位置附近振动,基质原子可能获得足够能量脱离晶格格点成为间隙原子,而产生一个空位,邻近杂质原子可以移到该空位,这种扩散机制为替代式扩散;间隙杂质原子从一个位置运动到另一个位置却不占据格点,称为填隙式扩散。

51、费克扩散方程或法则:52、扩散工艺的结果用三种测量方式进行评估:结深、薄层电阻和扩散层的杂质分布。

53、扩散分布也可以用电容—电压法测量.54、测量总杂质分布更精确的方法是二次离子质谱法(SIMS)。

55、低温时扩散率为本征扩散率。

56、非本征扩散区域内,扩散率与杂质浓度有关,而且扩散和相继的扩散之间存在相互作用和协同效应.57、离子注入将具有一定能量的带电粒子掺入到衬底中,注入能量在1keV到1MeV间,所对应离子分布的平均深度范围是10nm到10μm。

58、离子从进入晶片到停止在晶体中所经过的总距离称为射程R,从此距离在入射轴上的投影称投影射程Rp,投影射程的统计涨落为投影偏差σp。

59、降低沟道效应方法:覆盖一层非晶体的表面层;将硅晶片晶向偏转;在晶片表面制作一个损伤层。

60、外延层生长技术有化学气相淀积和分子束外延.61、分子束外延式指在具有极高真空度的环境中,一束或多束热原子流或者分子流与晶体表面发生反应而生成外延层的工艺。

62、真空技术参数—分子碰撞率Φ,即单位时间衬底的单位面积上多少分子与其碰撞,是分子质量、温度和压强的函数Φ=p(2πmkT)^(1/2).63、异质外延式指外延层与衬底是两种不同的半导体,且外延层必须保持理想化的界面,意味过界面的原子键必须连续.64、三种外延层的生长:晶格匹配外延、应力外延和无应力外延。

65、外延层中的缺陷:来自衬底的缺陷(采用没有位错的半导体衬底避免);来自界面的缺陷(衬底表面必须彻底清洗或采用方程SiCl4+2H2 -Si+4HCl 的逆反应进行现场反蚀);沉积物或位错环;低角晶粒间界;刃型位错。

66、磷玻璃流:低温淀积的磷玻璃(掺P的SiO2)在加热时会变软而流动,形成光滑表面,所以经常采用这种SiO2作为相邻金属层间的绝缘体.适合采用磷的浓度为6%~8%。

67、减小ULSI电路中RC常数,需要互连材料具有低电阻率和掩膜层低电容。

68、保证正确操作,DRAM中存储电容必须保持为定值。