基于FPGA的自适应均衡器的研究与设计

基于FPGA的延时块LMS均衡器的设计与实现

基于FPGA的延时块LMS均衡器的设计与实现

裴亮锋;陈自力

【期刊名称】《计算机测量与控制》

【年(卷),期】2013(21)1

【摘要】码间干扰是影响无人机数据链高速传输的重要因素之一;为了减小码间干扰对数据链的影响,提高数据链的通信速度,文章在LMS算法的基础上,分析并设计具有并行处理功能的延时块LMS均衡器,利用verilog HDL完成了该算法在FPGA上的实现;仿真结果表明均衡器能有效地减少数据链中的码间干扰,通信速度提高一倍,这为以后研究设计更高速均衡器打下了基础.

【总页数】4页(P184-187)

【作者】裴亮锋;陈自力

【作者单位】军械工程学院,石家庄 050003;军械工程学院,石家庄 050003

【正文语种】中文

【中图分类】TP302

【相关文献】

1.采用FPGA实现基于LMS算法的自适应均衡器的设计研究 [J], 金健;陈涛

2.基于FPGA的分数间隔预测判决反馈均衡器的设计与实现 [J], 霍亚娟;葛临东;王彬

3.基于DDLMS算法的信道均衡器的FPGA实现 [J], 白勇博;陈自力;祁栋升

4.基于FPGA的数字音响均衡器的设计与实现 [J], 宋庆恒;周滔顺;殷富有

5.基于FPGA的FSE-CMA盲均衡器设计与实现 [J], 郭业才; 李峰; 万逸儒; 胡峥

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的自适应滤波器的设计

摘要自适应滤波器是统计信号处理的一个重要组成部分。

在现代滤波处理技术中,自适应滤波器的处理效果尤为突出。

在众多滤波器中,特别是在一些对信号处理的实时性要求比较高,体积功耗有严格限制的场合,使用FPGA硬件实现的数字滤波器更为广泛。

本论文从自适应滤波器研究的重要意义入手,介绍了线性自适应滤波器的算法,对几种基于最小均方误差准则或最小平方误差准则的自适应滤波器算法进行研究,就滤波器的基本原理及设计方法做了简单的介绍,最终设计基于FPGA的LMS算法设计复数自适应滤波器,对设计方法进行叙述,并以VHDL语言编写程序进行仿真测试。

关键词:自适应滤波器;FPGA;自适应算法LMS;有限冲激响应滤波器FPGA-based design of adaptive filterStudent:TAN xx Teacher:CHEN xxAbstract:Adaptive filter is a statistical signal processing as an important component. Processing technology in the modern filter, the adaptive filter, particularly in the treatment effect. Among the filters, especially in some of the real-time signal processing requirements of higher power, there are strict restrictions on the size of the occasion, the use of FPGA hardware to achieve a wider range of digital filters.In this paper, adaptive filter from the importance of research to start to introduce the linear adaptive filter algorithm, based on several criteria MMSE or least square error criteria for the study of adaptive filter algorithm, it filters The basic principle and design method of a brief introduction, the final design of FPGA-based design of complex LMS adaptive filter algorithm, the design methods described, and VHDL languages in maxplus simulation test platform.Keywords: adaptive filter;FPGA;LMS adaptive algorithm;finite impulse response filter目录摘要 (I)1 绪论 (1)1.1 引言 (1)2 自适应算法研究及分析 (1)2.1 自适应滤波基本概念 (1)2.2 变步长自适应滤波算法 (2)2.3 仿射投影算法 (3)2.4 RLS自适应滤波算法 (3)2.5 LMS算法及其推广 (3)2.6小结 (6)3 滤波器原理介绍 (7)3.1 自适应滤波器原理 (7)3.2 本文滤波器的工作原理 (8)4 基于FPGA的自适应滤波器的设计 (11)4.1 基本设计方法 (11)4.2 设计流程 (12)4.2.1 设计准备 (13)4.2.2 设计输入 (13)4.2.3 功能仿真 (14)4.2.4 设计处理 (14)4.2.5 时序仿真 (14)4.2.6 器件编程测试 (14)4.3 自适应滤波器设计 (15)4.3.1 自适应滤波器结构 (16)4.3.2 复数滤波器设计与实现 (18)4.3.3 基本设计准备 (19)4.3.4 复数自适应滤波器设计防真 (22)4.4小结 (24)5 结论 (25)致谢 (26)参考文献 (27)1 绪论1.1 引言随着信号处理技术的不断发展,对信号处理速度的要求也不断提高。

基于FPGA自适应均衡器的研究与实现的开题报告

基于FPGA自适应均衡器的研究与实现的开题报告一、研究背景及意义自适应均衡器(Adaptive Equalizer)是数字通信领域中的重要技术之一,能够对接收信号的失真进行补偿,从而提高系统的抗干扰能力和传输性能。

较早期的自适应均衡器是基于DSP处理器或者纯软件实现的,但是这种实现方式存在处理速度慢、功耗较大等问题。

而基于FPGA实现自适应均衡器可以有效解决这些问题,具有处理速度快、硬件可重构、可实现并行处理等优点,因此也成为了近年来广泛应用的实现方式。

本文将会探讨如何基于FPGA实现自适应均衡器,并研究不同均衡算法的优缺点,比较它们在不同信道环境下的性能差异。

研究结果将有助于提高数字通信系统的稳定性和性能表现,对智能终端、移动通信网络等领域具有一定的应用价值和市场前景。

二、研究内容及方法1.研究内容本研究将围绕如下的研究内容展开:(1)自适应均衡器的基本原理及各种均衡算法的模型推导和性能分析。

(2)基于FPGA的自适应均衡器系统的设计和实现,包括硬件电路系统的搭建和算法模块的软件设计。

(3)针对均衡器在不同信道环境下的性能差异进行实验和数据分析,比较不同算法性能的差异。

2.研究方法本研究将采用如下方法进行:(1)文献调研和理论分析:对自适应均衡器和各种均衡算法进行综述和调研,比较它们的优缺点,找出其中适合用于FPGA实现的算法。

(2)硬件电路设计:建立自适应均衡器硬件电路,包括模拟信号采集模块、ADC模块、FPGA模块、DAC模块和模拟输出模块等。

(3)算法模块设计:在FPGA中实现各种自适应均衡算法,比较它们在不同信道环境下的性能表现。

(4)实验和数据分析:利用仿真软件和实际硬件平台,对自适应均衡器在不同信道环境下的性能进行测试和分析,比较各种算法的性能差异。

三、预期成果1.硬件电路设计和实现自适应均衡器,测试其在不同信道环境下的性能表现。

2.实现自适应均衡器中的各个算法模块,比较它们的性能差异,找出适合实际应用的算法。

基于FPGA和符号L MS算法的自适应均衡器设计

基于FPGA和符号L MS算法的自适应均衡器设计邱陈辉;李锋;徐祖强【期刊名称】《计算机工程与设计》【年(卷),期】2014(000)007【摘要】To adaptively equalize the transmission channel of communication system,the adaptive equalizer based on field pro-grammable gate array (FPGA)was used in this system.Signum-LMS algorithm was proposed on the basis of standard least mean square (LMS)algorithm.It decreased the consumption of FPGA hardware resource by reducing the number of multiplica-tions in the adaptive equalization.MATLAB software simulation proved the feasibility and effectiveness of this scheme.Quartus II and ModelSim hardware simulations verified that the adaptive equalizer utilizing the signum-LMS algorithm had superiority in the consumption of FPGA hardware resource.%为了对通信系统的传输信道进行自适应均衡处理,在通信系统中加入了基于现场可编程门阵列(FPGA)的自适应均衡器。

在标准最小均方(LMS)算法的基础上,提出了符号LMS算法。

该算法通过降低自适应均衡过程中的乘法运算次数来减少该自适应均衡器所消耗的FPGA硬件资源。

基于FPGA自平衡控制器的设计

基于FPGA自平衡控制器的设计查长礼;王陈宁【期刊名称】《安庆师范学院学报(自然科学版)》【年(卷),期】2012(018)003【摘要】Aimming at the rotary encoder angle measurement and control of stepper motor characteristic,we introduce one kind of the core component based on the FPGA by using VHDL hardware description language in the FPGA to achieve the rotary encoder frequency, direction discrimination, counting function, rotary eneoder for angle sensor and stepper motor as the driving self bal- ance controller design method. The whole system is correct by using Quartus programming software simulation analysis, and its op- eration is stable and accurate by measure through the hardware experiment platform authentication system.%针对旋转编码器角度测量与步进电机控制的特点,介绍了一种基于FPGA为核心器件,运用VHDL硬件描述语言在FPGA中实现旋转编码器倍频、辨向、计数的功能,旋转编码器为角度传感器以及步进电机为驱动的自平衡控制器设计的方法。

整个系统利用Quartus编程软件仿真分析正确,硬件实验平台验证该系统运行稳定、测量准确。

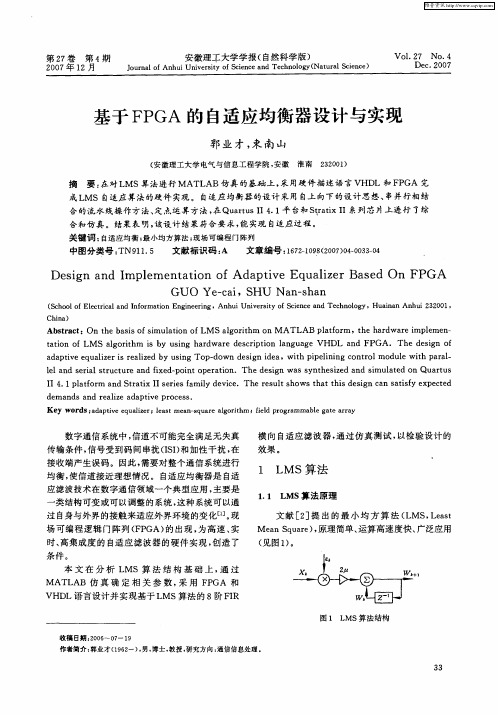

基于FPGA的自适应均衡器设计与实现

Ab ta t s r c :On t e b ss o i l t n o h a i fsmu a i f o LM S a g rt m n M ATLAB p a f r ,t eh r wa e i lm e — lo i h o lto m h a d r mp e n

一

横 向 自适应 滤 波 器 , 过仿 真测 试 , 通 以检 验设 计 的 效果 。

L MS算 法

11 L . MS算 法原 理 文 献 [ ] 出 的 最 小 均 方 算 法 ( MS L at 2提 L , es Me nS u r ) 原理 简单 、 算高 速度快 、 a q ae , 运 广泛应用

误差调整模块先根据期望响应信号dt和滤波器输出值弘求得输出误差值再将输出误差与迭代步长的2倍相乘得到中间变量2卢缸为权向量的迭代提供调整后的误差数据该逻辑单元主要进行减法计算和乘法运算

维普资讯

第2 卷 7

第 4期

安徽理 工 大学 学报 ( 自然 科 学版 )

t t n o a i fLM S ag rt m sb sn a d r e ci t n ln u g oቤተ መጻሕፍቲ ባይዱ l o ih i y u i g h r wa ed srp i a g a e VHDL a d FP o n GA. Th e in o e d sg f

数字通 信系统 中 , 信道不 可能 完全 满足无 失 真

传输 条件 , 信号 受到 码 间 串扰 (S ) 加性 干 扰 , I I和 在 接收端 产生误 码 。因此 , 需要 对 整个通 信系统 进行 均衡 , 使信道接 近 理想情 况 。 自适 应均 衡器是 自适 应滤 波技术 在数字 通 信领域 一个典 型应 用 , 主要 是

基于FPGA的均衡器的设计开题报告

07级毕业论文开题报告学院专业毕业论文题目学生姓名班级指导教师日期年月日论文题目:基于FPGA的均衡器的设计一、选题的依据及课题的意义FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA的基本特点1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5) FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM 进行编程。

用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA 芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。

掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA 的编程无须专用的FPGA编辑器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA功能时,只需换一片EPROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

因此,FPGA的使用非常灵活。

在移动通信和高速无线数据通信中,多径效应和信道带宽的有限性以及信道特性的不完善性导致数据传输时不可避免的产生码间干扰,成为影响通信质量的主要因素,而信道的均衡技术可以消除码间干扰和噪声,并减少误码率。

其中判决反馈均衡器(DFE)是一种非常有效且应用广泛得对付多径干扰得措施。

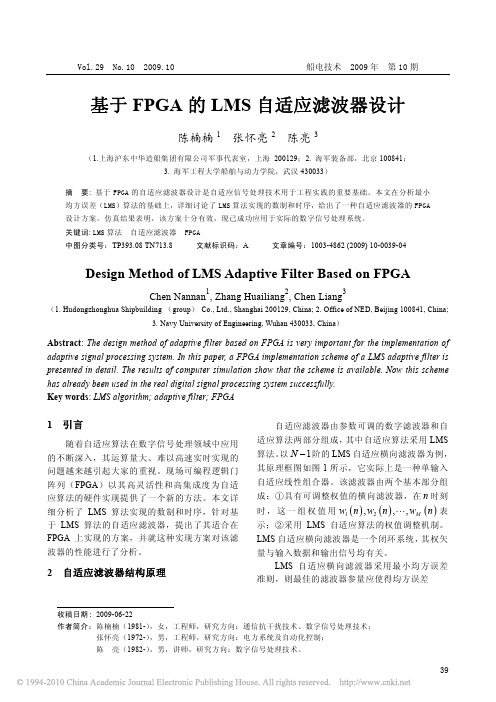

基于FPGA的LMS自适应滤波器设计

基于FPGA的LMS自适应滤波器设计陈楠楠1张怀亮2陈亮3(1.上海沪东中华造船集团有限公司军事代表室,上海 200129;2. 海军装备部,北京100841;3. 海军工程大学船舶与动力学院,武汉430033)摘要: 基于FPGA的自适应滤波器设计是自适应信号处理技术用于工程实践的重要基础。

本文在分析最小均方误差(LMS)算法的基础上,详细讨论了LMS算法实现的数制和时序,给出了一种自适应滤波器的FPGA 设计方案。

仿真结果表明,该方案十分有效,现已成功应用于实际的数字信号处理系统。

关键词: LMS算法 自适应滤波器 FPGA中图分类号:TP393.08 TN713.8 文献标识码:A 文章编号:1003-4862 (2009) 10-0039-04 Design Method of LMS Adaptive Filter Based on FPGAChen Nannan1, Zhang Huailiang2, Chen Liang3(1. Hudongzhonghua Shipbuilding (group)Co., Ltd., Shanghai 200129, China; 2. Office of NED, Beijing 100841, China;3. Navy University of Engineering, Wuhan 430033, China)Abstract: The design method of adaptive filter based on FPGA is very important for the implementation of adaptive signal processing system. In this paper, a FPGA implementation scheme of a LMS adaptive filter is presented in detail. The results of computer simulation show that the scheme is available. Now this scheme has already been used in the real digital signal processing system successfully.Key words: LMS algorithm; adaptive filter; FPGA1 引言随着自适应算法在数字信号处理领域中应用的不断深入,其运算量大、难以高速实时实现的问题越来越引起大家的重视。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Us i n g a d a p t i v e e q u a l i z a t i o n i n mu hi p a t h f a d i n g s i t u a t i o n c a n e f f e c t i v e l y i mp r o v e t h e r e c e i v e r p e r f o r ma n c e . T h i s p a p e r

Ab s t r a c t : I n r e c e n t y e a r s ,t h e t e c h n o l o g y o f a d a p t i v e e q u a l i z e r h a s b e e n u s e d l a r g e l y i n t h e c o mmu n i c a t i o n s y s t e ms .

LI L u — l u . J I NG Da — h a i

( C o m p u t e r a n dI n f o r ma t i o n I n s t i t u t i o n h o h a i U n i v e r s i t y , N a n j i n g 2 1 1 1 0 0 , C h i n a )

d e s c r i b e s t h e p r i n c i p l e o f t h e a d a p t i v e e q u a l i z e r a n d b e I mp r o v e i t t o a c c o mmo d a t e t h e h i g h r a t e o f t h e wi d e b a n d d i g i t a l

李路路 ,静大海

( 河 海大 学 计 算 机 与信 息 学院 ,江 苏 南 京 2 1 0 0 0 0) 摘要 : 近 年 来 , 自适 应 均衡 技 术 在 通 信 系统 中 的应 用 日益 广 泛 ,利 用 自适 应 均 衡 技 术 在 多径 环 境 中 可 以 有 效 地 提 高 数 字 接 收 机 的 性 能 。 为 了适 应 宽 带 数 字接 收机 的 高 速 率 特 点 ,本 文 阐述 了 自适 应 均 衡 器 的 原 理 并 对 其 进 行 改 进 。 最 后使用 F P G A 芯 片和 V e r i l o g HD L设 计 实 现 了 自适 应 均衡 器 并仿 真 验 证 了新 方 法 的 有 效 性 。

d ( 为期 望输 入信 号 ,e ( 为误 差 ,其 中 为步 长 因子 , 用 以控制 收 敛 速度 与 稳定 性 , L M S算 法 收敛 的 条件 为 :0 < u < l / 2 m a x , 2 m a x 是 输 入 信 号 自相 关 矩 阵 的 最 大 特 征 值 。 式 ( 3)

第2 2卷 第 5期

V6 . 2 2

电子设 计工程

E l e c t r o n i c De s i g n E n g i n e e r i n g

2 0 1 4年 3月

Ma L 2 01 4

NO . 5

基于 F P G A 的 自适应均 衡器的研 究与设计

Ke y wo r d s : a d a p t i v e e q u a l i z e r ; wi d e b a n d d i g i t a l r e c e i v e r ; F P GA; Ve r i l o g HDL

信道均衡技术 ( C h a n n e l e q u a l i z a t i o n )是 指 为 了 提 高 衰 落信 道 中 的通 信 系 统 的传 输 性 能 而采 取 的一 种 抗 衰 落措 施 。 它 主要 是 减 小 信道 的多 径 时延 带 来 的 码 问 串扰 ( I S I )问题 。 其 原理 是 对 信 道 或 整个 传 输 系统 特 性 进行 补 偿 ,从而 达 到 系 统 传 输 的 要 求 Ⅲ。在 实 际 的 通信 系统 中 ,信 道 的特 性 是 未 知 的 并 且 是不 理 想 的 ,传 统 的均 衡 器 无 法满 足 系统 的 要 求 , 自 适 应 均 衡器 直 接 从 传 输 的信 号 中 ,根 据某 种 算 法 不 断调 整 系

统 中滤 波器 的增 益 ,来适 应 信 道 的随 机变 化 ,从 而 有更 好 的

( ) = “ ( ) ¨ ( ) e ( , 1 ) = n ) - y ( n ) w ( + 1 ) = w ( ) + 2 t w( n ) u ( n )

( 1 ) ( 2) ( 3 )

关 键 词 : 自适 应均衡 器 ;宽 带数 字接 收机 ;F P G A;V e r i l o gH DL 中图分 类号 :T N 9 2 文献标 识码 :A 文 章编 号 :1 6 7 4 — 6 2 3 6 ( 2 O 1 4 ) O 5 — 0 0 9 2 — 0 3

De s i g n a nd i mp l e me nt a t i o n o f e qua l i z e r ba s e d o n FPGA

r e c e i v e r , F i n a l l y d e s i g n a d a p t i v e e q u a l i z e r a n d s i mu l a t i o n w i t h F P GA a n d Ve r i l o g HDL t o v e r i f y i t s v a l i d i t y.