verilog多模块编程实例

verilog中generate的用法

verilog中generate的用法

1. 嘿,你知道吗?generate 可以用来生成多个模块实例呢!就像有个魔法盒子,能变出好多一样的东西。

比如可以用它生成多个相同功能的计数器。

2. generate 还能根据条件来生成代码呀!这不就像是根据天气来决定穿什么衣服嘛,条件不同,生成的代码也不同。

比如根据参数决定是生成加法器还是减法器。

3. 哇塞,generate 能做循环生成代码呢!这简直就如同工厂的流水线,一批批地生产出代码模块。

像用它来循环生成一组寄存器。

4. 嘿,你想过没,generate 可以把复杂的代码结构变得清晰简洁呀!就好像把一团乱麻整理得整整齐齐。

比如说把多个相似的逻辑块用 generate 来组织。

5. 哎呀呀,generate 能让代码的灵活性大大增强呢!就好像给代码装上了灵活的关节,可以随意摆动。

比如根据不同的配置生成不同的电路结构。

6. 嘿,你瞧,generate 还能用来创建数组呢!这不就跟摆棋子一样,可以整齐地摆成一排。

像用它创建一个二维的信号数组。

7. 哇哦,generate 能帮助我们更好地管理大型设计呢!就如同有个厉害的管家,把一切都安排得井井有条。

比如在大规模的芯片设计中用它来组织模块。

8. 嘿,generate 在处理复杂逻辑关系时可太有用啦!就像解开一团纠结的线,让一切都清楚明白。

比如用它来实现根据多种条件切换的逻辑。

9. 你知道吗,generate 的用法真的是超级多呀!它简直就是我们写Verilog 代码的神器。

所以,一定要好好掌握它呀!。

system verilog 实例化参数模块

system verilog 实例化参数模块如何在SystemVerilog中实例化参数化模块在SystemVerilog中,模块是一种组织硬件描述的方式。

参数化模块是一种允许用户在实例化时为模块参数传递值的工具。

在本篇文章中,我们将详细介绍如何在SystemVerilog中实例化参数化模块,并展示一些示例代码来帮助读者更好地理解。

参数化模块允许用户在实例化时为模块的参数传递不同的值。

这样可以根据实例化时提供的参数值,生成不同的硬件描述。

这对于设计具有不同配置或不同功能的模块非常有用。

参数化模块也可以提供一种动态生成硬件描述的方式。

首先,我们需要定义一个参数化模块。

在模块声明中,我们可以使用`#`符号来定义一个或多个参数。

例如,下面是一个具有两个参数的参数化模块的声明:systemverilogmodule MyParameterizedModule #(parameter WIDTH = 8, parameter DEPTH = 16) (input logic [WIDTH-1:0] data, input logic [DEPTH-1:0] address, output logic [WIDTH-1:0] output);模块的具体实现endmodule在这个例子中,我们定义了两个参数:`WIDTH`和`DEPTH`。

这些参数被用于定义`data`,`address`和`output`端口的位宽。

接下来,我们可以使用实际的参数值来实例化此参数化模块。

要在SystemVerilog中实例化一个参数化模块,我们需要在实例化语句中为参数提供值。

以下是一个实例化带有具体参数值的参数化模块的示例:systemverilogmodule MyTopModule;实例化参数化模块MyParameterizedModule #(8, 32)myInst(.data(in_data), .address(in_address), .output(out_data));顶层模块的其余部分endmodule在这个例子中,我们使用`(8, 32)`作为参数值实例化了`MyParameterizedModule`模块。

Verilog硬件描述语言(7)设计实例

[例5]. 3-8译码器设计实例(利用赋 值语句设计组合逻辑) module decoder(out,in); output [7:0] out; input [2:0] in; assign out = 1‘b1<<in;/**** 把最低位的1 左移 in(根据从in口输入的值)位,并 赋予out ****/ endmodule

多路器设计方案之三: module mux3( out, a, b, sel); output out; input a, b, sel; reg out; always @( a or b or sel ) begin if( sel ) out = a; else out = b; end endmodule

[例9]. 输出驱动器设计实例 三态输出驱动器设计方案之一: module trist1( out, in, enable); output out; input in, enable; assign out = enable? in: 'bz; endmodule

三态输出驱动器设计方案之二: module trist2( out, in, enable ); output out; input in, enable;

[例3].利用task和电平敏感的always块设 计比较后重组信号的组合逻辑. module sort4(ra,rb,rc,rd,a,b,c,d); parameter t=3; output [t:0] ra, rb, rc, rd; input [t:0] a, b, c, d; reg [t:0] ra, rb, rc, rd; always @(a or b or c or d) //用电平敏感的always块描述组合逻辑

Verilog的135个经典设计实例

Verilog的135个经典设计实例1、立即数放大器:立即数放大器是一种用于将输入电平放大到更高电平的电路,它可以实现任意输入到输出的映射,并且可以在Verilog中使用。

立即数放大器的Verilog实现如下:module immedamp(in, out);input in;output out;reg [3:0] immed;assign out = immed[3];begincase (in)4'b0000: immed = 4'b1000;4'b0001: immed = 4'b1001;4'b0010: immed = 4'b1010;4'b0011: immed = 4'b1011;4'b0100: immed = 4'b1100;4'b0101: immed = 4'b1101;4'b0110: immed = 4'b1110;4'b0111: immed = 4'b1111;4'b1000: immed = 4'b1000;4'b1001: immed = 4'b1001;4'b1010: immed = 4'b1010;4'b1011: immed = 4'b1011;4'b1100: immed = 4'b1100;4'b1101: immed = 4'b1101;4'b1110: immed = 4'b1110;4'b1111: immed = 4'b1111;endcaseendendmodule2、多路复用器:多路复用器是一种用于将多个输入选择转换为单个输出的电路,它可以实现由多种方式选择的输出,并可以使用Verilog实现。

verilog hdl语言100例详解

verilog hdl语言100例详解Verilog HDL语言是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它是硬件设计工程师在数字电路设计中的重要工具。

本文将介绍100个例子,详细解释Verilog HDL语言的应用。

1. 基本门电路:Verilog HDL可以用于描述基本门电路,如与门、或门、非门等。

例如,下面是一个描述与门电路的Verilog HDL代码:```verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule```2. 多路选择器:Verilog HDL也可以用于描述多路选择器。

例如,下面是一个描述2:1多路选择器的Verilog HDL代码:```verilogmodule mux_2to1(input a, input b, input sel, output y);assign y = sel ? b : a;endmodule```3. 寄存器:Verilog HDL可以用于描述寄存器。

例如,下面是一个描述8位寄存器的Verilog HDL代码:```verilogmodule register_8bit(input [7:0] d, input clk, input reset, output reg [7:0] q);always @(posedge clk or posedge reset)if (reset)q <= 0;elseq <= d;endmodule```4. 计数器:Verilog HDL可以用于描述计数器。

例如,下面是一个描述8位计数器的Verilog HDL代码:```verilogmodule counter_8bit(input clk, input reset, output reg [7:0] count);always @(posedge clk or posedge reset)if (reset)count <= 0;elsecount <= count + 1;endmodule```5. 加法器:Verilog HDL可以用于描述加法器。

verilog的15个经典设计实例

begin b=a; c=b; end endmodule

【例 5.11】模为 60 的 BCD 码加法计数器

module count60(qout,cout,data,load,cin,reset,clk);

【例 5.6】用 fork-join 并行块产生信号波形

`timescale 10ns/1ns module wave2; reg wave; parameter cycle=5; initial

fork wave=0;

#(cycle) wave=1; #(2*cycle) wave=0; #(3*cycle) wave=1; #(4*cycle) wave=0; #(5*cycle) wave=1; #(6*cycle) $finish; join initial $monitor($time,,,"wave=%b",wave); endmodule

else

out<=out+1;

end

endmodule

//同步复位 //计数

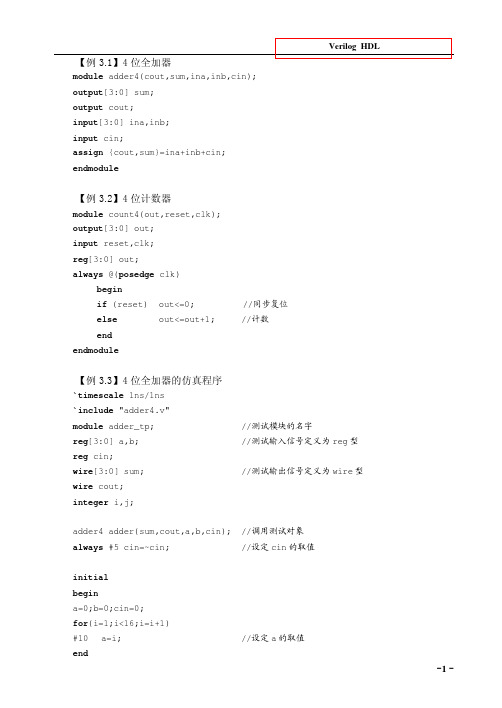

【例 3.3】4 位全加器的仿真程序

`timescale 1ns/1ns `include "adder4.v" module adder_tp; reg[3:0] a,b; reg cin; wire[3:0] sum; wire cout; integer i,j;

output[7:0] qout;

output cout;

input[7:0] data;

input load,cin,clk,reset;

用verilog-a写的一些电路模块的例子

用verilog-a写的一些电路模块的例子以下是几个用Verilog-A 语言编写的电路模块的例子:1. 增益电路模块````include "disciplines.vams"module gain_circuit(va, vb, vout, g);input va, vb;output vout;parameter real g=10.0;analog beginvout = g * (va - vb);endendmodule```这个例子展示了一个简单的增益电路模块,其中输入是两个电压va、vb,输出是vout,增益系数为g。

在模块中使用了Verilog-A 的`analog begin` 语句来定义电路的行为。

2. RC 低通滤波器模块````include "disciplines.vams"module rc_lowpass_filter(vin, vout, r, c);input vin;output vout;parameter real r=1.0, c=1e-6;real v1;analog begini(vin, v1) <+ (vin - v1)/(r*c);vout <+ v1;endendmodule```这个例子展示了一个基于RC 电路的低通滤波器模块,其中输入为vin,输出为vout,RC 电路的参数由r 和c 决定。

在模块中使用了Verilog-A 的`i()` 语句来定义电路的行为。

3. 三角波发生器模块````include "disciplines.vams"module triangle_wave_generator(vout, freq, amp, dc);output vout;parameter real freq=1e3, amp=1.0, dc=0.0;real t;analog begint = $abstime;vout <+ amp * (2 * (t * freq - floor(t * freq + 0.5)) - 1) + dc;endendmodule```这个例子展示了一个简单的三角波发生器模块,其中输出为vout,频率由freq 决定,幅值由amp 决定,直流分量由dc 决定。

Verilog模块的实例化

Verilog模块的实例化实例化语句1. 例化语法一个模块能够在另外一个模块中被引用,这样就建立了描述的层次。

模块实例化语句形式如下:module_name instance_name(port_associations) ;信号端口可以通过位置或名称关联;但是关联方式不能够混合使用。

端口关联形式如下:port_expr / / 通过位置。

.PortName (port_expr) / / 通过名称。

例[1]:....module and (C,A,B);input A,B;output C;...and A1 (T3, A, B ); //实例化时采用位置关联,T3对应输出端口C,A对应A,B对应B。

and A2(//实例化时采用名字关联,.C是and 器件的端口,其与信号T3相连.C(T3),.A(A),.B(B));port_expr 可以是以下的任何类型:1) 标识符(reg 或net )如 .C(T3),T3为wire型标识符。

2) 位选择,如 .C(D[0]),C端口接到D信号的第0bit 位。

3) 部分选择,如 .Bus (Din[5:4])。

4) 上述类型的合并,如 .Addr({ A1,A2[1:0]}。

5) 表达式(只适用于输入端口),如 .A (wire Zire = 0 )。

建议:在例化的端口映射中请采用名字关联,这样,当被调用的模块管脚改变时不易出错。

2. 悬空端口的处理在我们的实例化中,可能有些管脚没用到,可在映射中采用空白处理,如:DFF d1 (.Q(QS),.Qbar ( ),.Data (D ) ,.Preset ( ), // 该管脚悬空.Clock (CK)); //名称对应方式。

对输入管脚悬空的,则该管脚输入为高阻Z,输出管脚被悬空的,该输出管脚废弃不用。

3. 不同端口长度的处理当端口和局部端口表达式的长度不同时,端口通过无符号数的右对齐或截断方式进行匹配。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog多模块编程实例

1. 介绍

Verilog是一种硬件描述语言,被广泛应用于数字电路设计。

Verilog

具有模块化设计的特点,可以将一个大型的电路设计分解成多个小模块,然后逐个实现和调试。

本文将介绍Verilog多模块编程的实例,

以帮助读者了解如何使用Verilog进行模块化设计。

2. 模块化设计的优势

模块化设计是一种将大型系统分解成多个小模块的设计方法。

在Verilog中,模块化设计有以下几个优势:

- 提高代码可读性:通过将大型系统分解成多个小模块,可以提高代码的可读性和可维护性。

- 便于调试:每个小模块相对独立,可以单独调试和测试,提高了系统的可靠性和稳定性。

- 提高复用性:将功能相似的代码封装成模块,可以提高代码的复用性,减少代码冗余。

3. 多模块编程实例

接下来,我们将通过一个简单的数字电路设计来演示Verilog多模块

编程的实例。

假设我们要设计一个4位全加器电路,首先我们需要实

现一个单位全加器模块,然后将四个单元全加器模块连接成一个4位

全加器模块。

3.1 单位全加器模块

我们定义一个单位全加器模块,代码如下:

```verilog

module Adder_unit (

input a, b, cin,

output sum, cout

);

assign {cout, sum} = a + b + cin;

endmodule

```

在单位全加器模块中,我们定义了三个输入信号a、b、cin和两个输出信号sum、cout。

其中,sum表示相加的结果,cout表示进位。

在模块内部,我们通过assign语句实现了全加器的功能。

3.2 4位全加器模块

接下来,我们将四个单位全加器模块连接成一个4位全加器模块,代码如下:

```verilog

module Adder_4bit (

input [3:0] a, b,

input cin,

output [3:0] sum,

output cout

);

Adder_unit U0

(.a(a[0]), .b(b[0]), .cin(cin), .sum(sum[0]), .cout(cout0));

Adder_unit U1

(.a(a[1]), .b(b[1]), .cin(cout0), .sum(sum[1]), .cout(cout1)); Adder_unit U2

(.a(a[2]), .b(b[2]), .cin(cout1), .sum(sum[2]), .cout(cout2)); Adder_unit U3

(.a(a[3]), .b(b[3]), .cin(cout2), .sum(sum[3]), .cout(cout));

endmodule

```

在4位全加器模块中,我们首先定义了四个输入信号a、b和一个输入信号cin,以及四个输出信号sum和一个输出信号cout。

通过实例化四个单位全加器模块,并将它们连接成一个4位全加器模块。

4. 编译和仿真

完成了模块化设计后,我们可以对整个电路进行编译和仿真。

在Verilog中,可以使用常见的编译工具如Quartus、Vivado等对代码

进行编译,然后使用仿真工具进行波形仿真,验证电路设计的正确性。

5. 结论

本文介绍了Verilog多模块编程的实例,以帮助读者了解如何使用Verilog进行模块化设计。

在实际应用中,模块化设计是一种重要的设计方法,可以提高代码的可读性、可维护性和复用性。

希望本文能对

读者有所帮助,同时也欢迎读者在实践中进一步探索Verilog多模块

编程的技术。