PIC24系列单片机原理与开发

PIC单片机原理及应用

PIC 系列单片机代表着单片机发展的新动向

7 2021/4/20

PIC 单片机的特色

❖ 指令单字节化

数据总线和指令总线分离,ROM和RAM寻址空间互相独立, 宽度不同。 确保数据安全性、提高运行速度和实现全部指令单字节化。

MCS-51系列ROM和RAM都是8位,指令长度1~3字节,长短不一!

PIC12C50X/PIC16C5X 系列单片机的指令字节为12位; PIC16C6X/7X / 8X 系列单片机的指令字节为14位; PIC17CXX 系列单片机的指令字节为16位;

PIC 系列单片机代表着单片机发展的新动向

14 2021/4/20

PIC 单片机的特色

❖ I2 和 SPI 串行总线端口

I2(Inter IC Bus)和 SPI( Seril Peripheral Interface)是在 芯片之间实现同步串行数据传输的技术。方便灵活的扩展 外围器件,大大简化单片机应用系统的结构,极易形成产 品电路的模块化结构。 大屏幕彩电中都引入了I2技术。

26 2021/4/20

PIC12F629/675系统结构与工作原理

❖ PIC12F629/675简化结构框图

T1G T1CKI T0CKI

Flash程序 存储器 1K * 14

程序计数器PC 8级堆栈13位

RAM 寄存器 64*8

GP0/AN0/CIN+

指令寄存器 内部

4MHz 振荡器

指令译码 与控制

PIC单片机原理及应用

2005.12

1 2021/4/20

内容提要

单片机概述 PIC单片机的特色 PIC单片机的程序设计

2 2021/4/20

单片机概述

PIC24系列单片机原理与开发 第6章 AD转换器及编程

R/W -0

U-0

U-0

R/W-0

U-0

U-0

VCFG<2:0>

未用

未用

CSCNA

未用

未用

bit 15

bit 8

R -0

BUFS bit 7

U-0 未用

R/W -0

R/W -0

R/W -0

SMPI<3:0>

R/W-0

R/W -0 BUFM

R/W -0 ALTS bit 0

其中: U=未用(读为0),R=可读, W=可写,-n =上电复位值

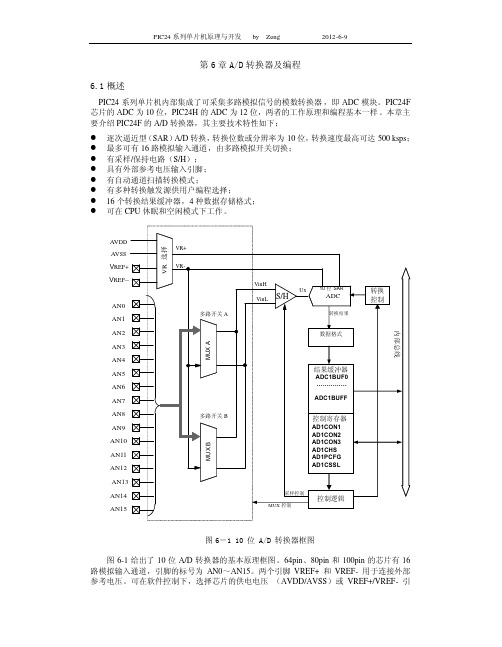

逐次逼近型(SAR)A/D 转换,转换位数或分辨率为 10 位,转换速度最高可达 500 ksps; 最多可有 16 路模拟输入通道,由多路模拟开关切换; 有采样/保持电路(S/H); 具有外部参考电压输入引脚; 有自动通道扫描转换模式; 有多种转换触发源供用户编程选择; 16 个转换结果缓冲器,4 种数据存储格式; 可在 CPU 休眠和空闲模式下工作。

采样完成后,应启动 A/D 转换。PIC24F 提供有 4 种启动 A/D 转换的方式,由位域 SSRC<2:0>的赋值确定。对于自动转换方式(SSRC<2:0>=“111”),采样时间由寄存器 AD1CON3 中的设置值(1~31 个 A/D 的时钟周期 TAD)所确定,采样完毕硬件自动启动 A/D 转换。另 外 3 种结束采样且启动 A/D 转换的方式为:定时器 Timer3 发生匹配时、INT0 引脚产生有 效电平和清零 SAMP 位。对于它们的编程将在下面的应用例程中给予进一步说明 。

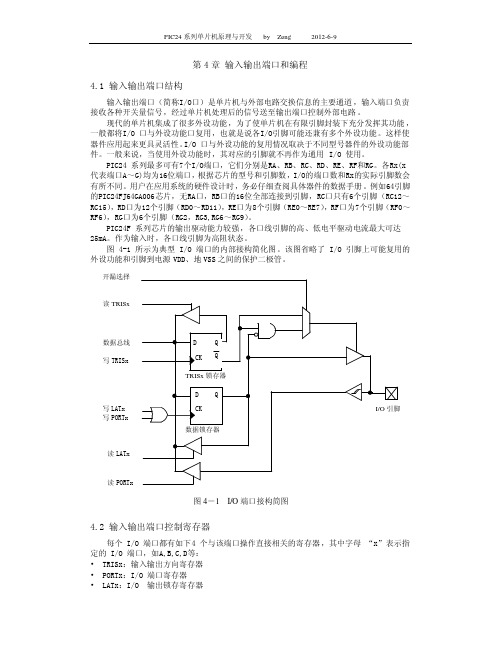

PIC24系列单片机原理与开发 第4章 输入输出端口和编程

读 PORTx 寄存器就是读取 I/O 引脚上的数据值。 读 LATx 寄存器就是读取保存在该端口锁存器中的数据值 。 写 PORTx 寄存器就是将数据值写入该端口锁存器 ,但可能出现“读-修改-写”操

作问题。

写 LATx 寄存器就是将数据值写入该端口锁存器 ,无“读-修改-写” 操作问题。 PIC24 系列的寄存器为16位,对于具体型号器件而言,有些I/O端口的引脚不存在。对 于该芯片不存在的端口,其相关的数据和控制寄存器都被禁止 ,这意味着对应的 LATx和 TRISx 寄存器以及该端口引脚将读为“0”。

PIC24 系列单片机原理与开发 by Zeng

2012-6-9

• ODCx:I/O 开漏控制寄存器 芯片的每个 I/O 引脚在 TRISx、 PORTx、 LATx 和 ODCx 寄存器中都分别有一个相关

的位。例如引脚 RB2(pin14)是 B 口的 D2 位,其对应方向寄存器 TRISB 的 D2 位、端口寄 存器 PORTB 的 D2 位、输出锁存寄存器寄存器 LATB 的 D2 位、开漏控制寄存器 ODCB 的 D2 位。

ODCx

开漏控制寄存器, R/W-0

复位:各位均为“0”

4.2.1 输入输出方向寄存器 TRISx

方向寄存器TRISx的各位控制端口 x各个引脚是作为输入还是输出 ,即控制端口数据的传 输方向。如果x端口的 I/O 引脚所对应的 TRISx 位为 1,则该引脚是输入引脚。如果某个 I/O 引脚的 TRISx 位为 0,则该引脚被配置为输出,引脚为输出锁存寄存器的状态。这种 设计完全继承了PIC系列单片机的一贯方法。也比较容易记忆,因为 “1” 很像字母“I ” (Input,输入),“0” 很像字母“O”(Output,输出),一目了然。I/O端口的各引脚 均可单独配置成输入或输出 。复位后,所有端口引脚都被定义为输入 。

I2C24LC02C读写例程(PIC单片机)

I2C24LC02C读写例程(PIC单片机)I2C 24LC02 C读写例程(PIC单片机)[单片机]发布时间:2008-04-22 10:11:001 I2C总线特点I2C总线最主要的优点是其简单性和有效性。

由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。

总线的长度可高达25英尺,并且能够以10Kbps的最大传输速率支持40个组件。

I2C总线的另一个优点是,它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线。

一个主控能够控制信号的传输和时钟频率。

当然,在任何时间点上只能有一个主控。

2 I2C总线工作原理I2C总线上的数据稳定规则,SCL为高电平时SDA上的数据保持稳定,SCL为低电平时允许SDA变化。

如果SCL处于高电平时,SDA 上产生下降沿,则认为是起始位,SDA上的上升沿认为是停止位。

通信速率分为常规模式(时钟频率100kHz)和快速模式(时钟频率400kHz)。

同一总线上可以连接多个带有I2C接口的器件,每个器件都有一个唯一的地址,既可以是单接收的器件,也可以是能够接收发送的器件。

每次数据传输都是以一个起始位开始,而以停止位结束。

传输的字节数没有限制。

最高有效位将首先被传输,接收方收到第8位数据后会发出应答位。

数据传输通常分为两种:主设备发送从设备接收和从设备发送主设备接收。

这两种模式都需要主机发送起始位和停止位,应答位由接收方产生。

从设备地址一般是1或2个字节,用于区分连接在同一I2C上的不同器件。

I2C总线在传送数据过程中共有三种类型信号,它们分别是:开始信号、结束信号和应答信号。

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的IC在接收到8bit数据后,向发送数据的IC 发出特定的低电平脉冲,表示已收到数据。

PIC24系列单片机原理与开发第6章AD转换器及编程

PIC24系列单片机原理与开发第6章AD转换器及编程AD转换器是一种用于将模拟信号转换为数字量的设备,它的主要用途是将模拟量转换为可用于数字控制系统的数字信号。

PIC24系列单片机内置了多路/低速模拟输入AD转换器,可以实现对模拟量的采集、处理和控制。

AD转换器的编程十分复杂,需要明确程序对模拟量的要求,包括采样率、量程、精度等,还需要根据PIC24系列单片机的资源情况,合理配置AD转换器的参数,以便实现模拟量的有效读取。

1)可以多路采样:多路采样可以提高采样精度,在故障时可以减少恢复时间,还可以提高采样率。

2)采样率:根据实际应用需要,调整单片机的时钟频率,来达到最佳的采样率。

3)精度范围:根据实际应用需要,调整AD转换器的精度范围,以保证采集到的数据和处理能力的均衡使用。

4)通道选择:根据实际应用,选择多路采样中的其中一路,来使用最佳的采样精度。

PIC24系列单片机原理与开发 第3章 时钟和系统管理

设所需的配置为: 禁双速启动,使用主振荡器和 PLL 四倍频, OSC1 与 OSC2 引脚接 8MHz 的 XT 晶振,禁时钟切换和保护监视。 在程序中加入下面的芯片配置字 2 的宏便可实现所需配 置。 _CONFIG2(IESO_OFF & FNOSC_PRIPLL & FCKSM_CSDCMD & POSCMOD_ XT) 若配置改为使用片内快速RC振荡器(8MHz,不分频) 和PLL四倍频, 禁止主振荡器, 其余不 变,则芯片配置字2的宏为: _CONFIG2(IESO_OFF & POSCMOD_NONE & FCKSM_CSDCMD & FNOSC_FRCPLL) 因为没有启用主振荡器,因此 OSC1 与 OSC2 引脚可作 I/O 用。 说明:1. 当配置为禁止主振荡器时(POSCMD<1:0> = 11,宏定义为POSCMOD_NONE) ,引脚 OSC1 和 OSC2自动配置成数字I/O功能(RC12和RC15)。 2. 当主振荡器配置为 外部时钟 的EC 模式时 (POSCMD<1:0> = 00,宏定义为 POSCMOD_EC),外部时钟接OSC1引脚,若将 OSCIOFCN位(配置字2<5>)编程为0或引用 宏定义OSCIOFNC_ON,OSC2引脚仍可以为数字I/O,否则OSC2引脚上为Fosc/2 时钟输出, 可用于系统时钟测试或同步。

PIC24 系列单片机原理与开发

by

Zeng

2012-6-9

如下: (1)在 OSCCON 寄存器解锁和写序列期间禁止中断 。 (2)用两条字节传送指令将 78h 和 9Ah 写入 OSCCON<15:8>, 以执行 OSCCON 高字节的 解锁序列。 (3)紧接上面解锁序列之后将新的振荡器源写入 NOSC<2:0>。。 (4)用两条字节传送指令将 46h 和 57h 写入 OSCCON<7:0>,以执行 OSCCON 低字节的 解锁序列。 (5)紧接着将 OSWEN 位置 1。 (6)调用软件延时,使选中的振荡器和/或 PLL 启动并稳定。 (7)检查 OSWEN 位是否为 0,如果为 0,则说明切换成功。 下面是解锁 OSCCON 寄存器和启动时钟切换的核心序列 。 例 3-1:时钟切换的基本代码序列 .global _Exam3_1 _Exam3_1: ;W0<2:0>为新的振荡器选择 PUSH SR ;状态寄存器入栈 MOV #0x0e0,w1 ;准备使 IPL<2:0>=0b111, MOV w1,SR ;CPU 中断优先级 7,禁止所有可屏蔽中断 MOV #OSCCONH,w1 ;OSCCONH (OSCCON 寄存器的高字节) 解锁序列 MOV #0x78, w2 MOV #0x9A, w3 MOV.b w2, [w1] MOV.b w3, [w1] MOV.b WREG, OSCCONH ;设置新的振荡器选择 MOV #OSCCONL,w1 ;OSCCONL(OSCCON 寄存器的低字节) 解锁序列 MOV #0x46, w2 MOV #0x57, w3 MOV.b w2, [w1] MOV.b w3, [w1] BSET OSCCON,#0 ; 启动时钟切换 POP SR ; 恢复状态寄存器 RETURN 上面的汇编子程序作为 C 函数调用的格式为: void Exam3_1(int X)。参数 X 的 bit2:0= 新振荡器选择位 NOSC<2:0>。例如将系统时钟切换成带分频的 FRC 为: Exam3_1(0b 111); 在基本序列完成后,系统时钟硬件按以下方式自动响应 : (1)若 COSC<2:0>位与 NOSC<2:0>位的值相同,则不进行切换操作,OSWEN 位自动清零, 时钟切换终止。 (2)如果启动了有效的时钟切换,则 LOCK 位(OSCCON<5>)和 CF 位(OSCCON<3>)清零。 (3)如果新的振荡器当前未运行 ,硬件会自动启动它。如果启动晶体振荡器,则硬件将等 待到振荡器起振定时器( OST)计时期满。如果新的振荡器源使用 PLL,则硬件将等待 到 PLL 锁定(位 LOCK = 1)。 (4)硬件等待新的时钟源达到稳定 ,然后执行时钟切换。 (5)硬件清零 OSWEN 位,指示时钟切换成功,并且 COSC<2:0>更新成 NOSC<2:0>位的值。 (6 ) 关闭旧时钟源。但是若旧时钟源是下面两种情况时例外 :若闪存配置字 1 中使能 WDT

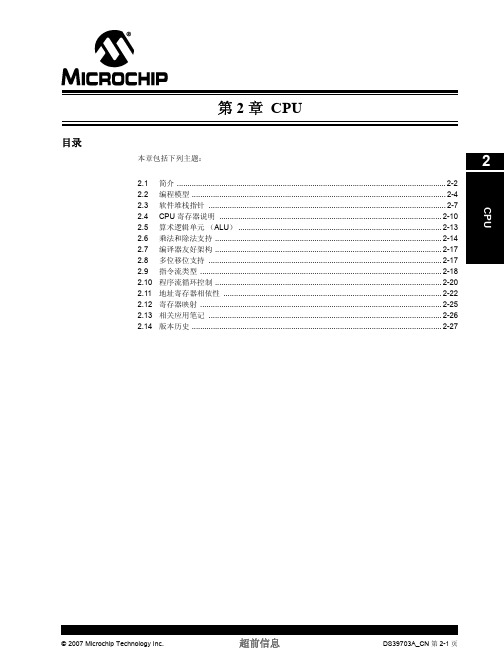

pic24各个模块数据手册(中文)2章cpu

© 2007 Microchip Technology Inc.

超前信息

DS39703A_CN 第 2-1 页

PIC24F 系列参考手册

2.1

简介

PIC24F CPU 模块采用 16 位(数据)改良的哈佛架构,并带有增强型指令集。CPU 具有 24 位指令 字,指令字带有长度可变的操作码字段。程序计数器(Program Counter,PC)为 24 位宽,可以寻 址高达 4M x 24 位的用户程序存储空间。单周期指令预取机制用来帮助维持吞吐量并提供可预测 的指令执行过程。除了改变程序流的指令、双字移动 (MOV.D)指令和表指令以外,所有指令都 在单个周期内执行。模块使用 REPEAT 指令支持无开销的程序循环结构,该指令在任何时候都可 被中断。

指令集架构 (Instruction Set Architecture, ISA)在 PIC18F 指令集架构的基础上有显著增强, 但仍在可接受程度上保持了向后兼容性。所有 PIC18F 指令和寻址模式都能直接得到支持或通过 简单的宏得到支持。许多 ISA 增强功能都是为了提高编译器效率而做出的。

内核支持固有(无操作数)、相对、立即数和存储器直接寻址模式,以及 3 组寻址模式(MODE1、 MODE2 和 MODE3)。所有模式都支持寄存器直接和各种寄存器间接寻址模式。每组都提供最多 7 种寻址模式。指令根据其功能要求,与预定义的寻址模式相关联。

PIC24F 指令集可被分成两种指令类型:寄存器和文件寄存器指令。寄存器指令可以把每个 W 寄 存器用作数据值或地址偏移值。例如:

例 2-1:

寄存器指令

MOV

W0, W1

; move contents of W0 to W1

MOV

pic24各个模块数据手册(中文)14章timer

未实现:读为 0

TSIDL: 空闲模式停止位

1 = 当器件进入空闲模式时,定时器停止工作 0 = 在空闲模式下定时器继续工作

未实现:读为 0

TGATE:Timerx 门控时间累加使能位

当 TCS = 1 时: 该位为无关位。

当 TCS = 0 时: 1 = 使能门控时间累加 0 = 禁止门控时间累加

C 类型定时器框图

TxCK(1)

同步

TON 1x

01

TCKPS1:TCKPS0 2

预分频器 1, 8, 64, 256

TxIF 事件标志

TGATE

1 0

复位

TCY QD Q CK

TMR3(TMR5)

ADC 事件触发信号 *

相等

比较器

00

TCS TGATE

PR3(PR5)

* ADC 事件触发信号仅在 Timer4/5 上可用。

TCS:Timerx 时钟源选择位

1 = 来自 TxCK 引脚的外部时钟 0 = 内部时钟 (FOSC/2)

未实现:读为 0

U-0 —

bit 8

U-0 —

bit 0

DS39704A_CN 第 14-6 页

超前信息

© 2007 Microchip Technology Inc.

图 14-2:

14.2.2 B 类型定时器

在大多数 PIC24F 器件上,如果存在 Timer2 和 Timer4,它们是 B 类型定时器。与其他类型的定 时器相比, B 类型定时器有下列独特的功能: • B类型定时器可以和C类型定时器相连形成32位定时器。B类型定时器的TxCON寄存器具有

T32 控制位,用来使能 32 位定时器功能。 • B 类型定时器的时钟同步在预分频逻辑后执行。关于将时钟同步放在预分频逻辑后执行的益

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

端口 RB 的基本功能为可编程的输入输出双向口,此外也可工作在它的第 2,3 等功能 PGD1/EMUD1/PMA6/VREF+/AN0/CN2/RB0 PGC1/EMUC1/VREF-/AN1/CN3/RB1 C2IN-/AN2/SS1/CN4/RB2 C2IN+/AN3/CN5/RB3 C1IN-/AN4/CN6/RB4 C1IN+/AN5/CN7/RB5 PGC2/EMUC2/AN6/OCFA/RB6 PGD2/EMUD2/AN7/RB7 U2CTS/C1OUT/AN8/RB8 PMA7/C2OUT/AN9/RB9 TMS/PMA13/CVREF/AN10/RB10 TDO/PMA12/AN11/RB11 TCK/PMA11/AN12/RB12 TDI/PMA10/AN13/RB13 PMA1/U2RTS/BCLK2/AN14/RB14 PMA0/AN15/OCFB/CN12/RB15 16 15 14 13 12 11 17 18 21 22 23 24 27 28 29 30 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O

有 有 有 有 有 有 有 有 有

PIC24FJ128GA010 100 128K

JTAG

PIC24 系列单片机原理与开发 by Zeng

2012-6-8

1.3

PIC24FJ64GA006 引脚图和引脚功能说明

在单片机应用系统中,需通过单片机引脚与系统中的信息进行交换,即输入输出,来实现系 统硬件的所需的各种功能。因此作为设计者需要详细了解单片机的每个引脚的功能 ,这样才能正 确、灵活地设计单片机应用系统的硬件和软件 。PIC24F 系列单片机所集成的外设功能很多 ,大部 分引脚复合了多种功能。PIC24FJ64GA006 单片机是 64 引脚薄型正方扁平封装 (12x12x1 mm), 其引脚排列如图 1-3 所示。

① ② ③ ④ ⑤ ⑥ ⑦ ⑧ ⑨ PIC 24 FJ 64 GA0 06 T -I/PT

Microchip 商标 16 位改进哈佛架构 Flash 存储器系列 程序存储器容量 (64KB) 产品类:通用单片机 引脚数(64pin) 盘带装标志 温度范围 (工业级) 封装形式(TQFP) 图 1- 2 PI C24F 系列单片机的命名 规则 命名的第 2 部分为 CPU 架构,“24”为不带 DSP 功能的 16 位改进型哈佛架构。第 4 部分数 字为 Flash 存储器容量,单位为 k 字节,有 16/32/64/128/256 等供选择。第 6 部分表示引脚数: 02-28 引脚, 04-44 引脚, 06-64 引脚,08-80 引脚,10-100 引脚。 温度范围-40°C 至 85°C。 例如上图所示的 PIC24FJ64GA006 单片机,Flash 程序存储器的容量为 64k 字节, 芯片引脚数 为 64。型号为 PIC24FV16KA301 芯片,是工作电压为 2.0V 至 5.5V 的超低功耗单片机,Flash 程 序存储器的容量为 16k 字节,芯片引脚数为 20。型号为 PIC24FJ256GB110 芯片,是带 USB On-The-Go(OTG)模块的通用单片机。Flash 程序存储器的容量为 256k 字节,芯片引脚数为 100。 型号为 PIC24FJ128DA210 芯片,是具有图形控制器和 USB On-The-Go 模块的通用单片机,Flash 程序存储器的容量为 128k 字节,芯片引脚数为 100/121。 本书将以 PIC24FJ64GA006 单片机为例,介绍 PIC24F 系列单片机的结构、工作原理、各功能 模块(外设)的编程。PIC24FJ64GA006 属于 PIC24FJ128GA(子)系列,该系列共有 9 款型号,它 们的外设功能和 RAM 容量相同,区别在于芯片的引脚数和 Flash 存储器容量,如表 1-1 所示。

64 64 64 80 80 80 100 100

5 5 5 5 5 5 5 5 5

5 5 5 5 5 5 5 5 5

2 2 2 2 2 2 2 2 2

2 2 2 2 2 2 2 2 2

2 2 2 2 2 2 2 2 2

16 16 16 16 16 16 16 16 16

2 2 2 2 2 2 2 2 2

定时器 1

定时器 2/3

定时器 4/5

输入捕捉 IC1-5

输出比较 OC1-5/PWM

电平变化通 知 CN0-23

图 1-1 PIC24F 系列单片机的结构框图

PIC24 系列单片机原理与开发 by Zeng

2012-6-8

1.2

PIC24F 产品系列

PIC24F 系列单片机的命名规则如图 1-2 所示.

MCLR

OSC1/CLKI/RC12 OSC2/CLK0/RC15

PIC24 系列单片机原理与开发 by Zeng

2012-6-8

引脚名称 VCAP/ VDDCORE

引脚号 56

类型 P

功能 接外部滤波电容(片内稳压器已使 能) /单片机内核逻辑的正电源 (片 内稳压器禁止)

ENVREG

57

I

片内稳压器使能端。 通常接高电平, 单片机内核使用片内稳压器。

OSC2/CLKO OSC1/CLKI FRC/LPRC 振荡器 高精度带 隙参考源 ENVREG 稳压器 上电延迟 定时器 振荡器延 迟定时器 上电复位 看门狗 定时器 欠压复位 指令寄存器 指令译码器 控制逻辑 支持除法 17x17 乘法器 工作寄存器 W0~W16 16 地址 MUX

端口 G

16 位 ALU VDDCORE/VCAP VDD,VSS MCLR 实时时钟 日历 16 16 路 10 位 AD 模拟比较 器 PMP/PSP IIC1 IIC2 UART1 UART2 SPI1 SPI2

PIC24 系列单片机原理与开发 by Zeng

2012-6-8

外设特性: 2 个 3 线/4 线 SPI 模块,利用 4 级 FIFO 缓冲器支持 4 种帧模式; 2 个 IIC 模块,支持多主 /从动模式和 7 位/10 位寻址; 2 个串行通信 (UART) 模块, FO 缓冲器;利 用片上硬件编码解码器支持 IrDA。 并行主/从端口(PMP/PSP):支持 8 位或 16 位数据,支持 16 条地址线 硬件实时时钟 /日历(Real-Time Clock/Calendar ,RTCC):提供时钟、日历和闹钟功能; 5 个带可编程预分频器的 16 位定时器 /计数器,并可组合成 32 位的定时器/计数器; 5 个 16 位捕捉输入,5 个 16 位比较/PWM 输出; I/O 口的驱动能力可达 18mA,可配置为漏极开路输出; 5 个外部中断源。 可以选择多达 24 个输入引脚来产生电平变化中断(CN )中断。

表1-1 PIC24FJ128GA 系列芯片 器 件 引 脚 程 16 SRAM 序 位定 存 (字节) 时器 储 器 (字 节) 64K 96K 128K 64K 96K 128K 64K 96K 8K 8K 8K 8K 8K 8K 8K 8K 8K 5 5 5 5 5 5 5 5 5 比较 / PWM 输出 SPI UART I2C™ 10 位 A/D (通道数)

PIC24 系列单片机原理与开发 by Zeng

2012-6-8

第 1 章 PIC24 系列单片机 概述

1.1 PIC24 系列单片机的功能和特点

PIC24 系列单片机是美国微芯科技公司 (Microchip Technology Inc. )近年来推出的 16 位 精简指令集(RISC)微控制器(MCU), 其具有高速度、低工作电压、低功耗、较大的输出驱动能力 和丰富的外设功能以及增强的计算性能 ,并且继承了 PIC16/18 系列 MCU 的高抗干扰性能和较低 的价位等特点。对于嵌入式产品的升级换代和那些用 8 位单片机难以满足性能要求,且性价比上 又不宜采用数字信号处理器的高性能 嵌入式应用,PIC24 系列单片机无疑是设计者的首选 。 PIC24 系列又分为 PIC24F 系列和与 PIC24H 系列。 PIC24F 和与 PIC24H 系列在硬件(包括对应 型号的引脚)和软件上完全兼容, 使用的开发工具也可完全相同,但 PIC24H 的工作速度比 PIC24F 更快,且其 AD 转换可 12 位,其外围设备有 DMA 传输方式,当然价格也较 PIC24F 高。 PIC24F 系列单片机有多达几十种型号供选择 ,引脚从 14pin 到 100pin,Flash 程序存储器从 4kB 到 256kB,RAM 从 512 字节到 16kB, 可以满足不同的嵌入式产品设计需求 。 PIC24F 的功能框图 如图 1-1 所示,归纳起来 PIC24F 系列单片机有如下主要特点(PIC24FJ128GA 系列): CPU 特性 系统时钟可达 32MHz,指令执行速度可达 16MIPS(百万条指令 /秒); 8MHz 内部振荡器,可 PLL(锁相环)4 倍频,并具有多个倍频选项; 17 位 x17 位单周期硬件乘法器; 32 位/16 位硬件除法器; 16 个 16 位的工作寄存器阵列; 优化的 C 编译器指令集架构:76 条基本指令,灵活的寻址模式; 程序存储器寻址空间可达 12MB; 数据存储器寻址空间可达 64KB; 两个地址发生单元可分别对数据存储器执行 读和写寻址。 模拟特性: 16 通道,10 位模数转换器,转换速率 500ksps,在休眠和空闲模式下也可进行转换; 具有可编程输入 /输出配置的模拟比较器。 单片机的特殊性能: 工作电压范围为 2.0V 到 3.6V; Flash 程序存储器的擦 /写次数达 1000 次(PIC24FJ128GA 系列典型值),用户软件可自 行编程擦 /写; 具有低功耗管理模式:休眠模式、空闲模式和备用时钟模式; 故障保护时钟监视器工作:当检测到时钟故障时, 可将时钟源切换到片内低功耗 RC 振荡 器; 可使用片内低压差线性稳压器(LDO)给单片机内核供电; 支持 JTAG 边界扫描和编程; 上电复位(Power-on Reset,POR)、上电延时定时器(Power-up Timer,PWRT)和振荡 器起振定时器(Oscillator Start-up Timer,OST); 灵活的可编程看门狗定时器(Watchdog Timer ,WDT)和片上低功耗 RC 振荡器可保证 器件可靠工作; 通过 2 个引脚可实现在线串行编程 (In-Circuit Serial Programming ,ICSP)和在线仿真 (In-Circuit Emulation ,ICE)。