中科院微电子成功研发30Gsps 6bit超高速ADC和DAC

基于FMC标准的DRFM设计

基于FMC标准的DRFM设计作者:潘勇先陈勇来源:《电子技术与软件工程》2015年第21期摘要本文给出了一种基于FMC标准的DRFM数字板卡设计。

母板上集成了一款高性能的FPGA,ADC、DAC分布在独立的小子板上,它们之间通过FMC连接器互联。

高速ADC 实现模拟信号的中频采样,DAC完成干扰信号的中频输出功能,FPGA负责相关的处理、运算及时序控制。

ADC采样频率为5GHz,波形的转换率也达到4GHz,可广泛应用于电子战和宽带数字接收机中。

【关键词】DRFM FMC ADC DACDRFM技术作为现代电子战前沿技术之一,对电子对抗领域发生了深远的影响。

DRFM 存储器是以高速采样、存储、宽带波形为技术基础,捕获、存储、处理雷达信号后,就能实现各种欺骗干扰,它能同时对抗多个威胁目标,并能够灵活的产生各种的干扰样式。

本文设计的ADC采样频率高达5Gsps,波形的转换率达到4Gsps,可以被广泛应用于在各种干扰器和数字接收机系统中。

1 DRFM工作原理接收机对射频信号经过放大、滤波、下变频到适合ADC量化的中频信号,高速数据采集以中频采样方式完成模拟信号的数字量化,高速采集的性能决定了DRFM的接收带宽。

数字样本信号被存储在存储器中,在需要时可随时读取出来并加适当的处理,然后由高速数/ 模转换器转换为模拟信号,再经激励上变频变频到所需频段,最后送发射机释放有效干扰。

波形的性能决定了DRFM的干扰瞬时带宽。

波形、采集及运算能力联合决定了DRFM的瞬时带宽。

2 硬件设计FMC(FPGA Mezzanine Card)接口总线技术是VME国际贸易协会(VITA)组织近年来提出,由ANSI发布的的一种全新的专门针对FPGA的高速子板接口,旨在满足更大的传输带宽以及更多的I/O接口需求。

基于FMC设计的DRFM有很好的扩展和可更换性,为满足不同带宽和样式的需求,只需考虑更换相应的ADC或DAC子板即可,这也大大缩短研发周期与成本。

基于JESD204B协议的ADC高速串行接口设计与实现

• 130•引言:在第五代移动通信中,高性能ADC 、DAC 器件是其发展的核心器件。

随着高速ADC 器件的发展,采样率已跨入GSPS 范围,采样精度也提升到了14bit 甚至16bit 。

随着采样速率的不断提高,数据位宽的逐渐加大,基于LVCOMS 、LVDS 的并行ADC 、DAC 传输技术暴露出信号同步困难,偏移大,抗干扰能力弱,布局布线困难等问题。

研制更新型的高速接口成为了解决问题的关键。

由JEDEC 国际组织推出的JESD204B 系列协议成为解决高速转换器和FPGA 之间数据传输问题的接口协议。

与传统的并行总线相比,JESD204B 高速串行接口具有以下优势:(1)提高了数据传输速率;(2)减少了引脚数目,使ADC 的封装变小;(3)简化了布局布线;(4)使用了CML 电平后,功耗更小。

目前,以ADI 、TI 为代表的众多厂家已生产了多款具有JESD204B 接口的高速AD ,同时,FPGA 公司XILINX 和Altera 就JESD204B 接口提供了专门的IPcore 供用户使用。

本文以A D 9680芯片为例,该芯片为一款双通道,支持最高采样率为1.25GSPS ,精度为14bits 的ADC ,详细描述了基于XILINX 公司KU 系列FPGA 的JESD204B IP Core 的逻辑实现,完成仿真验证,并在硬件电路板上完成实测,结果正确,可满足工程使用要求。

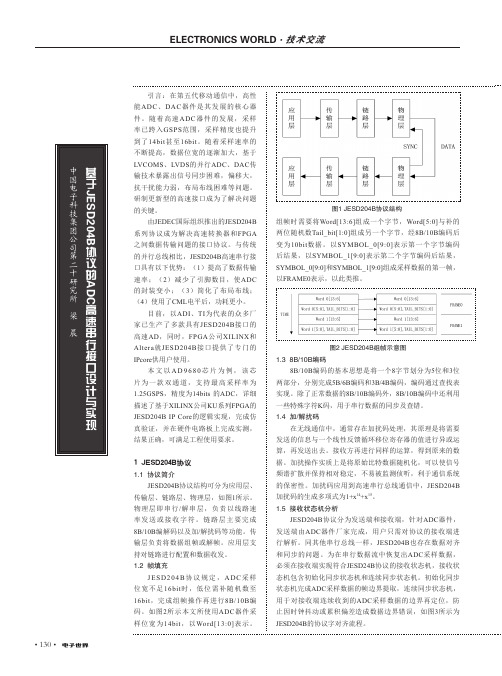

1 JESD204B协议1.1 协议简介JESD204B 协议结构可分为应用层、传输层、链路层、物理层,如图1所示。

物理层即串行/解串层,负责以线路速率发送或接收字符。

链路层主要完成8B/10B 编解码以及加/解扰码等功能。

传输层负责将数据组帧或解帧。

应用层支持对链路进行配置和数据收发。

1.2 帧填充J E S D 204B 协议规定,A D C 采样位宽不足16bit 时,低位需补随机数至16bit ,完成组帧操作再进行8B/10B 编码。

高速ADC_DAC设计论坛回顾

高速ADC/DAC 设计论坛回顾上网时间:2006年07月21日 打印版推荐给同仁发送查询 /AR T_8800015964_400001_500002_TS.H TM随着数字信号处理技术的迅速发展以及数字信号处理器件性能的全面提高,实际系统对高速数据转换器的要求也越来越高。

例如,在移动通讯基站设计中,高速数据转换器不仅要有很高的转换速度,而且还需要对高频信号具有很小的噪音失真,以免小信号被频率相近的大信号所掩盖。

对于数码相机和摄像机等图像采集和显示应用,为减少体积、成本并延长电池使用时间,高速数据转换器的小体积和低功耗也凸现重要。

这些都对采用高速A/D 、D/A 转换器的电子系统设计提出了更多挑战。

在《电子系统设计》专题论坛中,我们邀请到了两位高速A/D 、D/A 转换器方面的技术专家担任嘉宾主持,一位是AD I 公司副总裁Lew is Counts 先生,另一位是美信集成产品公司的业务发展经理何浩然先生。

以下是读者就高速A/D 、D/A 转换器的应用设计提出的问题以及专家的精彩回复。

Q1:在PCB 板上进行高速ADC/DAC 的走线和布线时应该特别注意哪些因素?如何使与邻近高速ADC/DAC 通道的电磁干扰最小?MAXIM 专家:1.通常情况下,带有完整地平面和电源平面的多层板的信号完整性最高。

转换器要求高速电路板布局设计技术,包括将裸焊盘连接到完整地平面。

2.使转换器模拟区域的内层地平面保持完整,只有极小空隙。

交错排列的过孔采用非常小的孔焊盘径等方法来使过内层空隙最小。

另外,使完整的地层在关键元件的下面。

3.详细规划不同的输入和输出信号在层上的布局,包括X 层上的所有模拟输入、Y 层上的所有数字输出以及Z 层上的所有时钟等。

然后尽量使每个层都夹在两个完整地平面之间,或者做成微带线。

4.电源层与地层成对放置,以使这些信号的电感最小并使总体噪声最小。

如果使用电源走线,则这些走线应足够宽,以使电压降和电感最小。

CSD17308超高速大电流30V耐压N沟道MOS

MIN TYP MAX UNIT 4.5 °C/W 58 °C/W

(1) RqJC is determined with the device mounted on a 1-inch2 (6.45-cm2), 2-oz. (0.071-mm thick) Cu pad on a 1.5-inch × 1.5-inch (3.81-cm × 3.81-cm), 0.06-inch (1.52-mm) thick FR4 PCB. RqJC is specified by design, whereas RqJA is determined by the user’s board design.

2

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

RDS(on) Drain to Source On Resistance

gfs

Transconductance

Dynamic Characteristics

CISS COSS CRSS Rg Qg Qgd Qgs Qg(th)

Input Capacitance Output Capacitance Reverse Transfer Capacitance Series Gate Resistance Gate Charge Total (4.5V) Gate Charge Gate to Drain Gate Charge Gate to Source Gate Charge at Vth

ADC入门基础知识

第30页/共67页

逐次逼近型ADC结构图

30

第31页/共67页

逐次逼近型ADC的适用系统

逐次逼近型ADC的转换周期是从采样模拟信号开始的, 采样值与DAC初始化输出结果相减,输出的差被比较器量化, 该比较器通过输出的结果指示SAR增加还是减小DAC的输出, 然后输入采样减去新的DAC输出,该过程一直重复,直到满足 所要求的精度为止。

逐次逼近型ADC完成n位数字转换需要N个时钟周期来完 成。因此,当分辨率提高时,转换器的速度就会相应的降低。

逐次逼近型ADC的静态误差会受到DAC线性度的限制,通

过校准或者微调DAC可以获得非常高的分辨率。

因 此 逐 次 逼 近 型 A D C 常第3用2页于/共6高7页分 辨 率 、 低 速 的 系 统 及 设

我国从 70 年代开始研制 ADC,至今已经有 8 bit、10 bit、12 bit、14 bit 的 ADC产品,但产品性能还远远达不 到高端应用的要求,与国外水平相差甚远;高端 ADC还处于 高校和研究所的研究开发阶段。

6ቤተ መጻሕፍቲ ባይዱ

第7页/共67页

低功耗、低电压、单片化

单元电路的一些优化设计也可以降低功耗,如动态偏置、开关电容动态共模反馈以及动态比较器等。低 电压是现在应用发展的一个趋势,主要有运放的rail-to-rail设计、模拟开关的电压自举等方法。

背景、发展

随着CMOS制作工艺的迅猛发展,越来越多的信号被移到数字领域来处理,从而达到降低成本,降低功 耗,提高速度的目的。

这就使我们迫切需要一种低功耗、低电压而且能够用标准深亚微米技术实现的ADC。

1

第2页/共67页

现状

国内在高性能芯片的研究和设计方面还比较 落后,这就造成了各种高性能芯片的巨大需求和 国内芯片产业落后之间的巨大矛盾。而且,由于 一些高端芯片产品受到国外的进口限制,这对我 国国防现代化发展以及民用电子通信工业的发展 非常不利。这就迫使我们必须自己研究设计出高 速、高精度的模数转换器。

电子行业深度研究:人工智能进入新时代,开启算力需求新篇章

电子人工智能进入新时代,开启算力需求新篇章伴随着OpenAI 推出的AIGC 产品功能逐渐强大,由此而带来了新的供给。

AIGC 已逐渐跑通成熟的商业模式,并且模型快速迭代,国内厂商奋起直追,促使整个社会对于算力需求的快速提升。

➢ 伴随着OpenAI 推出的AIGC 产品功能逐渐强大,由此而带来了新的需求。

伴随着AIGC 产品的应用场景逐渐丰富,无论是to B 端还是to C 端,都创造出了新的需求。

➢ OpenAI 已逐渐跑通成熟的商业模式,主要采用按量收费方式。

首先作为底层平台接入其他产品对外开放,按照数据请求量和实际计算量计算。

其次最新发布插件功能ChatGPT Plugins 可以帮助客户访问最新信息、运行计算或使用第三方服务。

➢ 算力需求指数级提升,国产替代随之而来。

伴随着AIGC 模型快速迭代,在模型性能实现飞跃式提升的同时,模型所使用参数量与预训练数据量也呈现指数级增长,与之相对应的便是整个社会对于算力需求的快速提升。

2023年开始美日荷对我国半导体产业链的掣肘行动逐渐加剧,国产算力替代随之而来。

➢ 投资建议:我们认为,AIGC 应用面逐渐越来越广,国内各大厂商奋起直追,整个社会对于算力的需求将呈现指数级增长,叠加美日荷对我国半导体行业的掣肘,国产替代随之而来。

重点关注: ➢ 1)GPU 厂商:景嘉微、海光信息;➢ 2)CPU 厂商:海光信息、龙芯中科;➢ 3)FPGA 厂商:紫光国微、复旦微电、安路科技;➢ 4)AI 芯片厂商:寒武纪、国芯科技;➢ 风险提示:AIGC 行业发展进程不及预期;国内厂商由于起步较晚而无法与国际巨头竞争;国产替代进程不及预期。

重点关注标的:简称EPS PE CAGR-3评级22A/E 2023E 2024E 22A/E 2023E 2024E 景嘉微 0.68 0.79 0.90 165.46 142.42 125.01 15% / 寒武纪 -2.91 -1.79 -1.19 -76.22 -123.91 -186.39 36% / 紫光国微 3.10 4.03 5.12 36.23 27.87 21.94 29% 买入复旦微电 1.32 1.85 2.36 48.45 34.57 27.10 34% 增持 安路科技 0.15 0.26 0.49 475.20 274.15 145.47 81% 增持 海光信息 0.35 0.54 0.85 258.71 167.69 106.53 56% / 国芯科技 0.35 0.941.49 206.37 76.84 48.48 106% /数据来源:公司公告,iFinD ,国联证券研究所预测,股价取2023年4月19日收盘价 证券研究报告 2023年04月20日投资建议: 强于大市(维持评级)上次建议: 强于大市相对大盘走势Table_First|Table_Author 分析师:熊军执业证书编号:S0590522040001 邮箱:*****************.cn分析师:孙树明执业证书编号:S0590521070001 邮箱:**************.cn联系人 刘欢宇邮箱:**************.cn相关报告1、《北方华创业绩超预期,设备材料有望维持高增长电子》2023.04.152、《周期复苏叠加AI 创新有望推动电子大行情电子》2023.04.083、《美光释放乐观预期,存储芯片有望迎来周期拐点电子》2023.04.03本报告仅供 y bj ie s ho u @e a s t m o n e y .c o m 邮箱所有人使用,未经许可,不得外投资聚焦研究背景北京时间3月14日晚间,谷歌宣布将进一步在其产品中引入人工智能(AI )技术,北京时间2023年3月15日凌晨,OpenAI 宣布正式推出GPT-4。

基于国产化器件的DRFM设计

基于国产化器件的DRFM设计王明君【摘要】在雷达电子对抗领域,基于数字射频存储器(DRFM)的雷达干扰系统方案因为具有可靠性高、假目标样式灵活且逼真度高等特点而被广泛采用.设计了一种宽带DRFM设备,性能指标达到预期,可满足大部分应用场合.【期刊名称】《电子与封装》【年(卷),期】2018(018)006【总页数】4页(P26-28,37)【关键词】数字射频存储器;模数转换器;数模转换器【作者】王明君【作者单位】中国电子科技集团公司第五十一研究所,上海 201802【正文语种】中文【中图分类】TN4021 引言随着无线电装备的广泛应用,现代化战场电磁环境日渐复杂。

在雷达对抗领域,数字射频存储器(DRFM)利用高速ADC对雷达信号进行高速高精度采样,利用高速处理器(如FPGA)对采样数据进行处理并送入高速存储器进行存储;释放干扰时,处理器从存储器中读出波形数据,进行干扰调制后送高速DAC进行数模转换,产生高逼真的雷达干扰信号,实现对雷达的有效干扰。

雷达抗干扰技术的进步,使得雷达干扰设备需具备更宽的瞬时带宽[1]。

作为干扰设备的核心部件,DRFM往往需要几倍于目标雷达的带宽。

这就要求DRFM的核心器件ADC、DAC具有更高的采样率,FPGA及存储器具备更大的数据带宽。

以往,高速高精度ADC、DAC及高端FPGA、RAM长期依赖进口,近年来高端集成电路的国产化已取得显著成效。

本文基于国产高速ADC、高速DAC、大规模FPGA及RAM设计了一种宽带DRFM设备,设备性能满足大部分干扰设备使用需求。

2 硬件设计2.1 硬件架构设计雷达信号通过干扰机天线进入接收系统,经过放大滤波及变频等信号调理后,变为适应DRFM工作窗口的中频信号;中频信号经过高速高精度ADC采样后变为数字中频信号;采样数据进入FPGA后进行格式转换处理,送入双口静态存储器(DPRAM)进行实时存储。

干扰时,FPGA根据指令将存储器中的数字波形文件读出并进行调制后产生数字干扰波形数据,将波形数据调整格式后送入高速DAC实现数模转换,产生中频干扰信号,将中频干扰信号进行上变频后发射出去,实现对雷达的干扰。

高速ADCDAC电路及PCB设计要点梳理

高速ADCDAC电路及PCB设计要点梳理概要在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。

最终的答案各不相同,但在所有情况下,设计工程师都应兼顾全局,而不要过分计较布局布线的每一个细节。

很多情况下做不到面面俱到,只能根据电路板及产品的面积进行取舍。

下面就给大家分享一下ADC/DAC电路及PCB设计中几个比较重要的问题:1数字地模拟地是否分割的问题硬件工程师最常提出的问题是:使用ADC时是否应将接地层分为AGND和DGND接地层?简单回答是:视情况而定。

详细回答则是:通常不分离。

为什么不呢?因为在大多数情况下,盲目分离接地层只会增加返回路径的电感,它所带来的坏处大于好处。

从公式V = L(di/dt)可以看出,破坏了GND的完整性,随着电感增加,电压噪声会提高。

随着电感增加,设计人员一直努力压低的PDN阻抗也会增加。

随着提高ADC采样速率的需求继续增长,降低开关电流(di/dt)的方式却很有限。

因此,除非需要分离接地层,否则请保持这些接地连接。

所以我们的结论是大部分情况下推荐不做DGND AGND分割,这个和大家早期经验做法相左。

我们大部分的产品是有尺寸要求的,可能没有足够和理想的空间。

受尺寸限制的影响,电路板无法实现良好的布局分割时,就需要分离接地层。

这可能是为了符合传统设计要求或尺寸,必须将脏乱的总线电源或高噪声数字电路放在某些区域。

这种情况下,分离接地层是实现良好性能的关键。

然而,为使整体设计有效,必须在电路板的某个地方通过一个磁珠或局部连接点将这些接地层连在一起。

最终,PCB上往往会有一个连接点成为返回电流通过而不会导致性能降低或强行将返回电流耦合至敏感电路的最佳位置。

如果此连接点位于转换器、其附近或下方,则不需要分离接地。

2巴伦的选择问题,规格及类型ADI的参考设计里面一般推荐是mini circuit的巴伦,但也有有高端的marki的巴伦变压器,动则上千元一个。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中科院微电子成功研发30Gsps 6bit超高速ADC和

DAC

日前,中科院微电子所成功研发出超高采样率、宽频带的30Gsps 6bit超高速模拟数字转换器(ADC)和数字模拟转换器(DAC),成功大幅缩短了与先进国家的技术差距,为我国在该领域摆脱国外技术壁垒限制增加了关键性的筹码,对下游产业的发展起到了极大的促进作用。

更关键的是,该芯片已在武汉邮电科学院构建的1Tb/s相干光OFDM传输验证平台上实现应用验证。

就在今年3月,美国对中兴通讯进行制裁的时候,由于中兴通讯FPGA、光器件、高速ADC/DAC等器件很大程度上依赖从美国进口,一些媒体甚至认为中兴通讯将可能遭遇寒冬,乃至破产。

而本次的技术突破则有望使中兴通讯在ADC/DAC方面摆脱受制于人的局面。

ADC芯片

在当下,数字系统和模拟系统已覆盖了生活和工业生产的方方面面,比如计算机就是非常典型的数字系统,在工业领域,很多工业检测多是连续变化的物理量,往往用与之对应的电压、电流或频率等进行模拟,因而这些都属于模拟系统。

而高速ADC/DAC则是连接数字系统和模拟系统的桥梁和媒介。