清华PLL讲义

第1章 PLL基本概念

2015-1-18

湖北大学物电学院 余琼蓉

5

锁 相 技 术

二

相位关系描述

uo (t ) Uo cos[ot o (t )]

输入输出瞬时相差

输出信号矢量 输入信号的瞬时相位 输出信号的瞬时相位

ui (t ) Ui sin[it i (t )]

输入信号矢量

e (t ) [it i (t )] [ot o (t )] (i o )t i (t) o (t)

环路的相位模型

2015-1-18

湖北大学物电学院 余琼蓉

17

锁 相

锁相环路的组成模型

PLL的误差电压 控制电压

技 术

输入信号

2015-1-18

湖北大学物电学院 余琼蓉

18

锁 相 技 术

鉴相器PD:

鉴相器: 是一个相位比较装置,用来检测输入信号相位θ1(t)与反馈信

号相位θ2(t)之间的相位差θe(t)。输出的误差信号ud(t)是相差θe(t)的函数, 即

2015-1-18

湖北大学物电学院 余琼蓉

2

锁 相 技 术

第1节

• • • • • 一 二 三 四 五

锁定与跟踪的概念

PLL的输入输出信号及其表示 相位关系描述 捕获过程 锁定状态 环路和基本性能要求

2015-1-18

湖北大学物电学院 余琼蓉

3

一

PLL的输入输出信号及其表示

PLL

锁 相 技 术

ui (t )

锁 相 技 术

第一章 锁相环的基本工作原理

相关知识 第一节 锁定与跟踪的概念 第二节 环路组成 第三节 环路的动态方程 第四节 一阶锁相环的捕获、锁定与失锁 第一章 章结

第1章PLL工作原理与电路构成1

第1章PLL工作原理与电路构成1(PLL与频率合成技术简介) 电路的基本工作原理111PLL 电路的三大组成部分1111PLL 的应用与频率合成器3112PLL 电路各部分工作波形3113PLL 电路以及频率合成器的构成412PLL 输出为输入N倍频的方法4121 输出为输入N/M倍频的方法(输入部分接入分频电路)5 122 输出为输入N/M倍频的方法(输出部分接入分频电路)5 123 输出为输入N×M倍频的方法(增设前置频率倍减器)6 124 电路与外差电路的组合方式(输出为(fin×N)+fL)7 125PLL 电路与DDS的组合方式7126PLL13PLL 频率合成器的信号纯正度9 理想频率合成器的输出频谱(1根谱线)9131132 振幅调制的噪声(AM噪声)10 频率调制的噪声(FM噪声)12133 噪声的影响14134FM 的其他应用1614PLL 数字数据恢复为时钟的情况16141【专栏】dBc18 频率电压转换电路(FM解调电路)19142 电动机的转速控制电路19143【专栏】PLL电路的发明者Bellescize20附录APLL电路中负反馈的应用21 电路与运算放大器电路的异同21A1PLL 放大电路中学习的负反馈方式与特性23A2第2章PLL电路的传输特性31(PLL电路的特性由环路滤波器决定) 电路传输特性的理解3121PLL211PLL 电路各部分的传输特性31 简单例题(时钟的50倍频电路)33212 传输特性的求法(除环路滤波器特性以外)35213【专栏】仿真使用SPICE非常方便36 使用的环路滤波器的特性与PLL电路的传输特性37214 PLL电路中施加负反馈的效果39215 环路滤波器设计的基础知识4122 低通滤波器的特性41221RC 具有阶跃特性的RC低通滤波器43222 多级RC滤波器中增益与相位之间关系44223 普通的RC低通滤波器(使用滞后滤波器时环路特性不稳定)46 224 使PLL特性稳定的滞后超前滤波器47225第3章PLL电路中环路滤波器的设计方法51(无源/有源环路滤波器的设计实例与验证) 无源环路滤波器的设计5131 滞后超前滤波器的伯德图51311312PLL 电路与滞后超前滤波器组合的特性53 分频系数的改变情况56313 根据规格化曲线图求出环路滤波器的常数(参照附录B)57 3143210 ~100kHz PLL频率合成器中环路滤波器的设计59 作为实验用频率合成器的概况59321 频率合成器传输特性的求法322(除环路滤波器以外)61 时间常数小、M=-10dB、相位裕量为60°的设计61323324 时间常数中等、M=-20dB、相位裕量为50°的设计64 时间常数大、M=-30dB、相位裕量为50°的设计66325 试做的频率合成器的输出波形68326 试做的频率合成器的输出频谱70327 锁相速度72328 有源环路滤波器7533331 有源环路滤波器75 次有源环路滤波器的伯德图753322 次有源环路滤波器773333 有源环路滤波器的噪声79334 根据规格化曲线图求出有源环路滤波器常数的方法80 335 ~50MHz PLL频率合成器中环路滤波器的设计80 3425 实际电路中设计的有源环路滤波器80341 使用规格化曲线图求出环路滤波器的常数81342 时间常数小、M=0dB、相位裕量为50°的设计85343 时间常数中等、M=-10dB、相位裕量为34450°的设计86 时间常数大、M=-20dB、相位裕量为50°的设计88 345 试做的频率合成器的输出波形89346 试做的频率合成器的输出频谱90347 锁相速度92348 锁相速度的仿真94349【专栏】用于测量频率变化形式的调制磁畴分析仪97 相位裕量不同时PLL电路的特性9735 用作实验的50倍频电路98351 环路滤波器的设计99352 相位裕量为40°的设计99353354 相位裕量为50°的设计100 相位裕量为60°的设计100355356 频率特性的仿真101 输出波形的频谱103357 锁相速度104358 电路最适用的相位裕量(40°~50°)105359PLL第4章4046与各种鉴相器109(PLL电路中使用的重要器件的基础知识) 的重要器件404610941PLL411PLL 的入门器件109 的三种类型1104124046 片内三种鉴相器11041374HC40464144046 片内VCO的特性113 鉴相器的工作要点11542 模拟鉴相器115421 数字鉴相器118422 相位频率型鉴相器120423 中PC2型鉴相器1234244046 死区124425 电流输出型鉴相器126426 高速鉴相器AD 9901127427第5章电压控制振荡器VCO的电路131(VCO要求的特性及各种振荡电路方式) 要求的性能13151VCO 的概况131511VCO 频率可变范围133512 频率控制的线性133513 输出噪声133514 输出波形的失真134515 电源电压变化时的稳定度134516 环境温度变化时的稳定度134517 外界磁场与振动的影响135518 由弛张振荡器构成的VCO13552 函数发生器的基本工作原理135521 由函数发生器构成的VCO138522 函数发生器IC MAX038的应用139523 反馈振荡器14253 反馈振荡器的基本工作原理142531 反馈振荡器振荡稳定的方法142532 由RC构成的反馈振荡器143533 状态可变VCO147534 高频用LC振荡电路及其在VCO中的应用15154 基本的哈脱莱/科耳皮兹振荡电路151541 科耳皮兹的改进型克拉普振荡电路152542 反耦合振荡电路153543 由LC振荡器构成VCO时采用的变容二极管154 544545 市售的LC振荡式VCO电路157 其他的VCO电路15855 由振子构成的反馈振荡器158551 延迟振荡器162552第6章可编程分频器的种类与工作原理163(构成PLL频率合成器的数字电路) 可编程分频器的基本器件(减计数器)1636161174HC19116361274HC40102/40103164613TC919816562 前置频率倍减器168 前置频率倍减器IC168621 脉冲吞没(Pulse Swallow)方式170622 分数(Fractional)-N方式171623 用LSI17263PLL 专用LSI的构成172631PLL632ADF4110/4111/4112/4113173第7章PLL电路的测试与评价方法177(无源/有源环路滤波器的环路增益) 负反馈电路中环路增益的测试17771 难以测试的环路增益177711 施加负反馈时原环路增益的测试178712 负反馈环路测试的仿真180713714 实际注入的信号181 使用频率响应分析仪的测试方法18372 负反馈环路特性的测试183721722FRA 与FFT分析仪的不同之处185 与网络分析仪的不同之处185723FRA 电路中环路增益的测试18673PLL 使用无源环路滤波器的PLL186731 使用有源环路滤波器的PLL188732第8章PLL特性改善技术191(信号纯正度与锁相速度的提高技术) 优质的电源19181 使用CMOS反相器电路进行的实验191811 使用晶体振荡电路进行的实验193812 串联稳压器噪声特性的比较196813 控制电压特性的改善20082VCO 内VCO线性的改善200821CD74HC4046 片内VCO的频率变化范围的扩大204822CD74HC4046 与鉴相器之间的干扰20683VCO 中VCO与鉴相器同在的情况20683174HC4046832 用1个74HC4046进行的实验207 使用2个74HC4046进行的实验(VCO和鉴相器在不同的封装中)209 83384 鉴相器的死区210 用74HC4046进行死区影响的实验211841 与巴厘枚嘎模块VCO的组合使用213842PC28434046 中PC1与巴厘枚嘎模块VCO的组合使用217 与巴厘枚嘎模块VCO的组合使用220 84474HCT9046 锁相速度的改善22185 用二极管切换环路滤波器常数的方法222851 用模拟开关切换环路滤波器常数的方法224852 转换器进行预置电压相加的方法226 用D A853第9章实用的PLL频率合成器的设计与制作229(环路滤波器的详细设计与实测特性) 使用74HC4046的时钟频率合成器22991 替代1Hz~10MHz晶体的频率合成器229911 全部使用CMOS IC构成的频率合成器230912 环路滤波器的设计233913 输出波形235914 频谱235915 锁相速度238916 使用TLC2933构成的脉冲频率合成器23992 系列的概况239921TLC29xx 时钟频率合成器电路239922 环路滤波器的设计241923 输出波形频谱的测试243924 频率合成器24593HF 频率合成器电路245931HF 2环路滤波器常数的计算24893 频谱250933 锁相速度252934 频率基准信号用PLL2559440MHz 频率基准信号用PLL电路25594140MHz 环路滤波器的设计258942 输出波形260943 低失真的低频PLL电路26195951 低失真的低频PLL电路261 环路滤波器的设计264952 输出波形的合成267953附录B环路滤波器设计用规格化曲线图270附图:各公司4046的振荡频率控制电压特性270参考文献282。

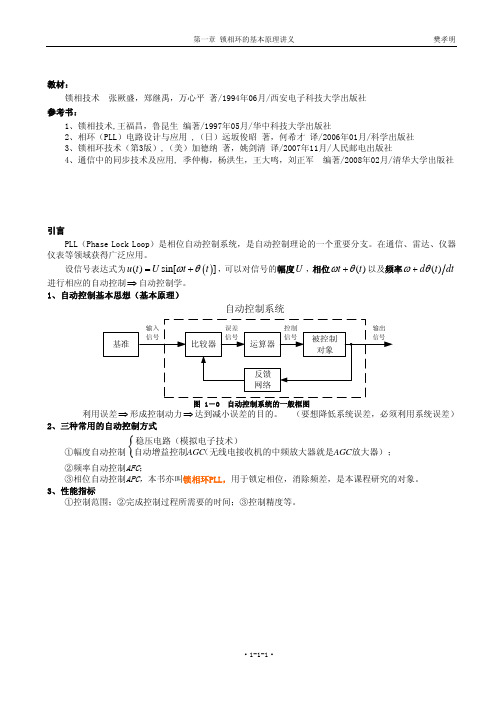

6.1 锁相环路(PLL)电路基础

t

VCO受环路滤波器输出电压uc(t)的控制,使振荡频率 向输入信号的频率靠拢,直至两者的频率相同,使得 VCO输出信号的相位和输入信号的相位保持某种特定 的关系,从而达到相位锁定的目的。

4.锁相环的基本工作过程 锁相环的基本工作过程如下: (1)设输入信号ui(t)和本振信号(压控振荡器输出信 号)uo(t)分别是正弦和余弦信号,它们在鉴相器内进 行比较,鉴相器的输出是一个与两者间的相位差成比 例的电压ud(t),一般把ud (t)称为误差电压。 (2)环路低通滤波器滤除鉴相器输出中的高频分量, 然后把输出电压uc(t)加到VCO的输入端,VCO的本振 信号频率随着输入电压的变化而变化。如果二者频率 不一致,则鉴相器的输出将产生低频变化分量,并通 过低通滤波器使VCO的频率发生变化。只要环路设计 恰当,则这种变化将使本振信号uo(t)的频率与鉴相器 输入信号ui (t)的频率一致。

图6.1.3 三种常用的环路滤波器

图6.1.3(a)所示的一阶RC低通滤波器的传递函 数为输出电压uc(t)与输入电压ud(t)之比,即

1 1 u ( jω ) jω C H ( jω ) = c = = RC 1 ud ( jω ) R + 1 jω + jω C RC

改为拉氏变换形式,用s代替jω,得 1 1 RC = τ = 1 H (s) = 1 1 sτ + 1 s+ s+ RC τ 式中,τ =RC为滤波器时间常数

3.良好的门限特性 在调频通信中,锁相环路用做鉴频器时也有门限效应存在。 但是,在相同的调制系数的条件下,它比普通鉴相器的门 限低。当锁相环路处于调制跟踪状态时,环路有反馈控制 作用,跟踪相位差小,这样,通过环路的作用,限制了跟 踪的变化范围,减少了鉴相特性的非线性影响,改善了门 限特性。 锁相环路在通信系统中的用途极为广泛。例如,锁相接收 机、微波锁相振荡源、锁相调频器、锁相鉴频器、窄带的 高频带通滤波器等。在锁相频率合成器中,锁相环路具有 稳频作用,能够完成频率的加、减、乘、除等运算,可以 作为频率的加减器、倍频器、分频器等使用。 目前在比较先进的模拟和数字通信系统中大都使用了锁相 环路。

PLL详解

PLL详解什么是锁相环呢?MCU的支撑电路一般需要外部时钟来给MCU提供时钟信号,而外部时钟的频率可能偏低,为了使系统更加快速稳定运行,需要提升系统所需要的时钟频率。

这就得用到锁相环了。

例如MCU用的外部晶振是16M的无源晶振,则可以通过锁相环PLL把系统时钟倍频到24M,从而给系统提供更高的时钟信号,提高程序的运行速度。

51单片机,AVR单片机内部没有锁相环电路,其系统时钟直接由外部晶振提供。

而XS128内部集成了锁相环电路,其系统时钟既可由外部晶振直接提供,也可以通过锁相环倍频后提供,当然,还有由XS128内部的时钟电路来提供(当其它来源提供的系统时钟不稳定时,内部时钟电路就起作用了,也就是自时钟模式)。

锁相环作为一个提供系统时钟的模块,是一个基本的模块,几乎每次编程序都得用到。

下面记一下怎样配置锁相环来设定想要的系统时钟。

锁相环PLL、自时钟模式和前面说的实时中断RTI、看门狗COP 都属于系统时钟与复位CRG中的模块,固前面用到的寄存器,这里有些会再用到。

在程序中配置锁相环的步骤如下:第一、禁止总中断;第二、寄存器CLKSEL的第七位置0,即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK,在PLL程序执行前,内部总线频率为OSCCLK/2。

CLKSEL_PLLSEL=0时,系统时钟由外部晶振直接提供,系统内部总线频率=OSCCLK/2(OSCCLK为外部晶振频率)。

CLKSEL_PLLSEL=1时,系统时钟由锁相环提供,此时系统内部总线频率=PLLCLK/2 (PLLCLK为锁相环倍频后的频率)。

第三、禁止锁相环PLL,即PLLCTL_PLLON=0。

当PLLCTL_PLLON=0时,关闭PLL电路。

当PLLCTL_PLLON=1时,打开PLL电路。

第四、根据想要的时钟频率设置SYNR和REFDV两个寄存器。

SYNR和REFDV两个寄存器专用于锁相环时钟PLLCLK的频率计算,计算公式是:PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)其中,PLLCLK为PLL模块输出的时钟频率;OSCCLK为晶振频率;SYNR、REFDV分别为寄存器SYNR、REFDV中的值。

第一章 锁相环路的基本工作原理讲义

第一章 锁相环的基本原理讲义

樊孝明

U i sin[0t (i 0 )t i (t )] U i sin[0t 0t i (t )] U i sin[0t 1 (t )] 式中:0 i 0 为输入信号频率与环路自由振荡频率之差,称为环路的固有频差,这也是PLL一个

非常重要的参数。 则输入、输出信号以 0t 为参考的瞬时相位分别为 1 (t ) 与 2 (t ) ,

1 (t ) 0t i (t ) (i 0 )t i (t ) ; 2 (t ) 0 (t )

可得PLL相位框图如图1-1(b)所示。

2、瞬时相差 e (t ) 与瞬时频差 e (t )

注意:输入信号是 sin 型,而输出信号是 cos 型,后面会做相应解释,在此不作解释; PLL是相位控制系统,PLL对输入与输出信号起作用的是它们的瞬时相位 因此必须建立输入、输出信号相位之间的控制关系。 二、PLL相位关系描述

1、输入、输出信号的相位表达式

输入信号的瞬时相位: i t i (t ) ; 输入信号的瞬时频率:

当环路进入同步之后,根据同步状态定义,输出信号的瞬时相位 0 (t ) 和瞬时频偏 0 (t ) 应满足下式:

0 (t ) 2 (t ) 1 (t ) e 0t i e ;

0 (t ) 0

将 0 (t ) 代入输出信号表达式 u0 (t ) U 0 cos[0t 0 (t )] 中可得:

c、环路能够进入锁定状态(简称为环路能够锁定)的条件 | 0 | p 或 0 p i 0 p 四、同步状态即锁定状态

1、同步状态定义:

瞬时频差|e ( t )| 瞬时相差|e ( t ) 2 n | e 这是环路同步的一般条件。

PLL上课讲义

Receiver I/O

Data Recovered clock t

CPU

MEM

PLL ICs

1-3

Ching-Yuan Yang / EE, NCHU

What is PLL ?

Reference signal

x(t) Phase Detector Loop Filter Synchronized Oscillator y(t) Synchronized signal

φ = ∫ (ω0 + K VCOVcont )dt

to take place.

Phase alignment can be achieved only by a (temporary) frequency change. The output phase of a VCO can be aligned with the phase of a reference if • the frequency of the VCO is changed momentarily, • a phase detector is used to determine when the VCO and reference signals are aligned. Phase locking is a task of aligning the output phase of the VCO with the phase of the reference.

PLL ICs

1-13

Ching-Yuan Yang / EE, NCHU

Basic PLL topology (cont’d)

Feedback loop comparing input and output phases

PLL(锁相环)电路原理及设计 [收藏]

![PLL(锁相环)电路原理及设计 [收藏]](https://img.taocdn.com/s3/m/ca8d027601f69e3143329497.png)

PLL(锁相环)电路原理及设计[收藏]PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

非常经典 清华大学 李宇根 PLL讲义 Lecture12

Spring Semester, 2008PLL DESIGN AND CLOCK/FREQUENCY GENERATION (Lecture 12)Woogeun Rhee Institute of Microelectronics Tsinghua UniversityTerm Project• Design 645MHz fractional-N PLL circuit: - fref = 40MHz, fout = 645MHz with 50% duty cycle - Due date: June 24th40MHzfref(1) (2)645MHzPFD(3)CP(4)VCO(5)2(6)foutPLL BW: ~500kHz16/17 k-bit ACCUM2W. Rhee, Institute of Microelectronics, Tsinghua UniversityTerm Project (continued)• Do followings: 1. Design loop filter for ~500kHz PLL bandwidth. 2. Draw open-loop gain Bode plot based on LPF design from (a). 3. Plot node 3, 4 and check the lock time. 4. Plot node 1, 2 after PLL is fully settled. What is the amount of static phase offset? 5. Plot node 5, 6 for 10 VCO cycles (i.e. zoom-in plot). 6. Estimate the spur level based on VCO gain and waveform at node 3. 7. Verify (f) result by having FFT and measure spur level at VCO output in dBc. E1. Plot eye diagram of VCO output and measure jitter in time domain. (extra) E2. Run phase noise simulation of open-loop VCO and calculate closed-loop RJ. (extra) E3. Calculate closed-loop RJ by defining approximated noise bandwidth. (extra) E4. Tell whether DJ or RJ is dominant. (extra) • Note: Ideal blocks allowed for PFD & LPF design3W. Rhee, Institute of Microelectronics, Tsinghua UniversityV. Applications 3. Clock Multiplier Unit (CMU)4W. Rhee, Institute of Microelectronics, Tsinghua UniversityCMU Design Considerations• Similar to RF frequency synthesizer - Use of frequency divider and PFD/CP - Trade-off between noise and spur • Different from RF frequency synthesizer - Less stringent lock-in time - Ultimately interested in pk-pk jitter. - Noisier supply voltage - Noisier reference clock - Lower supply voltage - Mostly in digital CMOS process - Ring VCO and on-chip LPF preferred.5W. Rhee, Institute of Microelectronics, Tsinghua UniversityJitter• Absolute jitter (long-term jitter) - Phase error w.r.t. ideal referenceΔTabs ,rms = lim1 2 ΔT12 + ΔT22 + ⋅ ⋅ ⋅ + ΔTN N →∞ N• Cycle-to-cycle jitter (short-term jitter) - No need for referenceΔTcc ,rms ≈ lim1 (T2 − T1 )2 + (T3 − T2 )2 + ⋅ ⋅ ⋅ + (TN − TN −1 )2 N →∞ N• Period jitter - For PLL, period jitter = absolute jitter.ΔTp ,rms = lim1 (T − T1 )2 + (T − T2 )2 + ⋅ ⋅ ⋅ + (T − TN −1 )2 N →∞ N*Note:Periodic jitter (PJ) is often considered DJ by sinusoidal modulation, which is different from period jitter.W. Rhee, Institute of Microelectronics, Tsinghua University6Total Jitter (TJ)RJpk-pk (14*σ)• Total jitter (TJpp) - RJpp + DJpp = 14 x RJrms + DJpp • Random jitter (RJ) - Non-systematic jitter - Gaussian distribution • Deterministic jitter (DJ) - Systematic jitter - Coupling and ISI - Duty cycle distortionDJDJ dominant (modulation)RJ dominant (noise)Pspurfo7W. Rhee, Institute of Microelectronics, Tsinghua UniversityRandom Jitter (RJ)Bathtub Curve• For BER = 10-12, RJpp = 14 x RJrmsRef: “Jitter Fundamentals,” Wavecrest Company8W. Rhee, Institute of Microelectronics, Tsinghua UniversityRJ and Noise Integration BandwidthfoCDR tracking BWPDLPFCDRN• CDR tracking BW should be considered for TXPLL design. - SONET: 50kHz – 80MHz - Typically (Baud Rate) / 1667 – (Baud Rate) / 29W. Rhee, Institute of Microelectronics, Tsinghua UniversitySupply Noise EffectfoCDR tracking BWPDLPFCDRN10W. Rhee, Institute of Microelectronics, Tsinghua UniversityJSSC’96, von Kaenel et al. Supply Noise ConsiderationSupply w/o NoiseSupply w/t Noise(f 3dBLess power but needs more careful design for 50% duty cycle.Cascaded PLLsParallel PLLsISSCC’03, Wong et al.Cascaded PLLsV. Applications3. Clock Multiplier Unit (CMU)A. Uniform BW control for PCIe2B. ΔΣPLL for digital clock generationC. S-S clocking for EMI reductionInside PCCurrent ComingFB-DIMM•DDR2 DRAM + high-speed serial linkÆPoint-to-point serial link communication •Overcomes trade-off between speed and capacity.[Li, ITC’04], [PCI-SIG]s o 123H s H s e H s H s −Δτ=−⋅()[()()]()H 1(s)H 3(s)H 2(s)ΔτLC VCORing VCO[Noguchi, ISSCC’02][Herzel, JSSC’03][Moon, JSSC’04][Williams, CICC’04]Dual-Path VCOsTimeTimeVarious Coarse-Tuning Gains(with BW FINE = 1)Various Coarse-Tuning Bandwidths(with BW FINE = 1)(CppSim tool from M.I.T. used for simulation)PLL Behavioral Simulation(<80kHz)(10MHz)VDDINBINBIASOUT OUTBR1R2Narrowbanding (for coarse tuning)4th -pole of PLL (for fine tuning)Resistor noise contribution to PLLH(f)fF RCF BWLinear Amplifier and Noise ConsiderationPhase Noise PerformancesMeasured RJ VariationMeasured VCO Tuning CurvePSRR PerformanceV. Applications3. Clock Multiplier Unit (CMU)A. Uniform BW control for PCIe2B. ΔΣPLL for digital clock generationC. S-S clocking for EMI reductionFractional-N PLL for Wireline Applications?Flexible Frequency Planning with ΔΣPLL•Conventional PLL makes it difficult to accommodate various reference clock frequencies.Digital Clock Generation with <1ppm Resolution•PLL with ring VCO needs wide bandwidth to suppress VCO noise.ÆLow f ref /f bw ratio makes it difficult to implement ΔΣfractional-N PLL.ÆSuffer from cycle-to-cycle jitter problem due to quantization noise.Fractional-N PLL for Digital SystemL f ) d B c /H z )Basic ConceptsEquivalent Discrete-Time Model Frequency ResponseL ) B c H zBehavioral Simulation Results500MHz Output Spectrum(Fref= 14.318MHz, N=37.15603)VCO Control Voltage•FIR-embedded frequency divider reduces output cycle-to-cycle jitter.ISCAS’07, Chi et al.Measured Output SpectraV. Applications3. Clock Multiplier Unit (CMU)A. Uniform BW control for PCIe2B. ΔΣPLL for digital clock generationC. S-S clocking for EMI reductionElectromagnetic Interference (EMI)•Radiation emission is strictly regulated by FCC.•Can be reduced by shielded cables but expensive and bulky.ÆHow about modulating clock to reduce peak power?Modulation Profile Clock SpectrumCarrier(w/o modulation)Spread Spectrum ClockingJSSC’03, Chang et al.By Voltage ModulationBy Divider Modulation By ΔΣModulation ISSCC’99, Li et al.ISSCC’05, Lee et al.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Æ Simply speaking, we will learn where to, when to, and how to use PLL for various applications.

5

W. Rhee, Institute of Microelectronics, Tsinghua University

8

W. Rhee, Institute of Microelectronics, Tsinghua University

I. Overview of Clocking and Frequency Generation

10

W. Rhee, Institute of Microelectronics, Tsinghua University

3

W. Rhee, Institute of Microelectronics, Tsinghua University

Course Assessment

• Homework: • Midterm exam: • Final exam: • Term project:

10% 20% 30% 40%

PLL DESIGN AND CLOCK/FREQUENCY GENERATION (Lecture 1)

Woogeun Rhee Institute of Microelectronics Tsinghua University

PLL Design and Clock/Frequency Generation (PLL设计与时钟/频率产生)

Course Outline – First Half

I. Overview of Clocking and Frequency Generation 1. Course introduction 2. Phase-locked clocking in modern communication systems II. Phase-Lock Basics 1. PLL linear model 2. Loop components 3. Loop dynamics 4. Transient response and acquisition 5. PLL behavioral simulations III. PLL Design 1. System design perspectives - spur and modulation - phase noise/jitter - settling time - bandwidth optimization 2. Circuit design aspects - phase detector - charge pump - frequency divider - voltage-controlled oscillator 3. Delay-locked loop (Midterm Examination)

• Course #: 80260042 • Time: Tuesday, 7:20pm – 8:55pm (spring’07) • Place: 六教6B206 • TA: 孙远峰 • Office hour: Thursday 2-4pm (10-11am for those who have time conflict) • Prerequisite: Basic analog/digital circuit design

2

W. Rhee, Institute of Microelectronics, Tsinghua University

Textbook & References

• Main Textbook

R. E. Best, Phase-Locked Loops, 5th ed., McGraw-Hill, New York, 2003

W. Rhee, Institute of Microelectronics, Tsinghua University

6

Course Outline – Second Half

IV. Applications 1. Frequency synthesizers for RF applications - system design consideration; phase noise, spur, and settling time - integer-N/fractional-N frequency synthesizers - direct digital frequency synthesizer 2. Clock-and-data recovery for serial link and optical communications - system design considerations; jitter transfer, jitter tolerance, and jitter generation - circuit design aspects in multi-Gb/s SerDes systems - DLL-based CDR for serial-link backplane applications - D/PLL-based CDR for SONET applications 3. Clock multiplier unit for digital clock generation - system design considerations; RJ, DJ, long-term jitter, and short-term jitter - circuit design for high supply rejection - examples; PLL design for FB-DRAM, multiplying DLL (MDLL) for low jitter accumulation 4. PLL for “design on demand” V. Advanced Topics 1. Recent PLL works and trends 2. Coupling effects on PLL performance 3. Various in-situ calibration/compensation methods for technology-friendly PLL 4. Future challenges VI. Project Discussion (Final Examination)

• References:

Theory and System Analysis W. Egan, Phase-Lock Basics, Wiley, New York, 1998 F. M. Gardner, Phaselock Techniques, 3rd ed., Wiley, New Jersey, 2005 D. H. Wolaver, Phase-Locked Loop Circuit Design, Prentice Hall, New Jersey, 1991 U. Rhode, Microwave and Wireless Synthesizers, Wiley, New York, 1997 W. Egan, Frequency Synthesis by Phase Lock, Wiley, New York, 2000 J. Smith, Modern Communication Circuits, McGraw Hill, New York, 1986 Architectures and Circuit Design B. Razavi, RF Microelectronics, Prentice Hall, New Jersey, 1998 T. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge, UK, 1997 Collection of Selected Papers B. Razavi, Monolithic Phase-Locked Loops and Clock Recovery Circuits, IEEE Press, New York, 1996 B. Razavi, Phase-Locking in High-Performance Systems, IEEE Press, New York, and Wiley, New Jersey, 2003

7

W. Rhee, Institute of Microelectronics, Tsinghua University

Lecture & Workshop by Prof. Perrott (MIT)

• Invited Lecture (will replace our PLL lecture, Apr. 17) - Fractional-N synthesizer and simulation • Workshop (Apr. 18 – 19) - PLL behavioral simulation tutorial - Lab exercise

What Is Phase-Locked Loop?

θin

PD

ቤተ መጻሕፍቲ ባይዱLPF

VCO

θout

• A circuit that synchronizes the signal from an oscillator with a second input signal (reference) so that they operate at the same frequency (Egan/Best). • A feedback system in which the feedback signal is used to lock the output frequency and phase to the frequency and phase of an input signal (Smith). • Basically an oscillator whose frequency is locked onto some frequency component of an input signal, which is done with a feedback control loop (Wolaver).