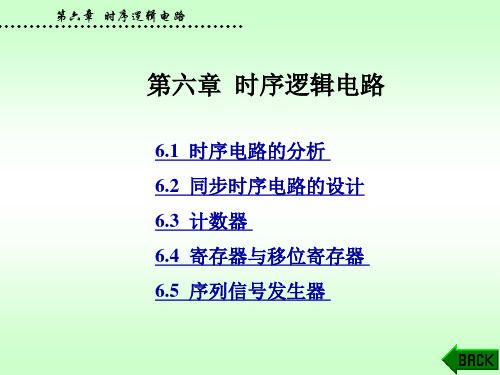

《数字逻辑电路(A)》复习题第六章时序电路

数字逻辑电路复习题与答案

_、单选题1、十进制整数转换为二进制数一般采用()。

A.除2取整法B.除10取余法C.除2取余法D.除10取整法正确答案:C2、将十进制小数转换为二进制数一般采用()。

A.乘2取整法B.乘10取余法C.乘2取余法D.乘10取整法正确答案:A3、十进制数"13",用三进制表示为()。

A.211B.111C.112D.101正确答案:B4、将十进制数18转换成八进制是().A.20B.24C.22D.21正确答案:C5、十进制数25用8421 BCD码表示为()A.10 010100B.0010 0101C.10 101D.10 000101正确答案:B6、以下代码中为恒权码的是()。

A.余3循坏码B右移码C.5211 码D.余3码正确答案:C7、T立八进制数可以用()位二进制数来表示。

A.4B.3C.1D.2正确答案:B&十进制数43用8421BCD码表示为()。

A.10011B.0100 0011C.101011D.1000011正确答案:B9、A+BC=()A.AB+ACB.BCC・(A+B)(A+C)正确答案:C10、4变量逻辑函数的真值表,表中的输入变量的取值应有()种。

A.4B.2C.16D.8正确答案:C11、f 16选1的数据选择器,其选择控制(地址)输入端有()个,数据输入端有16个,输出端有1个。

A.4B.16C.1D.2正确答案:A12、一个译码器若有100个译码输出端,则译码输入端至少有()个。

A.5B.8C.7D.6正确答案:C13、能实现并-串转换的是()。

A.数据选择器B.数据分配器C.译码器D.数值比较器正确答案:A14、欲设计一个3位无符号数乘法器(即3x3),需要6位输入及()位输出信号。

B.6C.4D.5正确答案:B15、4位输入的二逬制译码器,其输出应有()位。

A.4B.1C.8D.16正确答案:D16、对于8线一3线优先编码器,下面说法正确的是()A.有8根输入线,8根输出线B.有8根输入线,3根输出线C.有3根输入线,8根输出线D.有3根输入线,3根输出线正确答案:B17、3线-8线译码电路是()译码器A.八进制B.三进制C.三位二进制D.H-A进制正确答案:C18、实现多输入、单输出逻辑函数,应选()。

(整理)《数字逻辑电路》试题2.

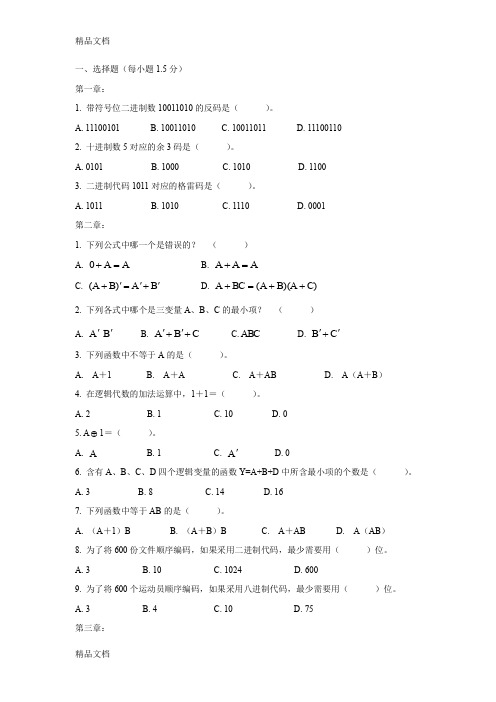

一、选择题(每小题1.5分)第一章:1. 带符号位二进制数10011010的反码是( )。

A. 11100101B. 10011010C. 10011011D. 111001102. 十进制数5对应的余3码是( )。

A. 0101B. 1000C. 1010D. 11003. 二进制代码1011对应的格雷码是( )。

A. 1011B. 1010C. 1110D. 0001第二章:1. 下列公式中哪一个是错误的? ( )A. A A 0=+B. A A A =+C. B A )B A ('+'='+D. )C A )(B A (BC A ++=+2. 下列各式中哪个是三变量A 、B 、C 的最小项? ( )A. B A ''B. C B A +'+'C.ABCD. C B '+'3. 下列函数中不等于A 的是( )。

A. A +1B. A +AC. A +ABD. A (A +B )4. 在逻辑代数的加法运算中,1+1=( )。

A. 2B. 1C. 10D. 05. A ⊕1=( )。

A. AB. 1C. A 'D. 06. 含有A 、B 、C 、D 四个逻辑变量的函数Y=A+B+D 中所含最小项的个数是()。

A. 3 B. 8 C. 14 D. 167. 下列函数中等于AB 的是( )。

A. (A +1)BB. (A +B )BC. A +ABD. A (AB )8. 为了将600份文件顺序编码,如果采用二进制代码,最少需要用( )位。

A. 3B. 10C. 1024D. 6009. 为了将600个运动员顺序编码,如果采用八进制代码,最少需要用( )位。

A. 3B. 4C. 10D. 75第三章:1. 采用漏极开路输出门电路(OD 门)主要解决了( )。

A. CMOS 门不能相“与”的问题B. CMOS 门的输出端不能“线与”的问题C. CMOS 门的输出端不能相“或”的问题2. 下列哪个特点不属于CMOS 传输门?( )A. CMOS 传输门属于双向器件。

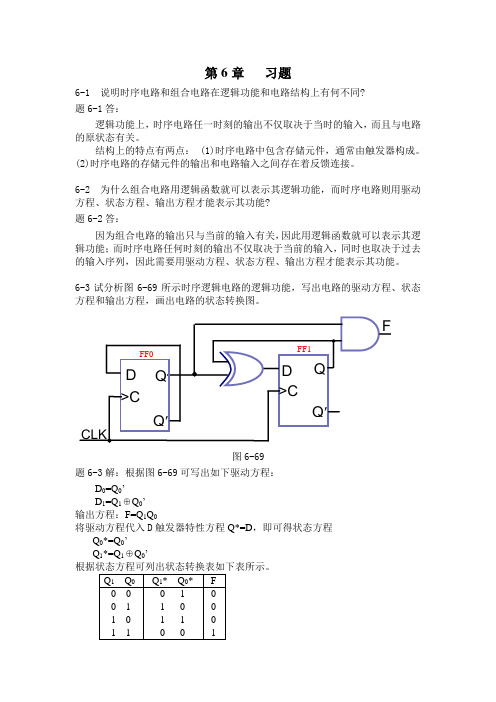

数字逻辑设计第6章 时序逻辑电路习题与解答

将方程代入 D 触发器的状态方程 Q*=D,得状态方程:

Q0*= Q0’,CLK 下降沿触发 Q1*=Q1’,Q0 上升沿触发 Q2*=Q2’, Q1 上升沿触发 根据状态方程可以画出 Q0、Q1、Q2 的波形图如下图所示,由图可见,该电路为 3 位异步二进制减法器。

6-14 用 74HCl61 构成的电路如图 6-77 所示,试分析其逻辑功能。

图 6-77 题 6-14 解:

由图可见,两个十六进制计数器 74HC161 形成级联方式,其中,161(1)的装

入值为 1100,进位输出 CO 接 161(2)的使能端 P 和 T,所以 161(1)为低 4 位,161(2) 为高 4 位,低 4 位计数达到 1111 时,进位输出 CO 有效,使下一时钟 CLK 上升沿 到达时,161(2)开始计数,而 161(2)计数达到 1111 时,其 CO 经反向形成装入 信号,高 4 位的装入值为 0011,所以在反复计数时,161(2)的计范围是从 0011 至 1111,而低 4 位的计数范围是从 1100 至 1111,整个 8 位从 00111100 到 11111111,其计数范围是从 60 到 255,共 196 个状态,所以该电路两片之间是 196 进制计数器。 6-15 试用 74HCl61 构成十一进制计数器。 题 6-15 解:

Q0*= Q0’ Q1*= Q0’Q1’+ Q0Q1 Q2*= Q0’Q1’Q2’+(Q0’Q1’)’Q2 根据状态方程可列出状态转换表如下:

C=1

C=0

Q2 Q1 Q0 000

Q2*Q1*Q0* 001

数字逻辑 第六章习题答案

根据真值表画出激励函数和输出函数卡诺图(略),化简后可 得:

(5) 画出逻辑电路图 根据激励函数和输出函数表达式,可画出实现给定功能的逻 辑电路如图11所示。该电路存在无效状态10,但不会产生挂 起现象,即具有自启动功能。

7 试用与非门构成的基本R-S触发器设计一个 脉冲异步模4加1计数器。 解(1) 设电路输入脉冲为x,状态变量为 y1y0,其状态表如表9所示。

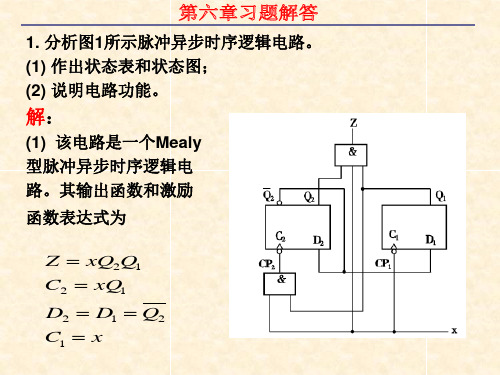

(2)该电路的状态图、状态表

(3)该电路是一个“x1—x2—x3”序列检测器。

4 分析图7所示脉冲异步时序电路,作出时间 图并说明该电路逻辑功能。

解:(1) 该电路是一个 Moore型脉冲异步时序逻辑 电路,其输出即电路状态。激 励函数表达式为

(2)电路次态真值表

(3)时间图

(4)该电路是一个模4计数器。

(4) 确定激励函数和输出函数 确定激励函数和输出函数时注意: ● 对于多余状态y2y1=10和不允许输入x2x1=11,可作为无关条 件处理; ● 当输入x2x1=00时,电路状态保持不变; ● 由于触发器时钟信号作为激励函数处理,所以,可假定次态 与现态相同时,触发器时钟信号为0,T端为d。 据此,可列出激励函数和输出函数真值表如表8所示。

(2) 根据状态表和RS触发器的功能表,可列出激 励函数真值表如表10所示。

Байду номын сангаас

(3)化简后,可得激 励函数最简表达式为:

(4)根据激励函数表达式,可画出逻辑电路 图如图12所示。

5 用D触发器作为存储元件,设计一个脉冲异 步时序电路。该电路在输入端x的脉冲作用 下,实现3位二进制减1计数的功能,当电 路状态为“000”时,在输入脉冲作用下输 出端Z产生一个借位脉冲,平时Z输出0。

数字电路习题库

一、选择题1、时序电路可由( )组成。

A.门电路B.触发器或触发器和门电路C.触发器或门电路D.组合逻辑电路 2、下列选项中不是时序电路组成部分的是( )。

A.门电路 B.组合逻辑电路 C.触发器 D.寄存器 3、时序电路由门电路和( )组合而成A.触发器B.寄存器C.加法器D.译码器 4、时序电路的输出状态的改变( )。

A.仅与该时刻输入信号的状态有关 B.仅与时序电路的原状态有关 C.与所述的两个状态都有关 D.与所述的两个状态都无关 5、时序逻辑电路中一定包含()。

A.触发器B.组合逻辑电路C.移位寄存器D.译码器 6、时序逻辑电路中必须有()。

A.输入逻辑变量B.时钟信号C.计数器D.编码器7、有一个与非门构成的基本RS 触发器,欲使该触发器保持原状态,即n n Q Q =+1, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S 8、有一个或非门构成的基本RS 触发器,欲使该触发器保持原状态,即n n Q Q =+1, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S 9、有一个与非门构成的基本RS 触发器,欲使该触发器01=+n Q, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S 10、有一个或非门构成的基本RS 触发器,欲使该触发器01=+n Q, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S 11、有一个与非门构成的基本RS 触发器,欲使该触发器11=+n Q, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S 12、有一个或非门构成的基本RS 触发器,欲使该触发器11=+n Q, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S13、对于JK 触发器,输入1,0==K J ,CP 脉冲作用后,触发器的次态应为()。

数字逻辑期末复习资料

第一章 数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD :二B 到十D 到BCD ,二B 到十六H ,二B 到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD 码表示;4、有权码和无权码有哪些?BCD 码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray 码 例:1、〔1100110〕B =〔0001 0000 0010〕8421BCD =〔102〕D =〔 66 〕H =〔146〕O〔178〕10=〔10110010〕2=〔0001 0111 1000 〕8421BCD =〔B2 〕16=〔 262〕8 2、将数1101.11B 转换为十六进制数为〔 A 〕A. D.C HB. 15.3HC. 12.E HD. 21.3H 3、在以下一组数中,最大数是〔 A 〕。

A.(258)D1 0000 0010B.(100000001 )B 257C.(103)H 0001 0000 0011259D.(001001010111 )8421BCD 2574、假设用8位字长来表示,〔-62〕D =( 1011 1110)原5、属于无权码的是〔B 〕A.8421 码B.余3 码 和 BCD Gray 的码C.2421 码D.自然二进制码 6、BCD 码是一种人为选定的0~9十个数字的代码,可以有许多种。

〔√〕 第二章 逻辑代数根底1、根本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与 逻辑乘 F=A+B 或 逻辑加F=A 非 逻辑反2、逻辑代数的根本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简〔有约束的和无约束的〕。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于〔 A 〕逻辑关系。

A 、与B 、或C 、非 2、数字电路中使用的数制是〔 A 〕。

《数字逻辑电路(A)》复习题第六章时序电路

时序逻辑电路一、选择题1同步计数器和异步计数器比较,同步计数器的显著优点是______________________________ 。

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制。

3.下列逻辑电路中为时序逻辑电路的是______________________________ 。

A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为______________________________ 的计数器。

A. NB. 2NC. N2D. 2N5.N个触发器可以构成能寄存_________________ 位二进制数码的寄存器。

A. N- 1B. NC. N+1D. 2N6.7.同步时序电路和异步时序电路比较,其差异在于后者____________________________ 。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关8. 一位8421 BCD码计数器至少需要 _________________个触发器。

A. 3B. 4C. 5D. 1 09.欲设计0 , 1 , 2, 3 , 4 , 5 , 6 , 7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用个触发器。

A. 2B. 3C. 4D. 810 . 8位移位寄存器,串行输入时经________________ 个脉冲后,8位数码全部移入寄存器中。

A. 1B. 2C. 4D. 8二、判断题(正确打",错误的打X)1•同步时序电路由组合电路和存储器两部分组成。

(V )2•组合电路不含有记忆功能的器件。

(V )3•时序电路不含有记忆功能的器件。

(X )4.同步时序电路具有统一的时钟CP控制。

(V )5.异步时序电路的各级触发器类型不同。

(X )6.环形计数器在每个时钟脉冲CP作用时,相临状态仅有一位触发器发生状态更新。

数字电子技术第六章时序逻辑电路

Qn1 J Qn K Qn

n 1

则求 Q2 时应得

___

n 1

Q2

a

Qn 2

Q2n

两式相比得

J ,

__

K

第六章 时序逻辑电路

故

___

Q n1 2

x Q2n

xQ1nQ2n

J2 x

_____

K2 xQ1n

___

Q1n1 xQ2n Q1n xQ1n

__

J1 xQ2n K1 x

第六章 时序逻辑电路

由图 6 - 15(a)~(d)可得

___ ___

Q4n1 Q1nQ2nQ3n Q4n Q1n Q4n

___ ___

___

Q3n1 Q1nQ2n Q3n Q1n Q3n Q2n Q3n

___ ______

Q1nQ2n Q3n Q1nQ2n Q3n

___ ___ ___

Q2n1 Q1n Q4n Q2n Q1n Q2n

___

Q1n1 Q1n

第六章 时序逻辑电路

由此得各触发器的激励函数为

J 4 Q1nQ2nQ3n

J3 Q1nQ2n

第六章 时序逻辑电路

根据方程可得出状态迁移表,如表 6 - 2 所示,再由表得 状态迁移图, 如图 6 -5 所示。

表 6 – 2 例 2 状态表

Q3n

Q2n

Q1n

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Q n1 3

0 0 0 1 0 0 0 0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时序逻辑电路

一、选择题

1.同步计数器和异步计数器比较,同步计数器的显著优点是。

A.工作速度高

B.触发器利用率高

C.电路简单

D.不受时钟C P控制。

3.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器

B.加法器

C.数码寄存器

D.数据选择器

4.N个触发器可以构成最大计数长度(进制数)为的计数器。

A.N

B.2N

C.N2

D.2N

5.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1

B.N

C.N+1

D.2N

6.

7.同步时序电路和异步时序电路比较,其差异在于后者。

A.没有触发器

B.没有统一的时钟脉冲控制

C.没有稳定状态

D.输出只与内部状态有关

8.一位8421B C D码计数器至少需要个触发器。

A.3

B.4

C.5

D.10

9.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同

步二进制计数器,最少应使用个触发器。

A.2

B.3

C.4

D.8

10.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1

B.2

C.4

D.8

二、判断题(正确打√,错误的打×)

1.同步时序电路由组合电路和存储器两部分组成。

(√)

2.组合电路不含有记忆功能的器件。

(√)

3.时序电路不含有记忆功能的器件。

(×)

4.同步时序电路具有统一的时钟CP控制。

(√)

5.异步时序电路的各级触发器类型不同。

(×)

6.环形计数器在每个时钟脉冲CP作用时,相临状态仅有一位触发器发生状态更新。

(×)

7.环形计数器如果不作自启动修改,则总有孤立状态存在。

(√)

8.计数器的模是指构成计数器的触发器的个数。

(×)

10.D触发器的特征方程Q n+1=D,而与Q n无关,所以,D触发器不是时序电路。

(×)

13.同步二进制计数器的电路比异步二进制计数器复杂,所以实际应用中较少使用同步二进制计数器。

(×)

14.利用反馈归零法获得N进制计数器时,若为异步置零方式,则状态S N只是短暂的过渡状态,不能稳定而是立刻变为0状态。

(√)

三、填空题

1.寄存器按照功能不同可分为两类:寄存器和寄存器。

2.数字电路按照是否有记忆功能通常可分为两类:、。

3.由四位环形移位寄存器构成的顺序脉冲发生器可产生个顺序脉冲。

4.时序逻辑电路按照其触发器是否有统一的时钟控制分为时序电路和

时序电路。

5.用电位触发的D触发器(同步式触发器)构成的寄存器称为。

6.n个触发器构成的环形计数器,其模数是,又是进制计数器,也是一个分频电路,也是一个顺序脉冲发生器。

该环形计数器自启动能力的。

7.n个触发器构成的扭环形计数器,其模数是,又是进制计数器,也是一个分频电路,该环形计数器自启动能力的。

四、时序电路的分析

1、分析以下电路,说明电路功能。

2、分析下图所示时序电路,作出状态表和状态图,指出其逻辑功能。

第七章答案

一、选择题

1.A

2.D

3.C

4.D

5.B

6.A

7.B

8.B

9.B

10. D

11. D

12. A

13. B

14.AB

15. A

16. C

二、判断题

1.√

2.√

3.√

4.√

5.×

6.×

7.√

8.×

9.× 10.×

11.√ 12.× 13.× 14.√

三、填空题

1.移位数码

2.组合逻辑电路时序逻辑电路

3.4

4.同步异步

5. 锁存器

6. N, n n n 无 7. 2n, 偶数,2n 无

四、1.(1)、01Q J = , 10Q J = , 110==K K (2)、n n Q Q Q 1011=+、 n n Q Q Q 0110=+

(3)、

(4)、

该电路是3进制减法计数器

2 .

驱动方程

状态方程:

一个五进制加法计数器。