集成电路封装和可靠性Chapter2-1-芯片互连技术

集成电路互连技术

4

1.2 集成电路对互连金属材料的要求

具有较小的电阻率 易于沉积和刻蚀 具有良好的抗电迁移特性

5

1.3 电迁移现象:

电迁移现象 是集成电路制造 中需要努力解决 的一个问题。特 别是当集成度增 加,互连线条变 窄时,这个问题 更为突出。

6

2、早期和目前应用最为广泛的 互连技术

7

2.1 早期互连技术----铝互连

在铝中加入硅饱和溶解度所需要的足量硅,形成Al-Si 合金,避免硅向铝中扩散,从而杜绝尖楔现象。

铝-掺杂多晶硅双层金属化结构 掺杂多晶硅主要起隔离作用。 铝-阻挡层结构

在铝与硅之间淀积一薄层金属,阻止铝与硅之间的作 用,从而限制Al尖楔问题。一般将这层金属称为阻挡层。

采用新的互连金属材料

解决Al/Si接触问题最有效的方法。

17

3.2 碳纳米管的结构

碳纳米管是由单层或多层石墨片按一定形式卷曲形成的中空 的无缝圆柱结构,是一种石墨晶体。碳纳米管的每层都是一 个C原子通过sp2杂化与旁边另外3个C原子结合在一起形成 六边形平面组成的圆柱。

18

3.3 碳纳米管的导电机制

碳纳米管的电子平均自由程约为1.6μm(室温下金属Cu的 电子平均自由程约为45nm ),如果碳纳米管长度小于这 个值,那么电子在碳纳米管中传输就可能为弹道输运,此 时碳纳米管的电阻跟管的长度无关 。

10

2.4 铝互连的不足(二):电迁移现象

电迁移现象的本质 是导体原子与通过该导 体电子流之间存在相互 作用,当一个铝金属粒 子被激发处于晶体点阵 电位分布的谷顶的时候, 它将受到两个方向相反 的作用力: (1)静电作用力, (2)“电子风”作用 力,

集成电路芯片封装技术培训课程(ppt-35页)全

微电子技术发展对封装的要求

四、高密度化和高引脚数

高密度和高I/O数造成单边引脚间距缩短、封装难

度加大:焊接时产生短路、引脚稳定性差

解决途径:

采用BGA技术和TCP(载带)技术

成本高、难以进行外观检查等。

微电子技术发展对封装的要求

五、适应恶劣环境

密封材料分解造成IC芯片键合结合处开裂、断路

解决办法:寻找密封替代材料

Ceramic

Ceramic or

Thin Film on Ceramic

Thin Film on PWB

PWB-D

•Integration to

BEOL

•Integration in

Package level

PWB-Microation at

System level

1、电源分配:传递电能-配给合理、减少电压损耗

2、信号分配:减少信号延迟和串扰、缩短传递线路

3、提供散热途径:散热材料与散热方式选择

4、机械支撑:结构保护与支持

5、环境保护:抵抗外界恶劣环境(例:军工产品)

确定封装要求的影响因素

成本

外形与结构

产品可靠性

性能

类比:人体器官的构成与实现

微电子封装技术的技术层次

芯片,但两类芯片的可靠性和成本不同。

封装材料

芯片封装所采用的材料主要包括金属、陶瓷、

高分子聚合物材料等。

问题:如何进行材料选择?

依据材料的电热性质、热-机械可靠性、技术和

工艺成熟度、材料成本和供应等因素。

表1.2-表1.4

封装材料性能参数

介电系数:表征材料绝缘程度的比例常数,相对值,通常介

电系数大于1的材料通常认为是绝缘材料。

集成电路封装和可靠性Chapter2-1-芯片互连技术【半导体封装测试】

UESTC-Ning Ning1Chapter 2Chip Level Interconnection宁宁芯片互连技术集成电路封装测试与可靠性UESTC-Ning Ning2Wafer InWafer Grinding (WG 研磨)Wafer Saw (WS 切割)Die Attach (DA 黏晶)Epoxy Curing (EC 银胶烘烤)Wire Bond (WB 引线键合)Die Coating (DC 晶粒封胶/涂覆)Molding (MD 塑封)Post Mold Cure (PMC 模塑后烘烤)Dejunk/Trim (DT 去胶去纬)Solder Plating (SP 锡铅电镀)Top Mark (TM 正面印码)Forming/Singular (FS 去框/成型)Lead Scan (LS 检测)Packing (PK 包装)典型的IC 封装工艺流程集成电路封装测试与可靠性UESTC-Ning Ning3⏹电子级硅所含的硅的纯度很高,可达99.9999 99999 %⏹中德电子材料公司制作的晶棒(长度达一公尺,重量超过一百公斤)UESTC-Ning Ning4Wafer Back Grinding⏹PurposeThe wafer backgrind process reduces the thickness of the wafer produced by silicon fabrication (FAB) plant. The wash station integrated into the same machine is used to wash away debris left over from the grinding process.⏹Process Methods:1) Coarse grinding by mechanical.(粗磨)2) Fine polishing by mechanical or plasma etching. (细磨抛光)UESTC-Ning Ning5旋转及振荡轴在旋转平盘上之晶圆下压力工作台仅在指示有晶圆期间才旋转Method:The wafer is first mounted on a backgrind tape and is then loaded to the backgrind machine coarse wheel . As the coarse grinding is completed, the wafer is transferred to a fine wheel for polishing .。

集成电路封装技术

集成电路封装技术一、概述集成电路封装技术是指将芯片封装成实际可用的器件的过程,其重要性不言而喻。

封装技术不仅仅是保护芯片,还可以通过封装形式的不同来满足不同应用领域的需求。

本文将介绍集成电路封装技术的基本概念、发展历程、主要封装类型以及未来发展趋势等内容。

二、发展历程集成电路封装技术随着集成电路行业的发展逐渐成熟。

最早的集成电路封装形式是引脚直插式封装,随着技术的不断进步,出现了芯片级、无尘室级封装技术。

如今,随着3D封装、CSP、SiP等新技术的出现,集成电路封装技术正朝着更加高密度、高性能、多功能的方向发展。

三、主要封装类型1.BGA封装:球栅阵列封装,是一种常见的封装形式,具有焊接可靠性高、散热性好等优点。

2.QFN封装:裸露焊盘封装,具有体积小、重量轻、成本低等优点,适用于尺寸要求严格的应用场合。

3.CSP封装:芯片级封装,在尺寸更小、功耗更低的应用场合有着广泛的应用。

4.3D封装:通过将多个芯片垂直堆叠,实现更高的集成度和性能。

5.SiP封装:系统级封装,将多个不同功能的芯片封装在一起,实现更复杂的功能。

四、未来发展趋势随着物联网、人工智能等领域的兴起,集成电路封装技术也将迎来新的挑战和机遇。

未来,集成电路封装技术将朝着更高密度、更低功耗、更可靠、更环保的方向发展。

同时,新材料、新工艺和新技术的应用将为集成电路封装技术带来更多可能性。

五、结语集成电路封装技术是集成电路产业链中至关重要的一环,其发展水平直接关系到整个集成电路的性能和应用范围。

随着技术的不断进步,集成电路封装技术也在不断演进,为各个领域的技术发展提供了强有力的支撑。

希望本文能够帮助读者更好地了解集成电路封装技术的基本概念和发展趋势,为相关领域的研究和应用提供一定的参考价值。

集成电路互连技术汇总

常规结构

2.5 目前应用最广泛的互连技术----铜互连

IBM 6层Cu互连表面结构图

2.6 以Cu作为互连材料的工艺流程

金属填充通孔 溅射势垒和籽晶层

淀积介质材料 CMP金属层

光刻引线沟槽图形

去掉刻蚀停止层

去掉光刻胶

光刻通孔图形 刻蚀引线沟槽

刻蚀通孔 去掉光刻胶

淀积刻蚀停止层

2.7 Cu互连存在的问题

合金,避免硅向铝中扩散,从而杜绝尖楔现象。 铝-掺杂多晶硅双层金属化结构

掺杂多晶硅主要起隔离作用。 铝-阻挡层结构

在铝与硅之间淀积一薄层金属,阻止铝与硅之间的作 用,从而限制Al尖楔问题。一般将这层金属称为阻挡层。 采用新的互连金属材料

解决Al/Si接触问题最有效的方法。

2.4 铝互连的不足(二):电迁移现象

铝互连的优点: 铝在室温下的

电阻率很低,与硅 和磷硅玻璃的附着 性很好,易于沉积 与刻蚀。由于上述 优点,铝成为集成 电路中最早使用的 互连金属材料。

2.2 铝互连的不足(一):Al/Si接触中的尖楔现象

Al Si

Al/Si接触中的 尖楔现象2.3 Al/Si接触的改进

Al-Si合金金属化引线 在铝中加入硅饱和溶解度所需要的足量硅,形成Al-Si

✓ a 尺寸太大 ✓ b 导电能力不符合发展需求

3、下一代互连材料与互连技术

3.1 下一代互联材料与互连技术:碳纳米管互连

碳纳米管于1991年发现以来, 就一直是纳米科学领域的研究 热点。

由于其超高电流密度承载能力 的特性(碳纳米管上可以通过 高达1010A/cm2的电流 ),引 起了集成电路器件制造领域专 家的关注。

1.2 集成电路对互连金属材料的要求

集成电路封装和测试复习题答案

一、填空题1、将芯片及其他要素在框架或基板上布置,粘贴固定以及连接,引出接线端子并且通过可塑性绝缘介质灌封固定的过程为狭义封装;在次根基之上,将封装体与装配成完整的系统或者设备,这个过程称之为广义封装。

2、芯片封装所实现的功能有传递电能;传递电路信号;提供散热途径;构造保护与支持。

3、芯片封装工艺的流程为硅片减薄与切割、芯片贴装、芯片互连、成型技术、去飞边毛刺、切筋成形、上焊锡、打码。

4、芯片贴装的主要方法有共晶粘贴法、焊接粘贴法、导电胶粘贴发、玻璃胶粘贴法。

5、金属凸点制作工艺中,多金属分层为黏着层、扩散阻挡层、表层金保护层。

6、成型技术有多种,包括了转移成型技术、喷射成型技术、预成型技术、其中最主要的是转移成型技术。

7、在焊接材料中,形成焊点完成电路电气连接的物质叫做煤斜;;用于去除焊盘外表氧化物,提高可焊性的物质叫做助焊剂;在SMT中常用的可印刷焊接材料叫做锡直。

8、气密性封装主要包括了金属气密性封装、陶瓷气密性封装、玻璃气密性封装。

9、薄膜工艺主要有遮射工艺、蒸发工艺、电镀工艺、光刻工艺。

10、集成电路封装的层次分为四级分别为模块元件(MOdUIe)、⅛路卡工艺(Card)、主电路板(Board)、完整电子产品。

11、在芯片的减薄过程中,主要方法有磨削、研磨、干式抛光、化学机械平坦工艺、电化学腐蚀、湿法腐蚀、等离子增强化学腐蚀等。

12、芯片的互连技术可以分为打线键合技术、载带自动键合技术、倒装芯片键合技术。

13、DBG切割方法进展芯片处理时,首先进展在硅片正面切割一定深度切口再进展反面磨削。

14、膜技术包括了薄膜技术和厚膜技术,制作较厚薄膜时常采用丝网印刷和浆料枯燥烧结的方法O15、芯片的外表组装过程中,焊料的涂覆方法有点涂、丝网印刷、钢模板印刷三种。

16、涂封技术一般包括了顺形涂封和封胶涂封。

二、名词解释1、芯片的引线键合技术(3种)是将细金属线或金属带按顺序打在芯片与引脚架或封装基板的焊垫上而形成电路互连,包括超声波键合、热压键合、热超声波键合。

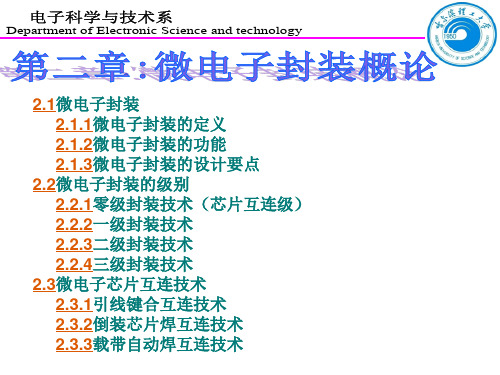

第二章 微电子封装概论(1)

第二步:将晶圆分布 图数字化,并将失效 芯片用红色标注,如 左图所示。

缺陷图样分析第二步

电子科学与技术系

Department of Electronic Science and technology

第三步:使用不同颜 色标注不同缺陷团簇, 如左图所示。 最后再通过与数据 库比对,完成缺陷图 样的分类。

2.2.1 零级封装技术(芯片互连级)

1.零级封装

零级封装是指半导体基片上的集成电路元件、器 件、线路;更确切地应该叫未加封装的裸芯片。 如果硬要说它是封装,是指圆片的切割到没有外 壳封装的集成电路的芯片,是由半导体厂商来完成 的,这种芯片可分为系列标准芯片和特殊用途的专 用芯片两种。 系统用户可从半导体厂家以这种裸芯片形式进货, 进行封装,经测试确保芯片质量合格后销售。

电子科学与技术系

Department of Electronic Science and technology

2.1.2 微电子封装的功能

微电子封装有5个功能如下:

1.电源分配: 微电子封装首先要通过电源使芯片电路能流通电流,但不 同部件所需的电源不同,要合理分配不同部件的电源,避免 器件被烧坏和不必要的电源损耗,这一点尤为重要。 2.信号分配: 为使电信号延迟尽可能减小,布线时应尽可能地使信号线 与芯片的互连路径,以及通过封装的 I/O引出路径达到最短。 对于高频信号,还应考虑信号的串扰,需进行合理的信号线 布线和地线布线。 3.机械支撑: 为芯片和其他部件提供牢固可靠的机械支撑,要能适应各 种工作环境和条件的变化。

缺陷图样分析第三步

电子科学与技术系

Department of Electronic Science and technology

2.贴膜 (Tape Attaching)

《集成电路封装与测试》芯片互连

引线键合技术

11

引线键合键合接点形状主要有楔形和球形,键合接点有两个,两 键合接点形状可以相同或不同。

球形键合

楔形键合

引线键合工艺参数

12

➢键合温度 WB 工艺对温度有较高的控制要求。过高的温度不仅会产生过多的氧化物影响键合质量,并

且由于热应力应变的影响,图像监测精度和器件的可靠性也随之下降。在实际工艺中,温控系 统都会添加预热区、冷却区,提高控制的稳定性,需要安装传感器监控瞬态温度 ➢键合时间

芯片焊区

芯片互连

I/O引线

半导体失效约有1/4-1/3是由芯片互连所引起,因此芯片互连对器件可靠性意义重大!!!

芯片互连技术概述

5

芯片托盘(DIE PAD)

芯片(CHIP)

L/F 内引脚 (INNER LEAD)

热固性环氧树脂 (EMC)

金线(WIRE)

L/F 外引脚 (OUTER LEAD)

IC 封装成品构造图

芯片互连常见方法

6

常见 方法

引线键合(又称打线键合)技术(WB) 载带自动键合技术(TAB)

倒装芯片键合技术(FCB)

这三种连接技术对于不同的封装形式和集成电路芯片集成度的限制各有不同的应用范围。 其中,FCB又称为C4—可控塌陷芯片互连技术。 打线键合适用引脚数为3-257;载带自动键合的适用引脚数为12-600;倒装芯片键合适用的引 脚数为6-16000。可见C4适合于高密度组装。

02 引线键合技术概述

引线键合技术

8

引线键合工程是引线架上的芯片与引线架之间用金线连接的工程。为了 使芯片能与外界传送及接收信号,就必须在芯片的接触电极与引线架的引脚 之间,一个一个对应地用键合线连接起来,这个过程称为引线键合。也称为 打线键合。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1Chapter 2Chip Level Interconnection芯片互连技术集成电路封装测试与可靠性UESTC-Ning Ning2Wafer InWafer Grinding (WG 研磨)Wafer Saw (WS 切割)Die Attach (DA 黏晶)Epoxy Curing (EC 银胶烘烤)Wire Bond (WB 引线键合)Die Coating (DC 晶粒封胶/涂覆)Molding (MD 塑封)Post Mold Cure (PMC 模塑后烘烤)Dejunk/Trim (DT 去胶去纬)Solder Plating (SP 锡铅电镀)Top Mark (TM 正面印码)Forming/Singular (FS 去框/成型)Lead Scan (LS 检测)Packing (PK 包装)典型的IC 封装工艺流程集成电路封装测试与可靠性UESTC-Ning Ning3⏹电子级硅所含的硅的纯度很高,可达99.9999 99999 %⏹中德电子材料公司制作的晶棒(长度达一公尺,重量超过一百公斤)UESTC-Ning Ning4Wafer Back Grinding⏹PurposeThe wafer backgrind process reduces the thickness of the wafer produced by silicon fabrication (FAB) plant. The wash station integrated into the same machine is used to wash away debris left over from the grinding process.⏹Process Methods:1) Coarse grinding by mechanical.(粗磨)2) Fine polishing by mechanical or plasma etching. (细磨抛光)UESTC-Ning Ning5旋转及振荡轴在旋转平盘上之晶圆下压力工作台仅在指示有晶圆期间才旋转Method:The wafer is first mounted on a backgrind tape and is then loaded to the backgrind machine coarse wheel . As the coarse grinding is completed, the wafer is transferred to a fine wheel for polishing .UESTC-Ning Ning6 Wafer Back Grinding processObjective:To reduce thethicknesswith a coarse grindingwheel.Objective:To load and alignthe wafer into thewafer cleaning andtape laminationmachine.Objective:To clean the waferfor the nextlamination step.Objective:To laminate a protectivelayer of film on thecircuitry surface of thewafer .2. Wafer cleaning1. Load and Align 3. Back grind Tape lamination4. Coarse grindingUESTC-Ning Ning7Wafer Back Grinding process (Cont.)Objective:To unload the wafer from back grinding machine.5. Fine polishing6. UnloadObjective:To load the wafer to wafer mounter.Objective:To remove the back grind tape afterwafer mounted on the frame.8. Tape removal7. LoadUESTC-Ning Ning8Wafer Back Grinding Issues and Challenges⏹Issues☐Ease of process–Thin wafer handling from one step to another –Back grinding tape removal–Excessive stresses removal or reduction from the wafer.(应力)☐Yield–Wafer breakage due to stress built up during thinning process. –Scratches .(划痕)–Die metallization smearing.(污点,模糊)☐Equipment stability and capability⏹Challenges☐Market requirements drive for very thin wafer (<3 mils)☐Flip chip wafer back grindingUESTC-Ning Ning9Wafer sawing⏹Wafer Separation Process►Purpose:The wafer separation process is to divide the wafer into individual dice or chips.Process Methods:1)Sawing (with diamond-impregnated saw blade) 锯切☐Single or dual cut ☐Step cut or bevel cut2) Partial scribing (with laser beam, diamond-tipped scribing tool, or diamond-impregnated saw blade) 局部划片器UESTC-Ning Ning10Wafer sawingUESTC-Ning Ning11►Wafer Sawing is a Front-of-Line (FOL) operation that cuts the wafer along the streets separating the individual die. Streets, also called scribe lines , are lines on the wafer that separate each individual die from the surrounding dice. Kerf width is the saw width. After the wafer is sawn, the wash station, using a detergent, removes residual cut material fromthe wafer.Wafer sawingDicing Blade晶圆工作台刀刃NingUESTC-Ning Ning13The SAWING process is broken down into four steps:Objective:To rinse slurry (silicon dust)before it dries with de-ionized water and CO2. Also to drywafer by pinning and with clean air , and unload wafer .1. Load and Align2. Pattern Recognition System (PRS)3. Cut4. Wash, Rinse, Dry and UnloadObjective:To separate dice from a wafer with resin-bonded diamond wheel . (First blade is used to remove metal structures and stresses on street for second blade.)Wafer sawingUESTC-Ning Ning14Wafer Sawing Issues and Challenges⏹Issues:☐Ease of process--Die chipping control (碎屑)--Multiple die types and sizes processing☐Yield--Saw on die--Scratches (划痕)--Chipping --Die crack☐Equipment stability and capability⏹Challenges:☐Smaller kerf width for more die per wafer☐Larger wafer size (300mm)with multiple die types and sizesUESTC-Ning Ning15--Die Attach Process☐Purpose:The die attach process is to attach the sawed die in the right orientation accurately onto the substrate with a bonding medium in between to enable the next wire bond first level interconnection operation .☐Process Methods1)Semi-automated eutectic die attach .低共熔物芯片粘接2)Fully automated adhesive die attach.胶粘剂粘接--Die Attach Process 晶粒--Die Attach Process☐Au-Si 低共熔合金粘接法金膜◆低共融合金粘接法主要用在芯片产品需要非常低的背部接触电阻。

--Die Attach ProcessUESTC-Ning Ning19--Die Attach ProcessUESTC-Ning Ning20 1. Units and Dice/ wafer LoadObjective:To load the carrierswith the units placedon them. To loadthe dice/wafer intothe machine.2. Bonding Medium DispenseObjective:To dispense thebonding mediumonto the substratedie attach paddle.3. Pattern Recognition System(PRS) & AlignObjective:To align the theta(rotation) position ofthe wafer. To align thedie (X-Y)with respectto the package PRSeye points.4. Die AttachObjective:To attach the dieprecisely and form agood adhesion withdesired bond linethickness (BLT).--Die Attach Process--Die Attach Process 5. Unload (Die Attach)UESTC-Ning Ning22Wire Bonding Technology Die Attach ProcessIssues and Challenges☐Issues:◆Ease of process–Delamination control –Void control ◆Yield–Adhesive on die–Incomplete wet out/fillet –Die crack–Die placement◆Equipment stability and capability☐Challenges:◆Market requirements drive for very thin die (<3 mils).◆Material selection (e.g. lead free compatible, thermal Materialselection and electrical requirements).UESTC-Ning Ning23--Wire Bonding ProcessUESTC-Ning Ning245. UnloadObjective:To unload the carriers after wire bond.To unload the wire spool when the wireis used upThe Wire Bonding Process --Wire Bonding ProcessUESTC-Ning Ning25Wire Bonding Issues and Challenges◆Challenges:☐Market requirements drive for tighter bond pitch . (<37/75um staggered , <60um non-staggered).☐Smaller wire diameter (<1.0mils).☐Brittle Intermetallic composition (IMC) on lead free.◆Issues:☐Ease of process-Looping profile control.-Process optimization for bond ability and bond reliability.☐Yield-Lifted bond (non stick on pad or lead).-Sagging and swayed wire. 引线塌陷或歪斜-Tight loop.☐Equipment stability and capability.交错排列无铅工艺中易脆的金属间化合物UESTC-Ning Ning26 MD(封塑)(Molding)BM(背印)(Back Mark)D/T(去胶/去纬)(Dejunk/Trim)SP(电镀)(Solder Panting)F/S(成型/去框)(Form/Singulation)F/T(功能测试)(Function/Test)PK(包装)(Packing)PMC(烘烤)(Post Mold Cure)MC(烘烤)(Mark Cure)TM(正印)(Top Mark)LS(检测)(lead Scan)Molding塑封成型UESTC-Ning Ning27按封装材料分类:陶瓷封裝常用于特殊用途和专业领域IC芯片例如:高频和军事通讯加盖式气密性封装UESTC-Ning NingUESTC-Ning Ning29☐Hermetic lid Sealing在第一级互连完成后,将周围印刷有焊料的盖子(或陶瓷,金属或塑料盖)放置在封装基板腔体上(芯片已键合在腔体内)。