数字逻辑设计习题参考答案(第4章)

数字电子技术第4章组合逻辑电路习题解答

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

习题4.2图解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.图解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题4.4图解:(1)ABD BC CD ABD BC CD L ++=••=B AC & && & D L B A =1 =1=1FF A B & &&& & F B A(3)4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)4.6试分析图所示电路的逻辑功能。

习题4.6图解:(1)ABC C B A F )(++=10电路逻辑功能为:“判输入ABC 是否相同”电路。

4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题4.7图解:(1)根据波形图得到真值表:C AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

数字逻辑课后习题答案(科学出版社_第五版)

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制49 110001 6153 110101 65127 1111111 177635 1001111011 11737.493 111.1111 7.7479.43 10011001.0110111 231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010 10 12111101 61 751011100 92 1340.10011 0.59375 0.46101111 47 5701101 13 153.将下列十进制数转换成8421BCD码1997=0001 1001 1001 011165.312=0110 0101.0011 0001 00103.1416=0011.0001 0100 0001 01100.9475=0.1001 0100 0111 01014.列出真值表,写出X的真值表达式A B C X0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1 X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1) (A⊕B)⊕C=A⊕(B⊕C)A B C (A⊕B)⊕C A⊕(B⊕C)0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 01 0 0 1 11 0 1 0 01 1 0 0 01 1 1 1 1所以由真值表得证。

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C0 0 0 1 10 0 1 0 00 1 0 0 00 1 1 1 11 0 0 0 01 0 1 1 11 1 0 1 11 1 1 0 07.证明下列等式(1)A+A B=A+B证明:左边= A+A B=A(B+B)+A B=AB+A B+A B=AB+A B+AB+A B=A+B=右边(2)ABC+A B C+AB C=AB+AC证明:左边= ABC+A B C+AB C= ABC+A B C+AB C+ABC=AC(B+B)+AB(C+C)=AB+AC=右边(3)EDCCDACBAA)(++++=A+CD+E 证明:左边=EDCCDACBAA)(++++=A+CD+A B C+CD E=A+CD+CD E=A+CD+E=右边(4) C B A C B A B A ++=C B C A B A ++ 证明:左边=C B A C B A B A ++=C B A C AB C B A B A +++)( =C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式9.将下列函数展开为最小项表达式 (1) F(A,B,C) = Σ(1,4,5,6,7)(2) F(A,B,C,D) = Σ(4,5,6,7,9,12,14) 10.用卡诺图化简下列各式(1)C AB C B BC A AC F +++=化简得F=C(2)C B A D A B A D C AB CD B A F++++=F=D A B A +(3) F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)化简得F=D BC D C A BC A C B D C ++++(4) F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)化简得F=AC AD B A ++11.利用与非门实现下列函数,并画出逻辑图。

数字逻辑_习题四_答案

习题四部分习题参考答案4.1 将下列函数简化,并用与非门和或非门画出逻辑电路图。

& (3)C B C A D C A B A D C B A F +++=),,,( 解:化简得F=C B C A B A ++F 的与非式为:F=C B C A B A •• ,逻辑电路图如图1所示。

F 的或非式为:F=C B A C B A C B A ABC F +++++=+=,逻辑电路图如图2所示。

图1 图2 4.3分析图4.59所示的逻辑电路图,并说明其逻辑功能。

解:(1)由逻辑电路图写出逻辑表达式并化简可得:DC D B D C D B F D BC D C B D C A D BC D C B D C A F CDABD CD ABD F +=⋅=++=⋅⋅=+=⋅=012(2)根据逻辑表达式,其逻辑功能如表所示。

1 C1&1&&&& &&ABF≥1 0 ≥1≥1≥1ACB ≥1≥1F由真值表可知,DCBA 表示的二进制数,当该值小于等于5,F0=1,当当该值小于等于10,大于5,F1=1,当该值小于等于15,大于10,F2=1。

4.4 试分析图4.60 所示的码制转换电路的工作原理答:①写出逻辑表达式001G B B =⊕ 112G B B =⊕ 223G B B =⊕ 33G B =D C B A F2 F1 F0 输 入 输 出0 00 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 1 0 1 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 0 0 1 0 0 1 1 1 0 1 0 1 0 0 0 0 1 0 1 0 0 1 0 1 0 1 0 1 0 0 1 0 1 0 1 1 1 0 0 1 1 0 0 1 0 0 1 1 0 1 1 0 0 1 1 1 0 1 0 0 1 1 1 1 1 0 0③由真值表可以发现,任意相邻的两个代码之间只有一位不同,而其余各位均相同。

数字逻辑设计第三版第四章答案

WX 00 YZ

W

01

11

⋅ Z 01 1 1 1 Z 11 10 d 1 Y W⋅X⋅Y X F = W ′ ⋅ Y′ ⋅ Z + W ′ ⋅ X′ ⋅ Z + W ⋅ X ⋅ Y + W′ ⋅ X′ ⋅ Y′ or X′ ⋅ Y′ ⋅ Z′ X′ + Y + Z 01 0 (a) W + X′ + Z X′ + Y′ + Z′ WX 00 YZ 00 01 11 10 W 11 0 0 0 0 X d 10 d 0 Z 0 W′ + Y W′ + X (b) W + X′ + Y′ Y 0 0 X + Y′ + Z W′ + Z W + Y′ + Z F = (W + X′ + Y′) ⋅ (X′ + Y + Z) ⋅ (W′ + Z′) ⋅ (X + Y′ + Z)

X 01 11 1 1 Y F=X⋅Y+Z (b) 1 1 Z Z 10 X⋅Y YZ W′ ⋅ Y′ ⋅ Z 00 01 11 Y 10 1 X F = W′ ⋅ X + X′ ⋅ Y′ ⋅ Z + X ⋅ Y 1 X⋅Y 1 W 01 1 1 1 1 1 Z 11 10 W′ ⋅ X X′ ⋅ Y′ ⋅ Z′

4.28

X Y

4.29

课

4.31

4.35

w.

4.39

ww

4.37 Figure 3–4(d) is more appropriate, since electrically a TTL NOR gate is just the wired-AND of inverters. (a) True. If A ⋅ B = 0 then either A = 0 or B = 0 . If A + B = 1 then either A = 1 or B = 1 . Therefore,

数字逻辑设计习题参考答案(第4章)

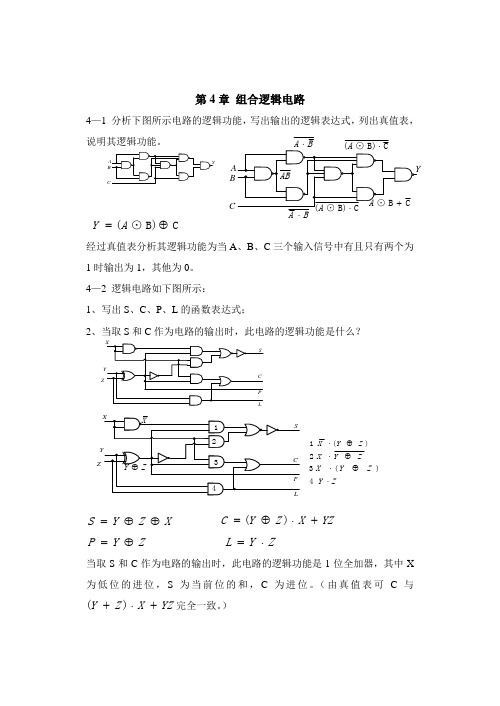

第4章 组合逻辑电路4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

C B)⊙(⊕=A Y经过真值表分析其逻辑功能为当A 、B 、C 三个输入信号中有且只有两个为1时输出为1,其他为0。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?X Z Y S ⊕⊕= YZ X Z Y C +⋅⊕=)(Z Y P ⊕= Z Y L ⋅=当取S 和C 作为电路的输出时,此电路的逻辑功能是1位全加器,其中X 为低位的进位,S 为当前位的和,C 为进位。

(由真值表可C 与YZ X Z Y +⋅+)(完全一致。

)ZB CBA ⋅CB)⊙(⋅A Z)(Z Y X ⊕⋅ZY X ⊕⋅)(Z Y X ⊕⋅ZY ⋅12344—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

Z Y X F ⊕⊕=1 Z Y X F ⋅⊕=)(2Z XY Z XY F +⋅=3 XYZ F =44—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出1P 和2P 的表达式,列出真值表,说明其逻辑功能。

ABC C B A m m m m Y Y P +⋅⋅=+=⋅=⋅=70707016543216543212m m m m m m Y Y Y Y Y Y P +++++=⋅⋅+⋅⋅=C B C A B A ++=P1的逻辑功能为当三个输入信号完全一致时输出为1。

P2的逻辑功能为当上输入信号不完全一致时输出为1。

4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备出故障时,指示灯红灯和黄灯都亮。

1234解:设输入变量A 、B 、C 分别对应三台设备的状态,0表示故障,1表示正常;输出变量X 、Y 、Z 表示绿、黄、红三个灯的亮灭,0表示灭,1表示亮,根据题意可得真值表如下:设ABC 分别连入74LS138的A 2A 1A 0 由真值表得 42104210Y Y Y Y m m m m Y ⋅⋅⋅=+++=6530Y Y Y Y Z ⋅⋅⋅=4—6 下图3.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

数字逻辑电路与系统设计蒋立平主编习题解答

第4章习题及解答用门电路设计一个4线—2线二进制优先编码器。

编码器输入为3210A A A A ,3A 优先级最高,0A 优先级最低,输入信号低电平有效。

输出为10Y Y ,反码输出。

电路要求加一G 输出端,以指示最低优先级信号0A 输入有效。

题 解:根据题意,可列出真值表,求表达式,画出电路图。

其真值表、表达式和电路图如图题解所示。

由真值表可知3210G A A A A =。

(a)0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 0 1 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 10000000000000000000000000010100011111010110000103A 2A 1A 0A 1Y 0Y G真值表≥1&1Y 3A 2A 1&&1A 0Y &1GA 00 01 11 100010001111000000001101113A 2A 1A 0A 03231Y A A A A =+00 01 11 1000000011110001000011103A 2A 1A 0A 132Y A A =(b) 求输出表达式(c) 编码器电路图图 题解4.1试用3线—8线译码器74138扩展为5线—32线译码器。

译码器74138逻辑符号如图(a )所示。

题 解:5线—32线译码器电路如图题解所示。

&&&&11EN01234567BIN/OCTENY 0&G 1G 2AG 2B42101234567BIN/OCTEN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B421A 0A 1A 2A 3A 4Y 7Y 8Y 15Y 16Y 23Y 24Y 31图 题解4.3写出图所示电路输出1F 和2F 的最简逻辑表达式。

第四章1 《数字逻辑》(第二版)习题答案

第四章1.分析图1所示的组合逻辑电路,说明电路功能,并画出其简化逻辑电路图。

图1 组合逻辑电路解答○1根据给定逻辑电路图写出输出函数表达式CA B CBA B CAA B CF⋅+⋅+⋅=○2用代数法简化输出函数表达式CBA ABC CBA ABC C)B(A ABCCABCBABCAABCF+ =+ ++ =+ +=⋅+⋅+⋅=○3由简化后的输出函数表达式可知,当ABC取值相同时,即为000或111时,输出函数F的值为1,否则F的值为0。

故该电路为“一致性电路”。

○4实现该电路功能的简化电路如图2所示。

图24.设计一个组合电路,该电路输入端接收两个2位二进制数A=A2A1,B=B2B1。

当A>B时,输出Z=1,否则Z=0。

解答○1根据比较两数大小的法则,可写出输出函数表达式为○2根据所得输出函数表达式,可画出逻辑电路图如图6所示。

图66.假定X=AB代表一个2位二进制数,试设计满足如下要求 (2) Y=X3(Y也用二进制数表示。

)○1假定AB表示一个两位二进制数,设计一个两位二进制数立方器。

由题意可知,电路输入、输出均为二进制数,输出二进制数的值是输入二进制数AB的立方。

由于两位二进制数能表示的最大十进制数为3,3的立方等于27,表示十进制数27需要5位二进制数,所以该电路应有5个输出。

假定用TWXYZ表示输出的5位二进制数,根据电路输入、输出取值关系可列出真值表如表4所示。

由真值表可写出电路的输出函数表达式为T=AB,====BWAB,ZA,Y0,X根据所得输出函数表达式,可画出用与非门实现给定功能的逻辑电路图如图9所示。

图98.设计一个“四舍五入”电路。

该电路输入为1位十进制数的8421码,当其值大于或等于5时,输出F 的值为1,否则F 的值为0。

解答○1 根据题意,可列出真值表如表5所示。

表5○2 由真值表可写出输出函数表达式为 F(A,B,C,D)=∑m(5~9)+∑d(10~15)经化简变换后,可得到最简与非表达式为○3逻辑电路图如图11所示。

数字逻辑课后答案 第四章

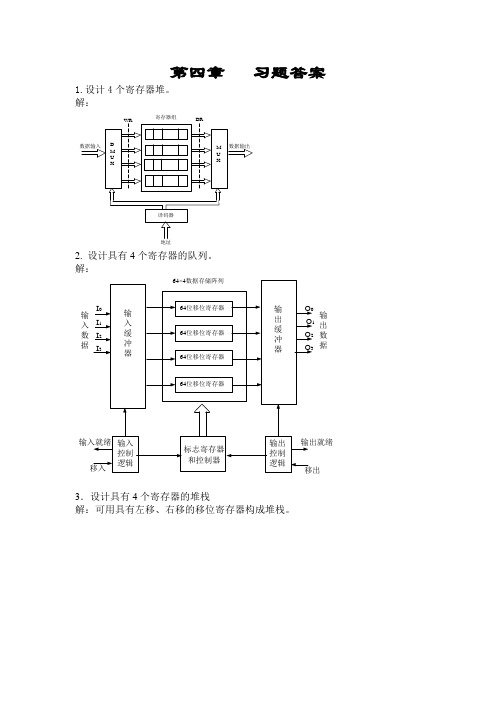

第四章 习题答案1.设计4个寄存器堆。

解:2. 设计具有4个寄存器的队列。

解:3.设计具有4个寄存器的堆栈解:可用具有左移、右移的移位寄存器构成堆栈。

寄存器组输入数据输出数据4.SRAM 、DRAM 的区别解:DRAM 表示动态随机存取存储器,其基本存储单元是一个晶体管和一个电容器,是一种以电荷形式进行存储的半导体存储器,充满电荷的电容器代表逻辑“1”,“空”的电容器代表逻辑“0”。

数据存储在电容器中,电容存储的电荷一般是会慢慢泄漏的,因此内存需要不时地刷新。

电容需要电流进行充电,而电流充电的过程也是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的。

DRAM 拥有更高的密度,常常用于PC 中的主存储器。

SRAM 是静态的,存储单元由4个晶体管和两个电阻器构成,只要供电它就会保持一个值,没有刷新周期,因此SRAM 比DRAM 要快。

SRAM 常常用于高速缓冲存储器,因为它有更高的速率;5. 为什么DRAM 采用行选通和列选通解:DRAM 存储器读/写周期时,在行选通信号RAS 有效下输入行地址,在列选通信号CAS 有效下输入列地址。

如果是读周期,此位组内容被读出;如果是写周期,将总线上数据写入此位组。

由于DRAM 需要不断刷新,最常用的是“只有行地址有效”的方法,按照这种方法,刷新时,是在RAS 有效下输入刷新地址,存储体的列地址无效,一次选中存储体中的一行进行刷新。

每当一个行地址信号RAS 有效选中某一行时,该行的所有存储体单元进行刷新。

6. 用ROM 实现二进制码到余3码转换 解: 真值表如下:8421码 余三码B B BG G G栈顶SR 1SR 2SR 3输入数据输出数据压入弹出3232BG0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 10 0 110 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 0最小项表达式为: G=G=G=G=阵列图为:7. 用ROM 实现8位二进制码到8421码转换10103∑)9,8,7,6,5(2∑)9,4,3,2,1(1∑)8,7,4,3,0(0∑)8,6,4,2,0(G 3G 2G 1G 0B 3B 2B 1B B 0解:输入为8位二进制数,输出为3位BCD码,12位二进制数,所以,所需8ROM的容量为:2*12=30728.ROM、EPROM和EEPROM的区别解:ROM 指的是“只读存储器”,即Read-Only Memory。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第4章 组合逻辑电路

4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

C B)⊙(⊕=A Y

经过真值表分析其逻辑功能为当A 、B 、C 三个输入信号中有且只有两个为1时输出为1,其他为0。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;

2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?

X Z Y S ⊕⊕= YZ X Z Y C +⋅⊕=)(

Z Y P ⊕= Z Y L ⋅=

当取S 和C 作为电路的输出时,此电路的逻辑功能是1位全加器,其中X 为低位的进位,S 为当前位的和,C 为进位。

(由真值表可C 与

YZ X Z Y +⋅+)(完全一致。

)

Z

B C

B

A ⋅C

B)⊙(⋅A Z

)

(Z Y X ⊕⋅Z

Y X ⊕⋅)(Z Y X ⊕⋅Z

Y ⋅1234

4—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

Z Y X F ⊕⊕=1 Z Y X F ⋅⊕=)(2

Z XY Z XY F +⋅=3 XYZ F =4

4—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出1P 和

2P 的表达式,列出真值表,说明其逻辑功能。

ABC C B A m m m m Y Y P +⋅⋅=+=⋅=⋅=7070701

6543216543212m m m m m m Y Y Y Y Y Y P +++++=⋅⋅+⋅⋅=

C B C A B A ++=

P1的逻辑功能为当三个输入信号完全一致时输出为1。

P2的逻辑功能为当上输入信号不完全一致时输出为1。

4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备出故障时,指示灯红灯和黄灯都亮。

1234

解:设输入变量A 、B 、C 分别对应三台设备的状态,0表示故障,1表示正常;输出变量X 、Y 、Z 表示绿、黄、红三个灯的亮灭,0表示灭,1表示亮,根据题意可得真值表如下:

设ABC 分别连入74LS138的A 2A 1A 0 由真值表得 42104210Y Y Y Y m m m m Y ⋅⋅⋅=+++=

6530Y Y Y Y Z ⋅⋅⋅=

4—6 下图3.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

将G1 G0 及A 带入并化简得:

当G1 G0为00时Y=A;01、11时B A Y ⊕=;10时Y=AB;

777Y m m X ===

Y

Z X

)

()()()(0 )()()(1)(0012012012012012012012012A A A B A A A B A A A B A A A A A A B A A A B A A A A A A Y +++⋅

+

++⋅+=)(0010B A G AB G A G G Y ⊕++=G A

4—7仿照全加器设计一个全减器,被减数为A ,减数为B ,低位来的借位为C ,差为D ,向上借一位为J 。

要求:1.写出真值表,写出D 与J 的表达式;2.用译码器74LS138和必要的基本门电路实现此电路;3.用双四选一数据选择器实现。

C B A

D ⊕⊕=

C B A B A J )(++=

4—8 设计一组合逻辑电路,输入为四位二进制码3B 2B 1B 0B ,当

3B 2B 1B 0B 是BCD8421码时输出1=Y ;否则0=Y 。

列出真值表,写出

与或非表达式,用集电极开路门实现。

2313123B B B B B B B Y ⋅=⋅+=

D

J

B2B3B1

Y

4—9 设计一个多功能组合数字电路,实现下表所示逻辑功能。

表中1C 0C 为功能选择输入信号;A ,B 为输入变量;F 为输出。

1.列出真值表,写出F 的表达式;

若将0C AB 分别连接8选1数据选择器74LS151的A 2A 1A 0可得表达式: 与74LS151的逻辑表达式比较可画出电路图 4—10分析图4.10(a )所示电路:

1.写出L ,Q ,G 的表达式,列出真值表,说明它完成什么逻辑功能。

2.用图4.10(a )所示电路与集成四位数码比较器(如图4.10(b )所示)构成一个五位数码比较器。

由电路图得:B A L =

B A G = B ⊙A Q =

该电路完成1位数值比较器的功能:L 为A 小于B ,G 为A 大于B ,Q 为相等。

若组成五位比较器将L 、G 与

Q 分别连入74LS85的A<B ,A>B 及A=B

7

4321)

742

1(1)7321(111m m C m C m m m m m m C m m m m C F +⋅+⋅++=

+++⋅++++⋅=C 1

1”

引脚即可。

图4.10(a)

图4.10(b)。