数字逻辑与数字系统四五六章答案

数字逻辑与数字系统设计习题参考答案

(4)(0.785)10=(0.011110000101)8421BCD

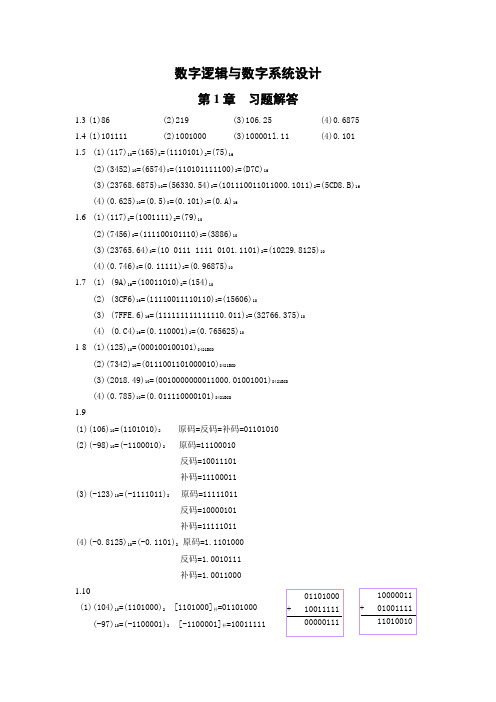

1.9

(1)(106)10=(1101010)2原码=反码=补码=01101010

(2)(-98)10=(-1100010)2原码=11100010

不考虑无关项,化简后的表达式:

F=

按考虑无关项化简结果绘制的逻辑电路习题4.10图(a)所示:

习题4.10图(a)

按不考虑无关项化简结果绘制的逻辑电路如习题4.10图(b)所示

习题4.10图(b)

4.11解:这是一个优先编码器的问题,设特快为A,直快为B,慢车为C,没有开车要求,输出为0,若A要求开车则输出,1,B要求开车输出为2,C要求开车输出3,根据A-B-C的优先顺序列功能表如下:

4.6解:根据题意:F= ,所以,可绘制电路如习题4.6图所示

习题4.6图

4.7解:根据题意:F= ,所以,可绘制电路如习题4.7图所示

习题4.7图

4.8解:

习题4.8图

4.9解:根据题意,三个变量有两个为1的卡诺图如习题4.9图(a)所示:

习题4.9图(a)

由此可列出逻辑表达式为:F= ,根据逻辑表达式可绘制逻辑电路习题4.9图(b)所示:

输入

输出

A

B

C

T1

T0

0

0

0

0

0

0

0

1

1

1

0

1

0

1

0

0

1

1

1

0

1

0

0

0

1

1

0

白中英数字逻辑习题答案

T2.1 分析下图所示的逻辑电路,写出表达式并进行简化。

A B

F

F = AB + B = AB

A

B

F

C

F = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC

T2.2 分析下图所示的逻辑电路,写出表达式并进行简化。

A

AD

BD

B

BD

F

BC

C CD

D

[解]

T2.5 右图所示为数据总线上的一种判零电路,写出F的逻辑表达式, 说明该电路的逻辑功能。

A0

A3 A4

A7

F

A8

A11 A12

A15

[解]

F= A0A1A2A3+A4A5A6A7+A8A9A10A11+A12A13A14A15 = A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15

[解] 先由 F→ F’,在由 F’→ F,得: F = A + B+C

(2) F(A,B,C,D) = Σ(0,1,5,7,10,11,12,13,14,15)

AB CD 00 01 11 10

00 1

1

01 1 1 1

[解1] F = A B C + AB + BD + AC = A+B+C + A+B + B+D + A+C

AB CD 00 01 11 10

00

111

01 1 1

1

11 1

1

10

1

ABCD F

数字逻辑设计习题参考答案(第6章)

第6章时序逻辑电路6—1 从概念,结构和功能描述等几个方面简述时序逻辑电路和组合逻辑电路的不同。

概念:组合逻辑电路在任一时刻的输出仅由该时刻的输入决定,而与过去的状态无关,电路无记忆功能。

时序逻辑电路任一时刻的输出信号不仅取决于该时刻的输入信号,而且还取决于电路原来的状态。

结构:组合电路都是单纯由逻辑门组成,且输出不存在反馈路径。

时序逻辑电路由组合逻辑电路和存储电路组成,输出和输入之间有反馈。

存储电路一般由触发器构成。

功能描述:组合逻辑电路一般用逻辑图、逻辑表达式和真值表描述。

时序逻辑一般用逻辑图、逻辑方程式(状态方程、输出方程、驱动方程)、状态转换表、状态转换图和时序图来描述。

6—2 作出与表1所示状态表对应的状态图。

6—3 用边沿触发D触发器和与非门设计一个三位右移寄存器,用一控制端X控制,当0=X时能串行输入新数据ID,当1=X时具有自循环功能。

A BD C2111/10X/010/011/010/001/101/010/011/000/001/1QQSETCLRDQQSETCLRDQQSETCLRDXD ID OCP6—4 完成下列设计:1. 画出用J-K 触发器实现的四位右移寄存器的逻辑图(数据向高位移位定义为右移,寄存器的输出1Q 2Q 3Q 4Q ,设4Q 为高位。

2. 用上述四位右移寄存器实现下列计数器,写出设计步骤,画出逻辑图。

CP 1Q 2Q 3Q 4Q0 0 0 0 0 11 0 0 02 0 1 0 0 31 0 1 0 4 0 1 0 1 5 0 0 1 0 6 0 0 0 1 70 0 0 0答:由题意知,计数器是由右移寄存器实现的,所以只要确定第一个JK 触发器的驱动方程即可。

根据给出的状态转换表,可得卡诺图。

化简得43Q Q Q Q Q Q D ++=⋅⋅=6—5 用一片74LS161和必要的门电路构成一个可控计数器。

当控制端C=1时,实现八进制计数;C=0时,实现四进制数。

数字逻辑(科学出版社第五版)课后习题答案综述

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制49 110001 6153 110101 65127 1111111 177635 1001111011 11737.493 111.1111 7.7479.43 10011001.0110111 231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010 10 12111101 61 751011100 92 1340.10011 0.59375 0.46101111 47 5701101 13 153.将下列十进制数转换成8421BCD码1997=0001 1001 1001 011165.312=0110 0101.0011 0001 00103.1416=0011.0001 0100 0001 01100.9475=0.1001 0100 0111 01014.列出真值表,写出X的真值表达式A B C X0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1 X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1) (A⊕B)⊕C=A⊕(B⊕C)A B C (A⊕B)⊕C A⊕(B⊕C)0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 01 0 0 1 11 0 1 0 01 1 0 0 01 1 1 1 1所以由真值表得证。

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C0 0 0 1 10 0 1 0 0 0 1 0 0 0 0 1 1 1 1 1 0 0 0 0 1 0 1 1 1 1 1 0 1 1 1 1 1 0 07.证明下列等式(1) A+A B=A+B证明:左边= A+A B =A(B+B )+A B =AB+A B +A B =AB+A B +AB+A B =A+B =右边(2) ABC+A B C+AB C =AB+AC证明:左边= ABC+A B C+AB C = ABC+A B C+AB C +ABC =AC(B+B )+AB(C+C ) =AB+AC =右边(3) E D C CD A C B A A )(++++=A+CD+E 证明:左边=E D C CD A C B A A )(++++ =A+CD+A B C +CD E =A+CD+CD E =A+CD+E =右边(4) C B A C B A B A ++=C B C A B A ++证明:左边=C B A C B A B A ++=C B A C AB C B A B A +++)( =C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式9.将下列函数展开为最小项表达式 (1) F(A,B,C) = Σ(1,4,5,6,7)(2) F(A,B,C,D) = Σ(4,5,6,7,9,12,14) 10.用卡诺图化简下列各式(1)C AB C B BC A AC F +++=化简得F=C(2)C B A D A B A D C AB CD B A F++++=F=D A B A +(3) F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)化简得F=D BC D C A BC A C B D C ++++(4) F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)化简得F=AC AD B A ++11.利用与非门实现下列函数,并画出逻辑图。

数字逻辑与数字系统设计习题参考答案

input a,b,c,d;

output f;

reg f;

always @(a or b or c or d)

case({a,b,c,d})

4'b0011: f<=1'b1;

4'b0100: f<=1'b1;

4'b0101: f<=1'b1;

4'b1010: f<=1'b1;

W=∑m(5,6,7,8,9)+∑d(10,11,12,13,14,15)

X=∑m(1,2,3,4,9)+∑d(10,11,12,13,14,15)

Y=∑m(0,3,4,7,8)+∑d(10,11,12,13,14,15)

Z=∑m(0,2,4,6,8)+∑d(10,11,12,13,14,15)

用卡诺图化简得:

[104-97]补=01101000+10011111=00000111, 104-97=(00000111)2=7

(2)(-125)10=(-1111101)2[-1111101]补=10000011

(79)10=(01001111)2[01001111]补=01001111

[-125+79]补=10000011+01001111=11010010,-125+79=(-0101110)2=-46

(5)F=∑m(1,2,3,4,5,6)

(6)F=∑m(4,7,8,11)

2.9解:

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

或=

数字逻辑课后答案 第四章

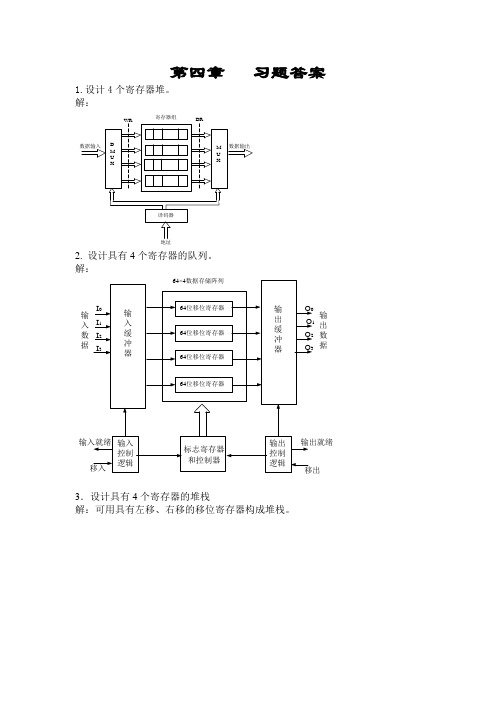

第四章 习题答案1.设计4个寄存器堆。

解:2. 设计具有4个寄存器的队列。

解:3.设计具有4个寄存器的堆栈解:可用具有左移、右移的移位寄存器构成堆栈。

寄存器组输入数据输出数据4.SRAM 、DRAM 的区别解:DRAM 表示动态随机存取存储器,其基本存储单元是一个晶体管和一个电容器,是一种以电荷形式进行存储的半导体存储器,充满电荷的电容器代表逻辑“1”,“空”的电容器代表逻辑“0”。

数据存储在电容器中,电容存储的电荷一般是会慢慢泄漏的,因此内存需要不时地刷新。

电容需要电流进行充电,而电流充电的过程也是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的。

DRAM 拥有更高的密度,常常用于PC 中的主存储器。

SRAM 是静态的,存储单元由4个晶体管和两个电阻器构成,只要供电它就会保持一个值,没有刷新周期,因此SRAM 比DRAM 要快。

SRAM 常常用于高速缓冲存储器,因为它有更高的速率;5. 为什么DRAM 采用行选通和列选通解:DRAM 存储器读/写周期时,在行选通信号RAS 有效下输入行地址,在列选通信号CAS 有效下输入列地址。

如果是读周期,此位组内容被读出;如果是写周期,将总线上数据写入此位组。

由于DRAM 需要不断刷新,最常用的是“只有行地址有效”的方法,按照这种方法,刷新时,是在RAS 有效下输入刷新地址,存储体的列地址无效,一次选中存储体中的一行进行刷新。

每当一个行地址信号RAS 有效选中某一行时,该行的所有存储体单元进行刷新。

6. 用ROM 实现二进制码到余3码转换 解: 真值表如下:8421码 余三码B B BG G G栈顶SR 1SR 2SR 3输入数据输出数据压入弹出3232BG0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 10 0 110 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 0最小项表达式为: G=G=G=G=阵列图为:7. 用ROM 实现8位二进制码到8421码转换10103∑)9,8,7,6,5(2∑)9,4,3,2,1(1∑)8,7,4,3,0(0∑)8,6,4,2,0(G 3G 2G 1G 0B 3B 2B 1B B 0解:输入为8位二进制数,输出为3位BCD码,12位二进制数,所以,所需8ROM的容量为:2*12=30728.ROM、EPROM和EEPROM的区别解:ROM 指的是“只读存储器”,即Read-Only Memory。

数字逻辑(第六版 白中英)课后习题答案

第四章习题答案1.设计4个寄存器堆。

解:2. 设计具有4个寄存器的队列。

解:3.设计具有4个寄存器的堆栈解:可用具有左移、右移的移位寄存器构成堆栈。

4.SRAM、DRAM的区别解:DRAM表示动态随机存取存储器,其基本存储单元是一个晶体管和一个电容器,是一种以电荷形式进行存储的半导体存储器,充满电荷的电容器代表逻辑“1”,“空”的电容器代表逻辑“0”。

数据存储在电容器中,电容存储的电荷一般是会慢慢泄漏的,因此内存需要不时地刷新。

电容需要电流进行充电,而电流充电的过程也是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的。

DRAM拥有更高的密度,常常用于PC中的主存储器。

SRAM是静态的,存储单元由4个晶体管和两个电阻器构成,只要供电它就会保持一个值,没有刷新周期,因此SRAM 比DRAM要快。

SRAM常常用于高速缓冲存储器,因为它有更高的速率;5. 为什么DRAM采用行选通和列选通解:DRAM存储器读/写周期时,在行选通信号RAS有效下输入行地址,在列选通信号CAS有效下输入列地址。

如果是读周期,此位组内容被读出;如果是写周期,将总线上数据写入此位组。

由于DRAM需要不断刷新,最常用的是“只有行地址有效”的方法,按照这种方法,刷新时,是在RAS有效下输入刷新地址,存储体的列地址无效,一次选中存储体中的一行进行刷新。

每当一个行地址信号RAS有效选中某一行时,该行的所有存储体单元进行刷新。

6. 用ROM实现二进制码到余3码转换解:真值表如下:8421码余三码B B2B1 B0G G2G 1G00 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 03310 1 1 00 1 1 11 0 0 01 0 0 1 01 0 0 11 0 1 01 0 1 11 1 0 0最小项表达式为:G=∑)9,8,7,6,5(G2=∑)9,4,3,2,1(G1=∑)8,7,4,3,0(G0=∑)8,6,4,2,0(阵列图为:7. 用ROM实现8位二进制码到8421码转换解:输入为8位二进制数,输出为3位BCD码,12位二进制数,所以,所需ROM的容量为:28*12=30728.ROM、EPROM和EEPROM的区别解:ROM 指的是“只读存储器”,即Read-Only Memory。

数字逻辑电路与系统设计第6章习题及解答.docx

第6章题解:6.1试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余 3BCD 码计数器。

题6・1解:余3BCD 码计数器计数规则为:0011->0100->—1100-0011-*-,由于釆用 异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1 所示。

题6.2试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2解:图题解6. 16.3试用D触发器和门电路设计一个同步4位格雷码计数器。

题6.3解:根据格雷码计数规则,\Q1Q OQsQ>\00011110000000011000111111100111\QlQoQ.3Q>\00011110000001011111111110100000X^iQoQ3Q>\00011110000111010001110111100001\QlQoQ.3Q>\00011110001100010011111100100011 Qi Qo计数器的状态方程和驱动方程为:er1=D.=+型Q”+Q;莎er1=D2=+Q©+N Q;N QT = D L+ Q;Q;Q;; +Qj = D o = Q^Q;1+按方程画出电路图即可,图略。

6.5试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题6・5解:可采取同步清零法实现。

电路如图题解6.5所示。

题6.6解:题6.4解:反馈值为1010c卜一进制计数器CLKCLR LD ENT ENP>c a[―<>40) a D DTC=\5图题解6. 5RCO74163当M=1时:六进制计数器八进制计数器6.7试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变 量M=0时,电路为8421 BCD 码十进制计数器,M=1时电路为5421 BCD 码十进制计数器, 5421BCD 码计数器状态图如下图P6.7所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章习题答案1.设计4个寄存器堆。

解:寄存器组2. 设计具有4个寄存器的队列。

解:输入数据输出数据3.设计具有4个寄存器的堆栈解:可用具有左移、右移的移位寄存器构成堆栈。

栈顶SR 1SR 2SR 3输入数据输出数据压入弹出4.SRAM 、DRAM 的区别解:DRAM 表示动态随机存取存储器,其基本存储单元是一个晶体管和一个电容器,是一种以电荷形式进行存储的半导体存储器,充满电荷的电容器代表逻辑“1”,“空”的电容器代表逻辑“0”。

数据存储在电容器中,电容存储的电荷一般是会慢慢泄漏的,因此内存需要不时地刷新。

电容需要电流进行充电,而电流充电的过程也是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的。

DRAM 拥有更高的密度,常常用于PC 中的主存储器。

SRAM 是静态的,存储单元由4个晶体管和两个电阻器构成,只要供电它就会保持一个值,没有刷新周期,因此SRAM 比DRAM 要快。

SRAM 常常用于高速缓冲存储器,因为它有更高的速率;5. 为什么DRAM 采用行选通和列选通解:DRAM 存储器读/写周期时,在行选通信号RAS 有效下输入行地址,在列选通信号CAS 有效下输入列地址。

如果是读周期,此位组内容被读出;如果是写周期,将总线上数据写入此位组。

由于DRAM 需要不断刷新,最常用的是“只有行地址有效”的方法,按照这种方法,刷新时,是在RAS 有效下输入刷新地址,存储体的列地址无效,一次选中存储体中的一行进行刷新。

每当一个行地址信号RAS 有效选中某一行时,该行的所有存储体单元进行刷新。

6. 用ROM 实现二进制码到余3码转换 解: 真值表如下:8421码余三码 B 3B 2BG 3G 2G1B 01G 00 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 010 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 10 0最小项表达式为:G 3=∑)9,8,7,6,5( G 2=∑)9,4,3,2,1( G 1=∑)8,7,4,3,0( G 0=∑)8,6,4,2,0( 阵列图为:G 3G 2G 1GB 3B 2B 1B B 07. 用ROM 实现8位二进制码到8421码转换解:输入为8位二进制数,输出为3位BCD 码,12位二进制数,所以,所需ROM 的容量为:28*12=30728.ROM、EPROM和EEPROM的区别解:ROM 指的是“只读存储器”,即Read-Only Memory。

这是一种线路最简单半导体电路,通过掩模工艺,一次性制造,其中的代码与数据将永久保存(除非坏掉),不能进行修改。

EPROM 指的是“可擦写可编程只读存储器”,即Erasable Programmable Read-Only Memory。

是采用浮栅技术生产的可编程存储器,它的存储单元多采用N沟道叠栅MOS管,信息的存储是通过MOS管浮栅上的电荷分布来决定的,编程过程就是一个电荷注入过程。

编程结束后,由于绝缘层的包围,注入到浮栅上的电荷无法泄漏,因此电荷分布维持不变,EPROM也就成为非易失性存储器件了。

当外部能源(如紫外线光源)加到EPROM上时,EPROM内部的电荷分布才会被破坏,此时聚集在MOS管浮栅上的电荷在紫外线照射下形成光电流被泄漏掉,使电路恢复到初始状态,从而擦除了所有写入的信息。

这样EPROM又可以写入新的信息。

EEPROM 指的是“电可擦除可编程只读存储器”,即Electrically Erasable Programmable Read-Only Memory。

也是采用浮栅技术生产的可编程ROM,但是构成其存储单元的是隧道MOS管,隧道MOS管也是利用浮栅是否存有电荷来存储二值数据的,不同的是隧道MOS管是用电擦除的,并且擦除的速度要快的多(一般为毫秒数量级)。

它的最大优点是可直接用电信号擦除,也可用电信号写入。

E2PROM的电擦除过程就是改写过程,它具有ROM的非易失性,又具备类似RAM的功能,可以随时改写(可重复擦写1万次以上)。

目前,大多数E2PROM芯片内部都备有升压电路。

因此,只需提供单电源供电,便可进行读、擦除/写操作,这为数字系统的设计和在线调试提供了极大方便。

9. flash存储器的特点解: Flash也是一种非易失性的内存,属于EEPROM的改进产品。

FLASH是结合EPROM和EEPROM技术达到的,FLASH使用雪崩热电子注入方式来编程。

主要特点是,FLASH对芯片提供大块或整块的擦除,而EEPROM则可以一次只擦除一个字节(Byte)。

这就降低了设计的复杂性,它可以不要EEPROM单元里多余的晶体管,所以可以做到高集成度,大容量,另FLASH的浮栅工艺上也不同,写入速度更快。

10. 用256K×8芯片实现256K×32的ROM解:需要4片256K×8的存储器,进行位扩展。

︰A0︰︰D0︰︰︰地址线数据线︰︰11. 用1M×4芯片实现1M×16的SRAM解:需要4片1M×4的存储器,进行位扩展。

12 用256K×4芯片实现1M×8的DRAM解:需8片1M×4的存储器,进行字位同时扩展。

13.用1M×8芯片实现4M×8的DRAM解:需4片1M ×8的存储器,进行字扩展。

A20A21A0︰︰A19D0︰︰︰D7地址线数据线A0 2×8A7 I/OA0 31M ×8A7 I/OA0 4256K ×8A7 I/OA0 11M ×8A7 I/O译码器1M 2:4CECECECE14.用64K ×4芯片实现64K ×16的ROM 解:需4片64K ×4的存储器,进行位扩展。

A0︰︰A15D0︰︰︰D15地址线数据线A0 CE 4I/OA0 CE 164K ×4A7 I/O︰︰︰︰︰︰15.用1M ×8芯片实现4M ×16的ROM解:需8片1M ×8的存储器,进行字位同时扩展。

第五章 习题答案1. 画出与阵列编程点 解:---2. 画出或阵列编程点 解:----X 1X 2X 3X 43. 与、或阵列均可编程,画出编程点。

解;1A -B B -F 324. 4变量LUT 编程 解:A 0A 1A 2A 3SOP 输出5. 用VHDL 写出4输入与门 解: 源代码:LIBRARY IEEE ;USE IEEE .STD_LOGIC_1164.ALL ;ENTITY and4 ISPORT (a ,b ,c ,d :IN STD_LOGIC ; x :OUT STD_LOGIC ); END and4;ARCHITECTURE and4_arc OF and4 IS BEGINx <=a AND b AND c AND d ; END and4_arc ;6. 用VHDL 写出4输入或门 解: 源代码:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY or4 ISPORT (a,b,c,d:IN STD_LOGIC;x:OUT STD_LOGIC);END or4;ARCHITECTURE or4_arc OF or4 ISBEGINx<=a OR b OR c OR d;END or4_arc;7.用VHDL写出SOP表达式解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sop ISPORT (a,b,c,d,e,f:IN STD_LOGIC;x:OUT STD_LOGIC);END sop;ARCHITECTURE sop_arc OF sop ISBEGINx<=(a AND b) OR (c AND d) OR (e AND f);END sop_arc;8.用VHDL写出布尔表达式解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY boolean ISPORT (a,b,c:IN STD_LOGIC;f:OUT STD_LOGIC);END boolean;ARCHITECTURE boolean_arc OF boolean ISBEGINf<=(a OR (NOT b)OR c) AND (a OR b OR(NOT c))AND ((NOT a) OR (NOT b) OR (NOT c));END boolean_arc;9.用VHDL结构法写出SOP表达式解:源代码:――三输入与非门的逻辑描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY nand3 ISPORT (a,b,c:IN STD_LOGIC;x:OUT STD_LOGIC);END nand3;ARCHITECTURE nand3_arc OF nand3 ISBEGINx<=NOT (a AND b AND c);END nand3_arc;――顶层结构描述文件LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sop ISPORT (in1,in2,in3,in4,in5,in6,in7,in8,in9:IN STD_LOGIC;out4:OUT STD_LOGIC);END sop;ARCHITECTURE sop_arc OF sop ISCOMPONENT nand3PORT (a,b,c:IN STD_LOGIC;x:OUT STD_LOGIC);END COMPONENT;SIGNAL out1,out2,out3:STD_LOGIC;BEGINu1:nand3 PORT MAP (in1,in2,in3,out1);u2:nand3 PORT MAP (in4,in5,in6,out2);u3:nand3 PORT MAP (in7,in8,in9,out3);u4:nand3 PORT MAP (out1,out2,out3,out4);END sop;10.用VHDL数据流法写出SOP表达式解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sop ISPORT (in1,in2,in3,in4,in5,in6,in7,in8,in9:IN STD_LOGIC;out4:OUT STD_LOGIC);END sop;ARCHITECTURE sop_arc OF sop ISBEGINout4<=(in1 AND in2 AND in3) OR (in4 AND in5 AND in6 ) OR (in7 AND in8 AND in9);END sop_arc;13.用VHDL设计3-8译码器解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder_3_to_8 ISPORT(a,b,c,g1,g2a,g2b:IN STD_LOGIC;y:OUT STD_LOGIC _VECTOR(7 downto 0));END decoder_3_to_8;ARCHITECTURE rt1 OF decoder_3_to_8 ISSIGNAL indata:STD_LOGIC _VECTOR(2 downto 0);BEGINindata<=c & b & a;PROCESS(indata,g1,g2a,g2b)BEGINIF(g1=′1′ AND g2a=′0′ AND g2b=′0′)THENCASE indata ISWHEN "000"=>y<="11111110";WHEN "001"=>y<="11111101";WHEN "010"=>y<="11111011";WHEN "011"=>y<="11110111";WHEN "100"=>y<="11101111";WHEN "101"=>y<="11011111";WHEN "110"=>y<="10111111";WHEN others=>y<="01111111";END CASE;ELSEy<="11111111";END IF;END PROCESS;END rt1;14.用VHDL设计七段显示译码器解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY segment7 ISPORT(xin:IN STD_LOGIC _VECTOR(3 downto 0);lt,rbi:IN STD_LOGIC;yout:OUT STD_LOGIC _VECTOR(6 downto 0);birbo:INOUT STD_LOGIC);END segment7;ARCHITECTURE seg7448 OF segment7 ISSIGNAL sig_xin:STD_LOGIC _VECTOR(3 downto 0);BEGINsig_xin<=xin;PROCESS(sig_xin,lt,rbi,birbo)BEGINIF(birbo=′0′)THENyout<="0000000";ELSIF (lt=′0′)THENyout<="1111111";birbo<=′1′;ELSIF (rbi=′0′AND sig_xin="0000")THENyout<="0000000";birbo<=′0′;ELSIF (rbi=′1′ AND sig_xin="0000")THENyout<="1111110";birbo<=′1′;ELSEbirbo<=′1′;CASE sig_xin ISWHEN "0001"=>yout<="0110000";WHEN "0010"=>yout<="1101101";WHEN "0011"=>yout<="1111001";WHEN "0100"=>yout<="0110011";WHEN "0101"=>yout<="1011011";WHEN "0110"=>yout<="0011111";WHEN "0111"=>yout<="1110000";WHEN "1000"=>yout<="1111111";WHEN "1001"=>yout<="1110011";WHEN others=>yout<="0100011";END CASE;END IF;END PROCESS;END seg7448;15.用VHDL设计8/3优先编码器解:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY priorityencoder ISPORT(din:IN STD_LOGIC _VECTOR(7 downto 0);ei:IN STD_LOGIC;yout:OUT STD_LOGIC _VECTOR(2 downto 0);eo,gs:OUT STD_LOGIC);END priorityencoder;ARCHITECTURE cod74148 OF priorityencoder IS BEGINPROCESS(ei,din)BEGINIF(ei=′1′)THENyout<="111";eo<=′1′;gs<=′1′;ELSEIF(din(7)=′0′ ) THENyout<="000";eo<=′1′;gs<=′0′;ELSIF(din(6)=′0′ ) THENyout <="001";eo<=′1′;gs<=′0′;ELSIF(din(5)=′0′ ) THENyout<="010";eo<=′1′;gs<=′0′;ELSIF(din(4)=′0′ ) THENyout<="011";eo<=′1′;gs<=′0′;ELSIF(din(3)=′0′ ) THENyout<="100";eo<=′1′;gs<=′0′;ELSIF(din(2)=′0′ ) THENyout<="101";eo<=′1′;gs<=′0′;ELSIF(din(1)=′0′ ) THENyout<="110";eo<=′1′;gs<=′0′;ELSIF(din(0)=′0′ ) THENyout<="111";eo<=′1′;gs<=′0′;ELSIF(din="11111111") THENyout<="111";eo<=′0′;gs<=′1′;END IF;END IF;END PROCESS;END cod74148;16.用VHDL设计BCD码至二进制码转换器。