QuartusⅡ设计举例

3-1.应用QuartusII完成基本组合电路设计

3-1. 应用QuartusII完成基本组合电路设计示例程序和实验指导课件位置:\EDA_BOOK3_FOR_1C6\chpt4\EXPT51_mux21A\工程mux21A(1) 实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

(2) 实验内容1:首先利用QuartusⅡ完成2选1多路选择器(例3-1)的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出图3-3所示的仿真波形。

最后在实验系统上进行硬件测试,验证本项设计的功能。

(3) 实验内容2:将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图3-1,并将此文件放在同一目录中。

以下是部分参考程序:...COMPONENT MUX21APORT ( a,b,s : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT ;...u1 : MUX21A PORT MAP(a=>a2,b=>a3,s=>s0,y=>tmp);u2 : MUX21A PORT MAP(a=>a1,b=>tmp,s=>s1,y=>outy);END ARCHITECTURE BHV ;【例3-1】ENTITY mux21a ISPORT ( a, b, s: IN BIT;y : OUT BIT );END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a,b,s)BEGINIF s = '0' THEN y <= a ; ELSE y <= b ;END IF;END PROCESS;END ARCHITECTURE one ;图3-1 双2选1多路选择器3-2 mux21a功能时序波形按照本章给出的步骤对上例分别进行编译、综合、仿真。

基于QuartusII的实例展示

基于QuartusII的实例演示基于QuartusII通过实验板上的KEY1按钮控制FPGA核心板上的第一个LED灯。

本实验比较简单,使用本站FPGA开发板或者CPLD开发板以及其它FPGA开发板都可进行实验。

下面实验目的:通过该实例学习,可以了解FPGA的基本开发流程,熟识quartusII软件基本功能的使用。

基本原理:利用一个常开按钮(实验板上的KEY1)作为输入(常开时输入1,闭合时输入0),经过一个反相器后输出到核心板的第一个LED。

KEY1常开时,LED亮,按下(闭合)实验板上的KEY1,该LED熄灭。

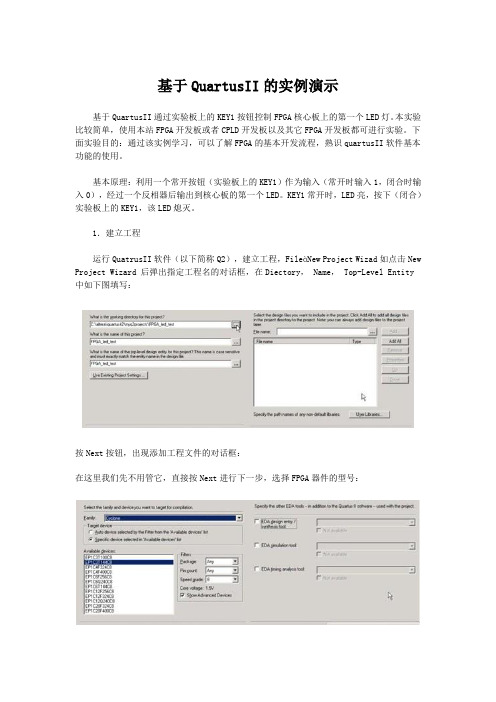

1.建立工程运行QuatrusII软件(以下简称Q2),建立工程,FileàNew Project Wizad如点击New Project Wizard 后弹出指定工程名的对话框,在Diectory, Name, Top-Level Entity中如下图填写:按Next按钮,出现添加工程文件的对话框:在这里我们先不用管它,直接按Next进行下一步,选择FPGA器件的型号:在Family下拉筐中,我们选择Cyclone系列FPGA,然后在“Available devices:”中根据核心板的FPGA型号选择FPGA型号,注意在Filters一栏选上“Show Advanced Devices”以显示所有的器件型号。

执行下一步出现对话框:这里是选择其它EDA工具的对话框,我们用Q2的集成环境进行开发,因此这里不作任何改动。

按Next进入工程的信息总概对话框:按Finish按钮即建立一个空项目。

2.建立顶层图执行FileàNew,弹出新建文件对话框:选择“Block Diagram Schematic File”按OK即建立一个空的顶层图,缺省名为“Block1.bdf”,我们把它另存为(FileàSave as),接受默认的文件名,并将“Add file to current project”选项选上,以使该文件添加到工程中去。

实验一 基于QUARTUSII图形输入电路的设计

实验一基于QUARTUSII图形输入电路的设计一、实验目的1、通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。

2、初步了解QUARTUSII原理图输入设计的全过程。

3、掌握组合逻辑电路的静态测试方法。

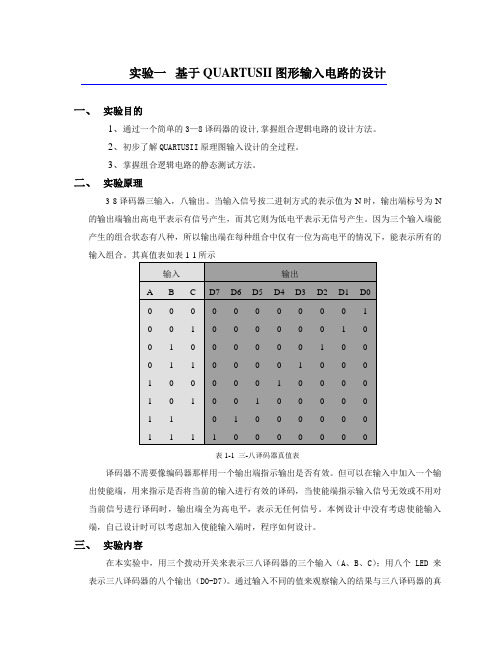

二、实验原理3-8译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时,输出端标号为N 的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。

其真值表如表1-1所示输入输出A B C D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 0 0 0 0 0 10 0 1 0 0 0 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 1 1 0 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 01 0 1 0 0 1 0 0 0 0 01 1 0 1 0 0 0 0 0 01 1 1 1 0 0 0 0 0 0 0表1-1 三-八译码器真值表译码器不需要像编码器那样用一个输出端指示输出是否有效。

但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。

本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。

三、实验内容在本实验中,用三个拨动开关来表示三八译码器的三个输入(A、B、C);用八个LED来表示三八译码器的八个输出(D0-D7)。

通过输入不同的值来观察输入的结果与三八译码器的真值表(表1-1)是否一致。

实验箱中的拨动开关与FPGA的接口电路如下图1-1所示,当开关闭合(拨动开关的档位在下方)时其输出为低电平,反之输出高电平。

其电路与FPGA的管脚连接如表1-2所示拨动开关的输出对应FPGA管脚名称图1-1 拨动开关与FPGA接口电路信号名称对应FPGA管脚名信号说明K1 AG12 从K1输出到FPGA的AG12K2 AA8 从K2输出到FPGA的AA8K3 AA10 从K3输出到FPGA的AA10K4 AB8 从K4输出到FPGA的AB8K5 AC5 从K5输出到FPGA的AC5K6 AE3 从K6输出到FPGA的AE3K7 AE4 从K7输出到FPGA的AE4K8 U8 从K8输出到FPGA的U5表1-2 拨动开关与FPGA管脚连接表LED灯与FPGA的接口电路如图1-2所示,当FPGA与其对应的端口为高电平时LED就会发光,反之LED灯灭。

QuartusⅡ设计举例

二、QuartusⅡ的图形用户界面启动QuartusⅡ软件后,点击File -> Open Project,调入一个项目,就进入图1-2所示图形用户界面图。

从图中我们可以看到整个界面可以分为八个区,分别是:图1-2 QuartusⅡ的图形用户界面1. 菜单区域:包括两部分,第一行是主菜单,第二行是常用快捷键。

2. 主工作区域:即输入编辑区。

3. 元件调用菜单:输入需要调用元件库里的器件,并选择连线以及文字标注等。

4. Project Navigator窗口:项目浏览器用于察看正在编辑的项目的信息。

5. Status窗口:系统在编译过程中的具体进度显示。

6. Change Manager窗口:用来跟踪和管理后编译,看是否达到设计目标。

7. Messages窗口:用于反馈在进行编译时的提示信息。

8. Tcl console窗口:工具命令语言(tool command language)输入窗口,Tcl是一种EDA 开放的工业标准脚本。

三、设计实例下面利用器件库中的存储器模块,采用原理图输入方式,来设计一个简单的LPM_ROM,并通过编辑器在ROM中存入新内容。

通过这个设计,我们将初步了解QuartusⅡ的设计的流程和步骤。

1.建立工程A. 建立文件夹如 D:\lpm_rom ,注意:文件夹(还有文件名)名称中不能包含中文和空格。

B. 新建一个存储器初始化(.mif)文件。

打开QuartusII,在顶部菜单中选File -> Newother files ->memory initialization file ,单击OK,在弹出的对话框中输入字数64和字长 8,单击OK, 打开存储器初始化编辑窗口。

利用View菜单命令,改变地址或字长的显示格式等,选择要编辑的字(反白显示),直接输入内容。

然后点File ->save as,在弹出的对话框中选择“保存在” D:\lpm_rom,输入文件名Mif1,文件名后缀选择.mif,取消最下面一行的Create new project based on this file 的选择框的对勾,点击保存完成。

QuartusⅡ课程设计报告

课程设计报告——2ASK信号的解调成员:张兴瑞01074029王鹏飞01074030柳东01074032设计内容:本课程设计内容主要介绍振幅键控(2ASK)的解调,即根据2ASK 解调原理,利用QuartusⅡ软件编程实现M序列(信号源)调制信号的解调,并对其进行仿真。

一、2ASK信号解调原理2ASK 是数字调制技术的基础,是一种实用的二进制振幅监控方式。

2ASK调制解调器系统框图如图1所示:图1 2ASK调制解调器系统2ASK主要有两种解调方式:非相干接收和相干接收。

其组成框图如图2所示。

2ASK非相干解调图2 2ASK相干解调图3 2ASK解调波形二、系统框图设计及各个模块功能下面给出2ASK解调器系统,其框图如4所示:图4.2-4 2ASK解调器① CLK:clk产生20MHZ信号。

② 125分频器:经分频得到与发射端相同的载波。

③ 2ASK调制:产生2ASK调制信号。

④比较器:将2ASK调制信号转化为方波信号。

由于调制信号是正弦波形式,这就需要将正弦波变为0、1表示的方波信号。

那么首先要将调制信号通过一个门限比较器及电平转换器,变成0、1表示的逻辑方波信号,然后在对其进行解调。

⑤ 4分频:将125分频后的信号再次分频,产生的信号作为计数器1的使能信号。

⑥计数器1:以恢复的方波作为计数时钟,对方波波个数计数。

⑦计数器2:将125分频器输出的信号作为计数器2的时钟信号,对这个信号计数。

⑧ ROM:内部存储32个1为数据,除一个数据为1外,其余数据全部为0。

这个ROM的输出作为计数器1的清零使能端。

⑨门限比较:以提取的时钟作为判决时钟,对计数器输出信号进行判决,输出基带信号demo_out。

下图为在QuartusⅡ软件中设计的2ASK解调系统的电路图:三、各个电路模块参数和程序1、ask模块:该模块为2ASK调制模块,产生解调用的2ASK调制信号,有同学提供。

2、fenpin125:对clk20MHz信号做125分频,产生160k的载波抽样信号。

QuartusII及其原理图设计

QuartusII及其原理图设 计

3

QUARTUS II 设计开发流程

QuartusII及其原理图设 计

4

QUARTUS II 文件格式介绍

QuartusII及其原理图设 计

5

QUARTUS II –图表和原理图编辑器

QuartusII及其原理图设 计

25

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

26

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

27

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

28

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

41

编译注意

要查找器件的资料,确保管脚定义,及其管脚工作状态 注意总线的画法和定义

注意同步清零和异步清零的方法

QuartusII及其原理图设 计

42

QUARTUS II –习题一

1-3 基于Quartus II软件,用部分积右移方式设计实现一个 4位二进制乘法器,选择合适的器件,画出电路连接

QuartusII及其原理图设 计

47

QUARTUS II –习题一

1-9 用D触发器构成按循环码(000-001-011-111-101100-000)规律工作的六进制同步计数器。 1-10 用74194、74273、D触发器等器件组成8位串入并 出的转换电路,要求在转换过程中数据不变,只有当8位一 组数据全部转换结束后,输出才变化一次。

实验1 应用QuartusII完成基本组合电路设计

实验1 应用QuartusII完成基本组合电路设计一、实验目的:熟悉QuartusⅡ的Verilog文本设计流程全过程,学习简单组合电路的设计、仿真和硬件测试。

二、实验内容1:首先利用QuartusⅡ完成2选1多路选择器(课本例3-3)的文本编辑输入(mux21a.v)和仿真测试等步骤,给出图1所示的仿真波形。

最后在实验系统上进行硬件测试,验证本项设计的功能。

图1 mux21a功能时序波形module mux21a(a,b,s,y);a,b,s;inputy;outputassign y=(s? a:b);endmodule2、将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图2(或书93页图3-29),并将此文件放在同一目录中。

图2 含2选1多路选择器的模块module muxk(a1,a2,a3,s0,s1,outy);a1,a2,a3;inputs0,s1;inputouty;outputtmp;wireu1(.a(a2),.b(a3),.s(s0),.y(tmp));mux21au2(.a(a1),.b(tmp),.s(s1),.y(outy));mux21aendmodule按步骤对上例分别进行编译、综合、仿真。

并对其仿真波形作出分析说明。

3、引脚锁定以及硬件下载测试:选择目标器件是EP1C6,建议选实验电路模式5(附录文件:GW48 EDA-SOPC 主系统使用说明中图7)。

用键1(PIO0,引脚号为1)控制s0;用键2(PIO1,引脚号为2)控制s1;a3、a2和a1分别接clock5(引脚号为16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。

通过短路帽选择clock0接256Hz信号,clock5接1024Hz,clock2接8Hz信号。

最后进行编译、下载和硬件测试实验(通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调)。

用Quartus II设计电子琴

(音阶发生器仿真图)

3.数控分频模块程序与仿真

--文件名:speaker.vhd。 --功 能:实现数控分频。 --最后修改日期:20004.3.19。 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity speaker is Port ( clk1 : in std_logic; tone1 : in integer range 0 to 2047; spks : out std_logic); end speaker; architecture Behavioral of speaker is signal preclk,fullspks:std_logic; begin

(顶层文件仿真图)

2.音阶发生器程序与仿真

--文件名:tone.vhd。 --功能:音阶发生器程序。 --最后修改日期:2004.4.13。 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity tone is Port ( index : in std_logic_vector(7 downto 0); code : out std_logic_vector(6 downto 0); high : out std_logic; tone0 : out integer range 0 to 2047); end tone; architecture Behavioral of tone is begin

4.1.2 利用Quartus II 工具分析设计[共3页]

第4章 时序约束与时序分析152另外,Altera 的STA 工具可以自动分析单时钟设计和多时钟设计(Multiple Clock Design )并报告器件内部的f max 和系统的f max 。

其实图4-2所示即为器件内部的f max (Internal f max ),它分析器件中同步元件(如寄存器)到同步元件之间的延时,然后计算出最高频率。

而系统f max (System f max )还包含了器件外部的延时分析,即包括器件与外部芯片配合的t SU 和t CO 的时序。

4.1.2 利用Quartus II 工具分析设计在Quartus II 的时序分析报告中,会以升序方式排列出路径的f max 。

在这些路径上,可以利用Quartus II 中的一些功能分析到更多的信息。

在所选中的时序路径上,单击鼠标右键,即可弹出一些查看路径细节的选项,如图4-4 所示。

• List Paths :列出路径信息。

• Locate in Assignment Editor :在Assignment Editor 中定位路径。

• Locate in Chip Editor :在Chip Editor 中定位路径。

• Locate in Timing Closure Floorplan :在时序收敛平面布局器中定位路径。

• Locate in Last Compilation Floorplan :在最近编译结果平面布局器中定位路径。

• Locate in Technology Map Viewer :在“工艺映射查看器”中定位路径。

图4-4 查看更多的路径信息需要提醒读者的是,虽然这里是以f max 时序报告为例说明,但是这些步骤在Quartus II 的所有其他时序路径中都类似。

如果选择List Paths 命令,就可以在Quartus II 的“消息窗口(Message Window )”的System 页面中看到图4-5所示的路径延时细节。

Quartus II 实例

图4-31 SignalTap II编辑窗

32

4.2 嵌入式逻辑分析仪

4.文件存盘 5.编译下载 6.启动SignalTap II进行采样与分析

图4-32下载cnt10.sof并准备启动SignalTap II

33

4.2 嵌入式逻辑分析仪

6.启动SignalTap II进行采样与分析

--LPM_ROM地址发生器进程

BEGIN

IF CLK'EVENT AND CLK = '1' THEN Q1<=Q1+1; --Q1作为地址发生器计数器

END IF;

END PROCESS;

u1 : data_rom PORT MAP(address=>Q1, q => DOUT,inclock=>CLK);--例化

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DOWNTO 0);

COMPONENT altsyncram --例化altsyncram元件,调用了LPM模块altsyncram

GENERIC (

--参数传递语句

intended_device_family

: STRING; --类属参量数据类型定义

52

END;

4.4 LPM_ROM宏模块应用

4.4.4 完成顶层设计

图4-47 仿真波形输出

53

4.4 LPM_ROM宏模块应用

4.4.4 完成顶层设计

图4-48 嵌入式逻辑分析仪获得的波形

19

4.1 QuartusII设计流程

5.时序仿真

图4-19 选择全时域显示

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二、QuartusⅡ的图形用户界面

启动QuartusⅡ软件后,点击File -> Open Project,调入一个项目,就进入图1-2所示图形用户界面图。

从图中我们可以看到整个界面可以分为八个区,分别是:

图1-2 QuartusⅡ的图形用户界面

1. 菜单区域:包括两部分,第一行是主菜单,第二行是常用快捷键。

2. 主工作区域:即输入编辑区。

3. 元件调用菜单:输入需要调用元件库里的器件,并选择连线以及文字标注等。

4. Project Navigator窗口:项目浏览器用于察看正在编辑的项目的信息。

5. Status窗口:系统在编译过程中的具体进度显示。

6. Change Manager窗口:用来跟踪和管理后编译,看是否达到设计目标。

7. Messages窗口:用于反馈在进行编译时的提示信息。

8. Tcl console窗口:工具命令语言(tool command language)输入窗口,Tcl是一种EDA 开放的工业标准脚本。

三、设计实例

下面利用器件库中的存储器模块,采用原理图输入方式,来设计一个简单的LPM_ROM,并通过编辑器在ROM中存入新内容。

通过这个设计,我们将初步了解QuartusⅡ的设计的流程和步骤。

1.建立工程

A. 建立文件夹如 D:\lpm_rom ,注意:文件夹(还有文件名)名称中不能包含中文和空

格。

B. 新建一个存储器初始化(.mif)文件。

打开QuartusII,在顶部菜单中选File -> New

other files ->memory initialization file ,单击OK,在弹出的对话框中输入

字数64和字长 8,单击OK, 打开存储器初始化编辑窗口。

利用View菜单命令,

改变地址或字长的显示格式等,选择要编辑的字(反白显示),直接输入内容。

然后点File ->save as,在弹出的对话框中选择“保存在” D:\lpm_rom,输入

文件名Mif1,文件名后缀选择.mif,取消最下面一行的Create new project based on this file 的选择框的对勾,点击保存完成。

C. 输入元件。

打开QuartusII,选File ->New Block Diagram/schematic File

单击 OK,进入图形输入界面,单击鼠标右键,点Insert ->Symobl…,在libraries 库中选择需要的元件,(如果知道元件名称也可以直接输入),在这里我们在Name框中直接输入lpm_rom,点OK,在弹出的窗口中选择VHDL ,在What name do you want for the output file? 点Browse,选择元件存放的文件夹D:\lpm_rom,给元件取名lpm_rom0,点击next ,进入LPM_ROM选择对话框,在currently select device family 中选择芯片cyclone,选宽8位,64字节,选中Dual clock , 点next进入下一界面, 去掉已打勾的’q’output port,然后点next进入下一界面, 点browse,选前面已建立的D: D:\lpm_rom\ Mif1.mif文件, 点next -> next, Finish完成lpm_rom0的输入。

重复点鼠标右键选Insert Symobl…在libraries库中择其他需要的input,output引脚。

连接到lpm_rom0对应的端口,修改输入引脚名称一个为a[5..0],时钟名为clk, 输出引脚的名称为q[7..0],然后点save,在弹出的窗口Do you want to create a new project on this file? 回答“是”,点next -> next ,在窗口中选择存入新建的文件夹D:\lpm_rom中,项目名lpm_rom0,lpm_rom0,点next->next,在设备窗口中分别选择:Family 为cyclone,package 为PQFP,Pin count

为240,Speed grade 为 8, 点next -> next ->Finish保存。

D. 编译。

在快捷键中,点击编译键►完成编译。

如果有错误,可返回前面重新检查、

修改输入后再次编译,直到看到提示编译成功信息。

2.波形仿真

A.打开QuartusII,选File File -> New other files -> Vector Waveform File,点击OK进入仿真界面。

B.在左空白处双击左键,在新出现的对话框的Radix中选择Hexadecimal(16进制), 点Node Finder 点list 选中需要仿真的信号,:a[5..0],clk ,[7..0]点击 OK -> OK.

C.加入信号。

选仿真需要的时间 ,点击Edit,选择End time (50 us).

点a[0],设置为高电平。

点clk (1us)注意一般设置信号的数量级和End time 数量级设置成一致的。

D.保存。

系统会自动把后缀加上。

E.仿真。

点快捷键仿真。

3.引脚锁定

仿真完成后,选择菜单Assignments-> p ins->Location,根据实验电路结构图NO.5和芯片引脚对照表, 查出a[5..0],clk ,[7..0] 在核心芯片EP1C6/1C12 Q240上所对应的引脚号,具体如下:

a[5]------键6-------PIO 5------238

a[4]------键5-------PIO 4------237

a[3]------键4-------PIO 3------236

a[2]------键3-------PIO 2------235

a[1]------键2-------PIO 1------234

a[0]------键1-------PIO 0------233

clk------ 28

q[7]-------PIO23-------20

q[6]-------PIO22-------19

q[5]-------PIO21-------18

q[4]-------PIO20-------17

q[3]-------PIO19-------16

q[2]-------PIO18-------15

q[1]-------PIO17-------14

q[0]-------PIO16-------13

q[3..0]是数码管1,q[7..4]是数码管2

引脚锁定后再次编译,点快捷键►编译。

4 下载

将电脑与实验箱通过并口连接接好,点快捷键,在出现的*.sof文件上,选

中program/configure点快捷键。

即可设计下载到FPGA中。

最后是用实验箱进行硬件测试。