二维FIR滤波器的FPGA实现

FIR数字高通滤波器的FPGA实现

摘要对于现代社会领域,数字信号处理(digital signal processing ,DSP)技术正在以很迅速的步伐往前发展,大家知道,数字信号处理中灵活性和实时性是最基本的要求,但在以往的模拟滤波器技术中,总是有着各种问题,让滤波效果达不到较为理想的要求。

而数字滤波器随着数字信号解决水平的发展而渐渐的被进步采用,并且因为它在设计上的灵活性等优势在滤波上被许多地方当做首选方式,已经渐渐地替代了以往的过滤器。

其中,有限长单位冲击响应(Finite Impulse Response,FIR)滤波器,因为它进行设计幅频时,具有良好的线性相位,以及稳定的系统等特性在数字信处理的项目里扮演了举足轻重角色。

这次使用现场可编程门阵列(Field-Programmable Gate Array,FPGA)和Matlab/DSP Builder来来设计一个FIR数字高通滤波器,使用窗函数法以及等波纹最佳优化法两种途径来对我们需要的滤波器进行设计。

首先确定好滤波器的相关参数和制作方案,利用DSP Builder制作工具设计一个取样频率48KHZ,截止频率10.8KHZ,输入输出数据宽度都是8位的17阶有限长单位冲击响应滤波器。

在MATLAB/Simulink中建立模型文件,调用工具库中的滤波器模块,连接成设计原理框图,设置好各参数并输入到对应的设计图位置后在Simulink中进行仿真,然后将模型文件通过Signal Compiler转化为VHDL语言和其他文件,在Quartus II中进行编译,引脚锁定下载到FPGA中,利用嵌入式逻辑分析仪SignalTap II对结果波形进行验证。

关键词:数字信号处理;现场可编程门阵列;有限长单位冲击响应;DSP BuilderAbstractIn the technical field of modern society, the digital signal processing technology has been developed rapidly. As we all know, the basic requirements of the digital signal processing are flexibility and topicality . However, the former filter technology always had many problems which made the filtering effect hard to achieve the ideal aims. With the development of digital signal processing technology, the digital filter has made great progress and been utilized. What’s more, it, as the preferred way has been used in many places because of its flexibility .So it has gradually displaced the previous filter. Among them, FIR digital filter plays a vital role because of it’s well linear phrase、stable systems and many other advantages in designing the frequency amplitudes.In this paper, I have designed a FIR digital high- pass filter by using FPGA and MATLAB/DSP Builder. With the window function method and equality ripple approach method, I first have analyzed and determined the relative parameters of the filter and design proposals. Then I made the 17-order FIR digital high-pass filter’s sampling frequency in 48KHZ、cutoff frequency in 10.8KHZ and data width in 8-bit by using DSP Bulider. By establishing model files in Matlab/Simulink, I used the filter module in the library tool and linked them into the principle chart .Later I set up and input those parameters into site to analogue simulation. I translated the Signal Compiler into the VHDL and other files and compiled in Quartus II and downloaded to FPGA. At last, I used the Signal Tap II to validate the result.KEY WORD: DSP; FPGA;FIR; DSP Builder第一章引言 (1)1.1背景意义 (1)1.2主要工作和组织结构 (3)第二章FIR数字滤波器 (4)2.1FIR数字滤波器的概念 (4)2.1.1FIR数字滤波器的结构 (5)2.1.2线性相位FIR数字滤波器的结构 (6)2.1.3FIR滤波器的特点 (7)2.2 FIR数字高通滤波器的设计方法 (9)2.2.1 窗函数法 (10)2.2.2等波纹最佳逼近法 (11)第三章FIR高通滤波器的FPGA实现 (13)3.1设计目标 (13)3.2 DSP Builder的设计流程 (13)3.3窗函数法 (15)3.4 FIR滤波器模型的建立 (17)3.4.1FIR高通滤波器原理图 (17)3.4.2 验证和测试方案 (19)3.5等波纹最佳逼近法 (20)3.6两种方法比较 (24)结束语 (25)参考文献 (26)第一章引言1.1背景意义对于当今信息领域,数字信号处理技术(Digital signal processing technology)已经变的相当迅速与成熟。

二维FIR滤波器的FPGA实现

二维FIR滤波器的FPGA实现

O 引言

二维有限长单位脉冲响应滤波器(2DFIR)用于对二维信号的处理,如在

通信领域中广泛采用2D-FIR 完成对I、Q 两支路基带信号的滤波[1]。

由于涉及大量复数运算并且实时性要求高,如果不对算法作优化在技术上很难实现。

目前主要设计方案是利用FPGA 厂商提供的一维FIR 知识产权核(IP),组成二维滤波器[2]。

这种方案没有考滤复数运算的特点,不可能在算法上优化,而且IP 核的内部代码是不可修改的,因此在不同厂商的器件上不可移植。

2D_FIR 的复数运算都需转成实数运算来实现的,而其中实数乘法运算占用逻辑资源远比实数加法多。

通过分析复数乘法特点,减小其所需实数乘法器个数就可以减小逻辑资源占用率并提高运算速度。

这种方案优点在于直接优化算法,不会受IP 核限制可移植性很强。

1 2DFlR 的设计

采用FPGA 设计复数FIR 滤波器常见的方案[2]为:用FPGA 厂商提供的4 个实数FIR 滤波器IP 核组合成2DFIR 滤波器。

很明显这种设计没有考虑复数运算的特点,2DFIR 滤波器占用资源至少4 倍于实数FIR 滤波器,硬件资源耗费过大,性能也会受到不小的影响。

因此从算法上分析并优化滤波器的结构非常必要。

1.1 算法优化

2DFIR 滤波器结构采用卷积型,它对输入数据的处理就是进行卷积运算[3],如(1)式所示:

(1)式中各量全为复数:xρ(n)为输入数据为滤波器抽头系数。

由(1)式。

基于FPGA的FIR滤波器设计与实现

目录引言................................... 错误!未定义书签。

第一章 FPGA的设计流程 ................... 错误!未定义书签。

1.1 FPGA概述 ................................... 错误!未定义书签。

1.2 FPGA设计流程................................. 错误!未定义书签。

1.3硬件描述语言HDL(Hardware Description Language) 错误!未定义书签。

1.4 FPGA开发工具Quartus Ⅱ软件设计流程 ......... 错误!未定义书签。

第二章有限冲激响应(FIR)滤波器的原理及设计.... 错误!未定义书签。

2.1数字信号处理基础原理.......................... 错误!未定义书签。

2.2 FIR滤波器背影知识........................... 错误!未定义书签。

2.3 FIR数字滤波器原理............................ 错误!未定义书签。

2.4 利用窗函数法设计FIR滤波器................... 错误!未定义书签。

第三章 FIR 数字滤波器的FPGA实现........... 错误!未定义书签。

3.1串行FIR滤波器原理............................ 错误!未定义书签。

3.2分布式算法基础................................ 错误!未定义书签。

3.3直接型FIR滤波器的原理结构图.................. 错误!未定义书签。

3.4具有转置结构的FIR滤波器...................... 错误!未定义书签。

第四章结论与总结......................... 错误!未定义书签。

毕业设计(论文)fir数字滤波器的fpga实现

毕业设计(论文)题目: FIR滤波器的FPGA实现专业:班级:姓名:学号:指导教师:日期: 2011-5-28目录第1章绪论 (1)1.1背景和选题依据 (1)1.2国内外研究现状和发展动态 (2)1.3论文研究的目的和主要内容 (2)第2章 FIR的原理及技术 (3)2.1FIR滤波器的特点 (3)2.2FIR滤波器的基础 (3)滤波器的基本结构 4滤波器的设计 5第3章EDA技术和可编程逻辑器件 (6)3.1电子设计自动化EDA技术 (6)编程逻辑器件简介 (8)进行开发的优点 (8)设计的开发流程93.3硬件描述语言VHDL及数字系统设计方法 (10)语言VHDL简介 (10)语言VHDL设计数字系统 (10)第4章基于FPGA的FIR滤波器硬件实现 (11)4.1器件介绍和系统开发环境 (11)Ⅱ系列结构和特点 (11)开发工具简介 (14)4.2并行FIR数字滤波器简介 (15)并行结构的改进 (15)块的划分 (16)4.3串行FIR数字滤波器的硬件实现 (17)设计思想与实现 (17)块具体功能的设计实现 (17)滤波器串行方式实现的系统分析 (23)滤波器的扩展应用 (24)结 (24)第5章总结与展望 (24)参考文献 (25)英文翻译 (26)FIR数字滤波器的FPGA实现【摘要】:随着科技的发展,电子电路的设计正逐渐摆脱传统的设计模式,而采用FPGA来设计电子电路正成为设计的趋势。

这是因为采用FPGA设计电子电路不仅开发时间短,资金投入相对少,且可将电路板级产品集成为芯片级产品。

纵观可编程逻辑器件的发展史,FPGA在结构原理、集成规模、下载方式、逻辑设计手段等方面的每一次进步都为现代电子设计技术的革命与发展提供了不可或缺的强大动力。

在数字处理中,滤波占有重要的地位。

数字滤波在语音和图像处理、HDTV、模式识别、谱分析等应用中经常用到。

有一限长冲激响应(FIR)滤波器,由于FIR系统只有一零点、系统稳定,便于实现FFT算法、运算速度快、线性相位的特性和设计更为灵活等突出优点而在工程实际中获得广泛应用。

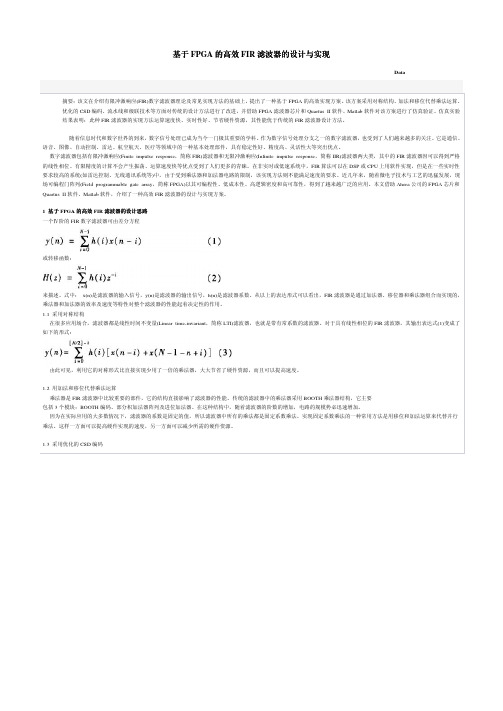

基于FPGA的高效FIR滤波器的设计与实现

基于FPGA的高效FIR滤波器的设计与实现Data摘要:该文在介绍有限冲激响应(FIR)数字滤波器理论及常见实现方法的基础上,提出了一种基于FPGA的高效实现方案。

该方案采用对称结构、加法和移位代替乘法运算、优化的CSD编码、流水线和级联技术等方面对传统的设计方法进行了改进,并借助FPGA滤波器芯片和Quartus II软件、Matlab软件对该方案进行了仿真验证。

仿真实验结果表明:此种FIR滤波器的实现方法运算速度快、实时性好、节省硬件资源,其性能优于传统的FIR滤波器设计方法。

随着信息时代和数字世界的到来,数字信号处理已成为当今一门极其重要的学科。

作为数字信号处理分支之一的数字滤波器,也受到了人们越来越多的关注。

它是通信、语音、图像、自动控制、雷达、航空航天、医疗等领域中的一种基本处理部件,具有稳定性好、精度高、灵活性大等突出优点。

数字滤波器包括有限冲激响应(Finite impulse response,简称FIR)滤波器和无限冲激响应(Infinite impulse response,简称IIR)滤波器两大类,其中的FIR滤波器因可以得到严格的线性相位、有限精度的计算不会产生振荡、运算速度快等优点受到了人们更多的青睐。

在非实时或低速系统中,FIR算法可以在DSP或CPU上用软件实现,但是在一些实时性要求较高的系统(如雷达控制、无线通讯系统等)中,由于受到乘法器和加法器电路的限制,该实现方法则不能满足速度的要求。

近几年来,随着微电子技术与工艺的迅猛发展,现场可编程门阵列(Field programmable gate array,简称FPGA)以其可编程性、低成本性、高逻辑密度和高可靠性,得到了越来越广泛的应用。

本文借助Ahera公司的FPGA芯片和Quartus II软件、Matlab软件,介绍了一种高效FIR滤波器的设计与实现方案。

1 基于FPGA的高效FIR滤波器的设计思路一个Ⅳ阶的FIR数字滤波器可由差分方程或转移函数:来描述。

FIR滤波器的FPGA设计与实现

FIR滤波器的FPGA设计与实现摘要滤波器,就是对电路网络中某一特定频率的频点或这个除了这个频点以外的频率进行有效滤除,从而得到一个特定频率的电信号,当然也可以用以消除某一个特定频率后的电信号的这样一种器件。

而所谓的FIR滤波器,其中FIR为Finite Impulse Response 的缩写,即指有限脉冲响应滤波器(以下简称为FIR滤波器)。

FIR滤波器由于本身可以设计成任意的幅频特性的滤波器,且同时能够保证精确、严格的相位线性,这就保证了它能够拥有一个稳定的系统。

因此,FIR滤波器已经成为数字系统与数字信号处理中,以及在通信系统等领域最重要的一种滤波器。

关键词:滤波器、有限脉冲响应、可编程门列阵。

SummaryFilter, the frequency of the circuit is a network of a specific frequency or frequency other than the frequency effectively filtered out to obtain a specific frequency of the power signal or a power signal to eliminate the specific frequency after . The so-called FIR filter, wherein the FIR Finite Impulse Response Abbreviation - finite impulse response filter (hereinafter simply referred to as an FIR filter). FIR filter can be designed arbitrarily because of theiramplitude-frequency characteristics of the filter, and simultaneously to ensure accurate and strict linear phase, which ensures that it has a stable system. Therefore, FIR filter has become a digital system with digital signal processing, as well as in the field of communication systems, etc. The most important kind of filter.Key words:Filter, Finite Impulse Response,Field-Programmable Gate Array引言线性时不变系统(Linear Time-Invariant System, L.T.I)是信号与系统处理以及信号系统处理中中最常见的系统。

基于FPGA的FIR数字滤波器设计与实现

基于FPGA的FIR数字滤波器设计与实现佚名【摘要】简要介绍了FIR数字滤波器的结构特点和基本原理,提出基于FPGA和DSP Builder的FIR数字滤波器的基本设计流程和实现方案。

在Matlab/Simulink 环境下,采用DSP Builder模块搭建FIR模型,根据FDATool工具对FIR滤波器进行了设计,然后进行系统级仿真和ModelSim功能仿真,其仿真结果表明其数字滤波器的滤波效果良好。

通过SignalCompiler把模型转换成VHDL语言加入到FPGA的硬件设计中,从QuartusⅡ软件中的虚拟逻辑分析工具SignalTapⅡ中得到数字滤波器实时的结果波形图,结果符合预期。

%The structure feature and the basic principle of FIR digital filter is introduced briefly. The basic design process and implementation scheme of the FIR digital filter based on FPGA and DSP Builder is proposed in this paper. FIR model is structured with DSP Builder module in the Matlab/Simulink environment. The FIR digital filter is designed according to the FDA⁃Tool. The system level simulation and ModelSim function simulation were completed. The simulation results show that the filter has excellent effect. The model is converted to VHDL language through SingalCompiler and added to FPGA hardware design. The real⁃time waveform graph of the FIR digital filter was received by the virtual logic analysis tool SignalTapⅡ in QuartusⅡ. The results conform to the expected requirement.【期刊名称】《现代电子技术》【年(卷),期】2013(000)014【总页数】4页(P123-126)【关键词】FPGA;DSP Builder;FIR数字滤波器;ModelSim功能仿真【正文语种】中文【中图分类】TN911-34在信息信号处理过程中,数字滤波器是信号处理中使用最广泛的一种方法。

FIR滤波器的FPGA设计与实现

第25卷第—期电子计工程2017^ 4月Vol.25 No.24 Electronic Design Engineering Dec. 2017FPAA%针'(规陈援援,刘有耀(西安邮电大学电子工程学院,陕西西安710061)摘要:本文针对快速、准确选择参数符合项目要求的滤波器设计方法的目的,通过系统的介绍有限脉冲响应(Finite Impulse Response,FIR)滤波器的原理、结构形式以及几种FIR滤波器设计方法,结合MATLAB软件提供的专用数字滤波器设计工具包FDAT00L,以及Quart?J软件提供的FIR核实现快速、便捷的设计F IR滤波器的几个具体实验,得出结论证实了熟练使用FDAT00L工具和FIR核比直接编写代码设计F IR滤波器更加方便、快捷,但编写代码具有灵活性更强的优势。

关键词+有限冲击响应2MATLAB;数字滤波器;FIR核中图分类号:TN713+.7 文献标识码:A文章编号+1674-6236(2017)24-0065-05FIR filter of the FPGA design and implementationCHEN Yuan-yuan,LIU You-yao(&'an University of P osts&Telecommunications,Xi'an710061 ,China)Abstract: I n o rder to choice the method of filter design which the parameters conform to the projectrapidly and accurately,this paper systematically introduce the principle,structure and several kinds ofdesign method of the Finite I mpulse Response(Finite I mpulse Response,F I R)filter,combined with MATLAB software which provide dedicated digital filter design tool called FDAT00L,and Quartus IIsoftware which provide F I R core realize design F I R filter rapidly and conveniently combine with severa specific experiments,the conclusion prove that skilled use FDAT00L tool and F I R core than write codesdirectly to design F I R filter are more convenient and quick,however writing codes have the advantage ofmore flexibility.Key words:finite impulse response;MATLAB;digital filter;F I R coreFIR(Finite Impulse Response)数字滤波器是非 递归型滤波器的简称,又叫有限长单位冲激响应滤 波器,是数字信号处理中较基本的单元,其稳定性 好、精度高、可以实现线性相位,在信号的滤波、检测 及预测等信息处理过程中都C要广泛应用到FIR数 字滤波器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二维FIR滤波器的FPGA实现

作者:阳小明, 李天倩, Yang Xiaoming, Li Tianqian

作者单位:西华大学,电气信息学院

刊名:

电子技术

英文刊名:ELECTRONIC TECHNOLOGY

年,卷(期):2009(4)

1.王金明;杨吉斌数字系统设计与Verilog HDL

2.程佩青数字信号处理教程

3.吴广玉;闫波;李广军基于FPGA的基带正交盲均衡器的设计 2003

4.阳小明;邱琪复自适应均衡器的研究及实现[期刊论文]-电子科技大学学报 2001(04)

1.朱双鹤.尚庆宣一种基于估计熵的自适应模糊滤波器及其在箭遥信号处理中的仿真应用[期刊论文]-国防科技大学学报2002,24(3)

2.Jie ZHOU.Yazhuo DONG.Yong DOU.Yuanwu LEI Dynamic Configurable Floating-Point FFT Pipelines and Hybrid-Mode CORDIC on FPGA[会议论文]-2008

3.郑鹤.王鲁平.李飙.ZHENG He.WANG Lu-ping.LI Biao一种快速的二维中值滤波算法及其硬件实现[期刊论文]-信息与电子工程2005,3(4)

4.卫建华.贺新华.WEI Jian-hua.HE Xin-hua基于HQV Vida处理器的HDTV图像质量改善[期刊论文]-现代电子技术2010,33(9)

5.罗海波.史泽林.惠颖.周广超.LUO Hai-bo.SHI Ze-lin.HUI Ying.ZHOU Guang-chao基于多级分组排序网络的实时大窗口二维中值滤波器设计[期刊论文]-红外与激光工程2008,37(5)

6.轶名视频压缩技术和MPEG降噪技术解析[期刊论文]-金卡工程2006,10(6)

本文链接:/Periodical_dzjs200904014.aspx。