基于FPGA的FIR滤波器设计与实现

基于FPGA的FIR滤波器设计与实现

目录引言................................... 错误!未定义书签。

第一章 FPGA的设计流程 ................... 错误!未定义书签。

1.1 FPGA概述 ................................... 错误!未定义书签。

1.2 FPGA设计流程................................. 错误!未定义书签。

1.3硬件描述语言HDL(Hardware Description Language) 错误!未定义书签。

1.4 FPGA开发工具Quartus Ⅱ软件设计流程 ......... 错误!未定义书签。

第二章有限冲激响应(FIR)滤波器的原理及设计.... 错误!未定义书签。

2.1数字信号处理基础原理.......................... 错误!未定义书签。

2.2 FIR滤波器背影知识........................... 错误!未定义书签。

2.3 FIR数字滤波器原理............................ 错误!未定义书签。

2.4 利用窗函数法设计FIR滤波器................... 错误!未定义书签。

第三章 FIR 数字滤波器的FPGA实现........... 错误!未定义书签。

3.1串行FIR滤波器原理............................ 错误!未定义书签。

3.2分布式算法基础................................ 错误!未定义书签。

3.3直接型FIR滤波器的原理结构图.................. 错误!未定义书签。

3.4具有转置结构的FIR滤波器...................... 错误!未定义书签。

第四章结论与总结......................... 错误!未定义书签。

基于FPGA的FIR滤波器设计

FIR滤波器设计1项目背景1.1FIR和IIR滤波器FIR(Finite Impulse Response)Filter:有限冲激响应滤波器,又称为非递归线性滤波器。

FIR滤波器,顾名思义,其脉冲响应由有限个采样值构成。

长度(抽头数)为N、阶数为N−1的FIR系统的转移函数、差分方程和单位冲激响应分别如下列三式所示。

图510IIR(Infinite Impulse Response)Filter:无限冲激响应滤波器,又称为递归线性滤波器。

FIR相对与IIR来说,具有如下的优点:可以具备线性相位特性线性相位的概念:如果滤波器的N个实值系数为对称或者反对称结构,该滤波器具有线性相位。

W(n)=±W(N−1−n)W(n)=±W(N−1−n)线性相位的特性:通过线性相位滤波器的信号的所有频率部分具有相同的延迟量。

易于设计但FIR也有自身的缺点:同样指标的滤波器,FIR需要更多的参数,即实现时消耗更多的计算单元,产生更大的延迟。

1.2FIR滤波器的原理信号通过一个FIR滤波器其实就是信号与FIR滤波器的系数进行卷积(即乘累加)的过程。

我们以一个简单信号模型为例,了解一下FIR波形器的原理。

现在有三组信号,分别是:信号1:低频信号,即在时域上变化慢的信号,其输入先后为11112222。

信号2:直流信号,其输入先后为1111111。

信号3:高频信号,即在时域上变化快的信号,其输入先后为12121212。

简单的滤波器模型低通滤波器:11信号1与低通滤波器进行卷积运算,其结果再除以2,得到如下数据:111 1.5222。

可以看到,低频信号经过低通滤波器后,各个点仍然保持了其形状,而且在1变成2时,还变平缓了。

信号2与低通滤波器进行卷积运算,其结果再除以2,得到如下数据:1111111。

可以看到,直流信号与输入的信号完成相同。

信号3与低通滤波器进行卷积运算,其结果再除以2,得到如下数据:1.5 1.5 1.5 1.5 1.5 1.51.5。

基于FPGA的高效FIR滤波器设计与实现

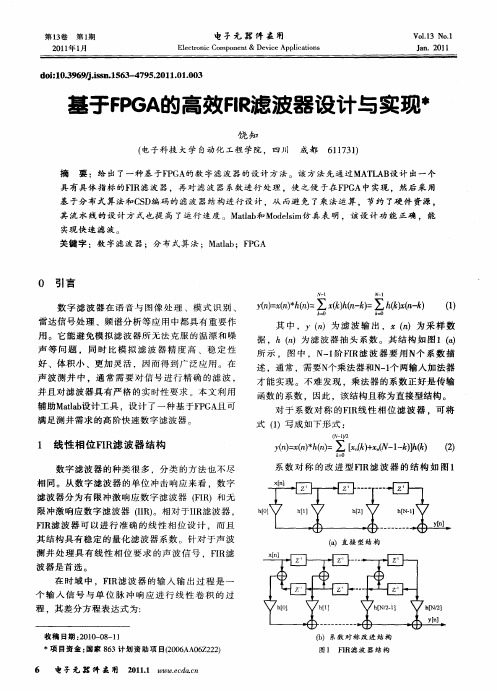

( a )直 接 型 结 构

程 ,其 差分方 程表 达式 为:

收 稿 日期 :0 0 0 — 1 2 1 — 8 1

()系数 对 称 改进 结构 b

图 1 FR滤 渡 器 结 构 I

项 目资 金 : 国家 8 3计 划 资助 项 目(0 6 A 6 22 6 20 A 0 Z 2 )

F A o l Ma a 信 号 处 理 工 具 箱 里 专 用 的 D T o是 tb l 滤 波器 设计 分 析工 具 ,该 工具 的 主要 作 用是 按 照 设 计 指 标 提 取 滤 波器 系数 。用F A 0l 计 数 字 D T o设 滤 波器 的关 键 在 于滤波 器 类 型 、窗 函数 、滤 波 器 阶 数 、截止 频 率等参 数 的选 择 。其 中窗 函数 用 于

占用 大量 资 源 的乘 法单 元 。分 布 式 算法 ( A D )的 提 出可 将乘 法 运算 转换 为 移位 相加 运 算 ,从 而节

滤波 器分 为有 限冲激 响应 数字 滤波 器 fI 1和 无 FR

y =( (=2 [(+ V1. } ( ( ) n 2 一一)( 2 n ) ) i J } ) 】 )

k - - 0

系 数 对 称 的 改 进 型 FR滤 波 器 的结 构 如 图 1 I

限 冲激 响应数 字滤 波器 fR 。相对 于I I ) I I R滤波器 ,

具有 具体指 标 的FR滤 波器 ,再对 滤波 器 系数进 行 处理 ,使之 便 于在 F G I P A中实现 。然后 采 用 基 于分布式算 法和C D编码 的滤波 器结构进 行设 计 ,从 而避免 了乘 法运算 ,节约 了硬件 资源 。 S

其 流 水 线 的 设 计 方 式 也 提 高 了运 行 速 度 。 Ma a 和 Moes tb l d l m仿 真 表 明 ,该 设 计 功 能 正 确 , 能 i

基于FPGA的FIR滤波器设计书

基于FPGA的FIR滤波器设计书1 概述我们学生通过这次的课设深入理解和消化了基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《FPGA 系统设计与应用》几门课程融合在一起综合应用设计一个实用的数字FIR 滤波器。

本报告中首先讲解了这次设计的具体内容,以及所要求的数字 FIR 滤波器的技术指标。

然后,数字滤波器的一些设计方法,并具体确定我这次设计所用的设计方案。

滤波器在matlab 中的设计方法应用。

通过matlab 得到所需滤波器的具体参数h(n),然后用这些所设计的参数,通过Quartus ii 工具编程具体实现滤波器功能。

这次滤波器实现过程中,用到以下小模块:延时器,加法器,乘法器,减法器。

2 课程设计要求及注意事项1.设计过程以小组为单位,各组设一个组长,负责组织和协调本小组的讨论、任务分工等;2.设计过程必须在本组内独立完成,不得跨组参考或抄袭,避免方案出现雷同;3.设计书一律采用专用报告纸,用统一封面装订;4.课程设计原则上在3 周内做完;5.最后一周周五进行优秀设计方案评选,在各组推选代表进行方案介绍的基础上,推选出2-3 个优秀设计方案。

6.学有余力的学生在完成必做设计内容的基础上,可对内容进一步展开设计,以提高综合应用能力,锻炼独立解决问题的能力。

3 课程设计内容3.1 课程设计题目及要求3.1.1 设计题目:基于 FPGA 的 FIR 滤波器设计3.1.2 设计要求利用所学知识,采用MATLAB 和FPGA 相结合完成FIR 滤波器的设计仿真。

采用直接法或分布式算法实现FIR 数字滤波器,了解两种算法的优缺点,选择其中一种算法,得出用它来实现FIR 滤波器的硬件结构,对其实现方式进行研究,分别采用合适的方法来设计,最后利用FPGA 器件实现FIR 数字滤波器的硬件电路,并用Matlab 对实现的结果进行仿真分析。

设计指标:1)类型:FIR 低通2)系统采样频率:Fs=10KHz;3)输入序列位宽为8 位的有符号数(最高位为符号位);4)输出结果保留8 位5)窗口类型为 kaiser 窗,β=0.5; 6)滤波器长度为N=16;3.2 数字滤波器简介及结构3.2.1 简介 滤波器是用来进行频率选择或频率分辨操作的线性时不变系统的通称。

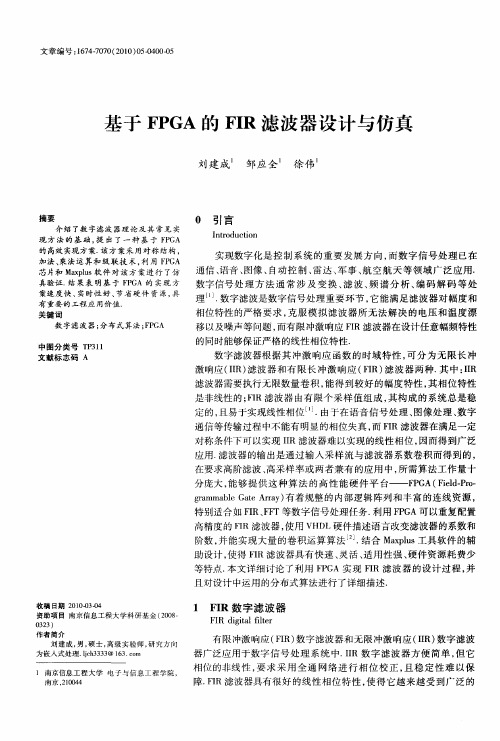

基于FPGA的FIR滤波器设计与仿真

数字滤波器; 分布 式 算 法 ;P A FG 中图分 类 号 T 3 1 P 1 文 献标 志 码 A

滤波器需 要执行 无 限数量 卷 积 , 能得 到较 好 的 幅度特性 , 相位 特性 其 是非线性 的 ; I 波器 由有 限个 采样 值 组 成 , 构 成 的系 统总 是稳 FR滤 其 定 的 , 易于实现 线性相 位 …. 且 由于 在语音 信 号处 理 、 图像 处理 、 数字 通信等传 输过程 中不能有 明显 的相位失真 , FR滤波器在 满足一定 而 I 对称条件 下可 以实现 I I R滤波器 难 以实 现 的线 性相 位 , 因而得 到广泛

特 别适合如 FR、丌 等数 字信号处 理任务 . I F 利用 F G P A可 以重 复配置 高精 度的 FR滤波器 , 用 V D I 使 H L硬件 描述语 言改变滤 波器 的系数和

阶数 , 能实 现大 量 的卷 积运 算算 法 J 结合 M xls 具软 件 的辅 并 . apu 工

案速 度 快 、 时性 好 、 省 硬 件 资 源 , 实 节 具 有重 要 的 工程 应 用价 值 . 关 键 词

实 现数字化 是 控 制 系统 的重 要发 展 方 向 , 而数 字 信 号处 理 已在

通信 、 语音 、 图像 、 自动控 制 、 达 、 事 、 空 航 天等 领 域 广 泛应 用 . 雷 军 航 数 字信号 处 理 方 法 通 常 涉 及 变 换 、 波 、 谱 分 析 、 码 解 码 等 处 滤 频 编 理¨. 数字滤 波是数 字信号处 理重 要 环节 , 它能 满 足滤 波器 对幅度 和 相 位特性 的严格 要 求 , 克服 模 拟 滤 波器 所 无 法解 决 的 电压 和 温度 漂 移 以及噪声 等 问题 , 而有 限冲激 响应 FR滤 波器在设计 任意 幅频 特性 I 的同时能够保证 严格 的线性相 位特性 . 数 字滤波器 根 据其 冲激 响应 函数 的 时域 特性 , 分 为无 限 长 冲 可

基于FPGA的FIR滤波器设计

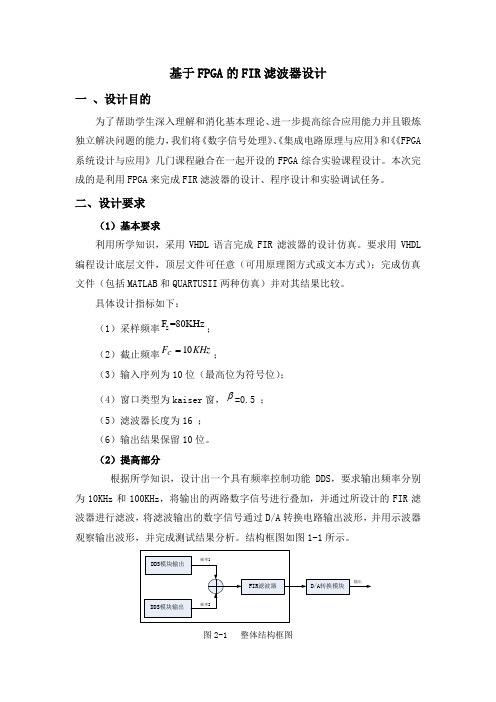

基于FPGA 的FIR 滤波器设计一 、设计目的为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《《FPGA 系统设计与应用》几门课程融合在一起开设的FPGA 综合实验课程设计。

本次完成的是利用FPGA 来完成FIR 滤波器的设计、程序设计和实验调试任务。

二、设计要求(1)基本要求利用所学知识,采用VHDL 语言完成FIR 滤波器的设计仿真。

要求用VHDL 编程设计底层文件,顶层文件可任意(可用原理图方式或文本方式);完成仿真文件(包括MATLAB 和QUARTUSII 两种仿真)并对其结果比较。

具体设计指标如下: (1)采样频率S F =80KHz ; (2)截止频率KHz F C 10=;(3)输入序列为10位(最高位为符号位); (4)窗口类型为kaiser 窗,β=0.5 ; (5)滤波器长度为16 ; (6)输出结果保留10位。

(2)提高部分根据所学知识,设计出一个具有频率控制功能DDS ,要求输出频率分别为10KHz 和100KHz ,将输出的两路数字信号进行叠加,并通过所设计的FIR 滤波器进行滤波,将滤波输出的数字信号通过D/A 转换电路输出波形,并用示波器观察输出波形,并完成测试结果分析。

结构框图如图1-1所示。

图2-1 整体结构框图三、设计原理3.1 FIR 滤波器由线性系统理论可知,在某种适度条件下,输入到线性系统的一个冲击完全可以表征系统。

当我们处理有限的离散数据时,线形系统的响应(包括对冲击的响应)也是有限的。

若线性系统仅是一个空间滤波器,则通过简单地观察它对冲击的响应,我们就可以完全确定该滤波器。

通过这种方式确定的滤波器称为有限冲击响应(FIR)滤波器。

3.2 线性FIR 滤波器原理FIR 滤波器响应(简称FIR )系统的单位脉冲响应()h n 为有限长序列,系统函数()H z 在有限z 平面上不存在极点,其运算结构中不存在反馈支路,即没有环路。

基于FPGA的FIR滤波器的设计与实现

基于FPGA 的FIR 滤波器的设计与实现马才根(东南大学 江苏南京 210018)摘 要:提出了一种基于FP GA 的FIR 滤波器设计方案。

介绍了基于F PGA 的F IR 滤波器的数字信号处理的算法设计,采用直接型的基本结构来设计,通过1位乘以8位的乘法,然后再移位相加的方法即可得到结果,其运算效率明显提高,并结合先进的EDA 软件进行高效的设计和实现,并给出了用Max+Plus Ⅱ运行的仿真结果。

该设计对FP GA 硬件资源的利用高效合理,用VHDL 编程,在F PGA 中实现了高采样率的F IR 滤波器。

关键词:F IR 滤波器;F PGA ;VHDL ;电子设计自动化中图分类号:TN713+.7 文献标识码:B 文章编号:1004373X (2005)2207302Design of FIR Filt er Based on FPGAMA Caigen(Southeast U niversity,N anjing,210018,China )Abstra ct :T his paper intr oduces the design scheme of F IR filter based on FP GA ,intr oduces that the design t echnology of F IR filter based on F PGA about digital syst em processing a rit hmetic .F IR filter adopts the basic structure of dir ect type ,the result s ar e got by the multiplication of 1×8,then shifting and adding.Integr ating advanced sof twar e of EDA to design and achieve,and giving some emulat or r esults.T his design ma kes high use of har dwar e r esource about F PGA,pr ogram ming with VHDL language,achieving F IR filter with high sampling level based on F PGA .Ke ywords :FIR filter ;FP GA ;VHDL ;EDA收稿日期:20050809 FIR 滤波器有多种设计和实现方法。

基于FPGA的FIR数字滤波器设计与仿真

a in ls p rto , so ai n o h p n . I l r i w d l s d b c u e o t t c h s itrin a d s a p c t o s s a e a ain r t r t rs a ig F R f t s i ey u e e a s fi s i tp a e d s t o n h r u — f g e o i e s r o

c a a trsi. h a i h o yo i i lf tra d t e meh d o a iai n a e r s a c e . h e i n o e rq i d d gt l h r c e i cT eb sc t e r fd gt le n h t o f e l t r e e r h dT e d sg ft e u r ii t a i r z o h e a i e sgv n u ig t e smu ae s f r fMAT AB.n h i l t r s l i ie . f tri ie sn h i lt o t a e o l w L a d t e smua e e u t sgv n Ke r sf t r d gt l c nr ls se / cl y i sal t n r v e d sr u e l oi m ; n o f n t n y wo d :i e ; ii ; o to y t msf i t n tl i e iw; it b t d ag rt l a a i ao i h wi d w c i u o

y∑c]2 + b2f = 【l ∑X ] n一 [ n

n = 0 L = 0 J

( 3 )

分 布 式 算 法 是 一 种 以 实 现 乘 加 运 算 为 目的 的运 算 方 法 。 它 与传 统 算 法 实 现 乘 加 运 算 的 不 同 在 于执 行 部 分 积 运 算 的先 后顺序。 该算 法 利 用一 个 查 找 表 (U ) 现 映射 , 用 一 个 2 L T实 即 字 宽 、 先 编 好 程 序 的 L T接 收 一个 Ⅳ 位 输 入 向 量 X= 】 预 U I 【 , x0 %[ , , [- l 映 射 , 查 找 表 的 查 找后 直接 输 出 部 分 积 。 1 … x N l】 】  ̄ 的 经 与传 统 算 法 相 比 , 布式 算 法 可 极 大 的 减 少 硬 件 电路 的规 模 , 分

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录引言 (4)第一章FPGA的设计流程 (5)1.1 FPGA概述 (5)1.2 FPGA设计流程 (9)1.3硬件描述语言HDL(Hardware Description Language) (10)1.4 FPGA开发工具Quartus Ⅱ软件设计流程 (13)第二章有限冲激响应(FIR)滤波器的原理及设计 (16)2.1数字信号处理基础原理 (16)2.2 FIR滤波器背影知识 (19)2.3 FIR数字滤波器原理 (21)2.4 利用窗函数法设计FIR滤波器 (26)第三章FIR 数字滤波器的FPGA实现 (31)3.1串行FIR滤波器原理 (31)3.2分布式算法基础 (32)3.3直接型FIR滤波器的原理结构图 (34)3.4具有转置结构的FIR滤波器 (36)第四章结论与总结 (40)谢辞 (42)参考文献 (43)摘要:本论文课题是《基于FPGA的FIR滤波器设计与实现》。

数字滤波器是语音与图象处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足滤波器对幅度和线性相位的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。

有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。

因此在许多应用领域都显示了强大的生命力,具有重要应用意义。

本文介绍了用VHDL实现线性相位FIR(有限长单位冲激响应)滤波器。

提出了一种基于FPGA的FIR滤波器设计方案。

介绍了基于FPGA的FIR滤波器的数字信号处理的算法设计,采用直接型和转置型的基本结构来设计,其运算效率明显提高,并结合先进的EDA软件进行高效的设计和实现,并给出了用Quartus Ⅱ运行的仿真结果。

该设计对FPGA硬件资源的利用高效合理,用VHDL编程,在PFGA中实现了高采样率的FIR滤波器。

关键字:FIR滤波器;FPGA;VHDL;MATLAB;Quartus ⅡAbstract:Digital filter is a fundamental device used in pronunciation &pattern process, pattern-recognition, radar signal processand spectral analysis. It can meet the high needs to range andphase, and can avoid such problems as voltage drifting,temperature drifting and noise that analogue filters cannotovercome. FIR filter can assure a strict linear phase identitywhile designing any range and frequency. Therefore, FIR filterhas shown its strong vitality in many fields and its importancein using. In the paper, the way to use VHDL to design linearphase FIR filter is introduced and its importance in using. Inthe paper, the way to use VHDL to design linear phase FIRfilter is introduced and its designing thoughts are expounded.This paper introduces the design scheme of FIR filter based onFPGA, introduces that the design technology of FIR filterbased on FPGA about digital system processing arithmetic.FIR filter adopts the basic structure of direct type, the resultare shifting and adding. Integrating advanced software of EDAto design and achieve, and giving some emulator results. Thisdesign makes high use of hardware resource about FPGA,programming with VHDL language, achieving FIR filter withhigh sampling level based on PDGA.Keywords: Finite Impulse Response Digital Filter(FIR)、FieldProgrammable Gate、Array(FPGA)、VHDL、Quartus Ⅱ引言在数字信号处理技术不断发展的今天,数字滤波器正在迅速地代替传统的模拟滤波器,所以有越来越多的人们在研究数字滤波器的结构以及其实现。

在数字滤波器中,有限冲激响应(FIR)滤波器具有无限冲激响应(IIR)滤波器所没有的线性相位,所以本课题研究的就是FIR数字滤波器,主要讨论了它的结构以及实现的方法。

目前FIR滤波器的实现方法有3种:利用单片通用数字滤波器集成电路、DSP 器件和可编程逻辑器件实现。

单片通用数字滤波器使用方便,但由于字长和阶数的规格较少,不能完全满足实际需要;使用DSP器件实现虽然简单,但由于程序顺序执行,执行速度较慢。

FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好。

本人毕业设计就是基于FPGA运用VHDL设计实现FIR 滤波器。

众所周知,Quartus Ⅱ是美国ALTERA公司自行开发的一种针对其公司生产的系列FPGA的设计、仿真、编程的工具软件,Quartus Ⅱ是FPGA应用软件中比较典型和常见的一种工具,在我国应用较为普遍。

本设计就是用Quartus Ⅱ所支持的一种很常用的硬件描述语言(VHDL)来编程,并在Quartus Ⅱ上编译与仿真。

1 FPGA的设计流程可编程逻辑器件(PLD, Programmable Logic Device)是厂家作为一种通用型器件生产的半定制电路,用户可以通过对器件编程实现使之实现所需要的逻辑功能.它的应用和发展不仅简化了电路设计,降低了成本,提高了系统的可靠性,而且给数字系统的设计方式带来了革命性的变化。

1.1 FPGA概述1 简单PLD的基本结构简单PLD包括PROM, PLA, PAL和GAL。

其结构特点是由与阵列和或阵列组成,能有效地实现“积之和”形式的布尔逻辑函数。

简单PLD的基本结构图如图2.1所示。

图中与阵列和或阵列是电路的主体,主要用来实现组合逻辑函数。

输入由缓冲器组成,它使输入信号具有足够的驱动能力并产生互补输入信号。

输出电路可以提供不同的输出方式。

图1.1简单PLD的基本结构2 现场可编程门阵列FPGA是现场可编程门阵列(Field Programmable Gate Array)的简称,是20世纪80年代中期出现的高密度可编程逻辑器件。

FPGA的出现是超大规模集成电路技术和计算机辅助设计技术发展的结果。

FPGA器件集成度高、体积小,具有通过用户编程实现专门应用的功能。

它允许电路设计者利用基于计算机的开发平台,经过设计输入、仿真、测试和校验,直到达到预期的结果。

使用FPGA 器件可以大大缩短系统的研制周期,减少资金投入。

更为可贵的是,采用FPGA 器件可以将原来的电路板级产品集成为芯片级产品,从而降低了功耗,提高了可靠性,同时还可以很方便地对设计进行在线修改。

FPGA一般由三种可编程电路和一个用于存放编程数据的SRAM组成,这三种可编程电路是:可编程逻辑块CLB、输入输出模块IOB和互连资源IR,其基本结构如图2.2所示。

可编程逻辑块是实现逻辑功能的基本单元,它们通常规则地排列成一个阵列,散布于整个芯片;可编程输入/输出模块主要完成芯片上逻辑与外部封装脚的接口,它通常排列在芯片的四周;可编程互连资源包括各种长度的连线线段和一些可编程连接开关,它们将各个CLB之间或CLB、IOB之间以及IOB之间连接起来,构成特定功能的电路。

FPGA的功能由逻辑结构的配置数据决定。

工作时,这些配置数据存放在片内的SRAM或熔丝图上。

基于SRAM的FPGA器件,在工作前需要从芯片外部加载配置数据,配置数据可以控制加载过程,在现场修改器件的逻辑功能,即所谓现场编程。

1、可编程逻辑块(CLB)CLB是FPGA的主要组成部分,是实现逻辑功能的基本单元。

它主要由逻辑函数发生器、触发器、数据选择器等电路组成。

CLB中有许多不同规格的数据选择器,分别用来选择触发器激励输入信号、时钟有效边沿、时钟能使信号以及输出信号。

这些数据选择器的地址控制信号均由编程信息提供,从而实现所需的电路结构。

CLB中的逻辑函数发生器均为查找表结构,其工作原理类似于ROM。

2、输入/输出模块(IOB)IOB提供了器件引脚和内部逻辑功能阵列之间的连接。

它主要由输入触发器、输入缓冲器和输出触发/锁存器、输出缓冲器组成,每个IOB控制一个引脚,它们可被配置为输入、输出或双向I/O功能。

3、可编程互连资源(IR)可编程逻辑互连资源可以将FPGA内部的CLB和CLB之间、CLB和IOB之间连接起来,构成各种具有复杂功能的系统。

IR主要由许多金属线段构成,这些金属线段带有可编程开关,通过自动布线实现各种电路的连接。

3 FPGA VS. CPLD可编程逻辑器件的两种主要类型是FPGA(Field Programmable Gate Array,现场可编程门阵列)和CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)。

虽然两者都是可编程逻辑器件,但是两者之间仍有较大的区别。

(1)FPGA是触发器密集型的器件,具有大量的触发器资源;而CPLD是组合逻辑密集型的器件,触发器资源少。

(2)FPGA的集成度远高于CPLD。

(3)FPGA的分段式布线结构决定了其延迟的不可预测性,而CPLD的连续式布线结构决定了它的时延是均匀的和可预测的。

因此,FPGA的应用范围远较CPLD广泛,FPGA可以用工业控制通信消费类电子等各种领域中较为复杂的设计,而CPLD一般只用于实现简单的控制,如地址译码等。