Xilinx PlanAhead 使用方法

AXI-HP接口_DMA_GIC编程

#define INTC_DEVICE_ID

XPAR_SCUGIC_SINGLE_DEVICE_ID

//DMA 控制设备 //GIC 控 制 设 备

ID 号=

#define

DMA_CTRL_IRPT_INTR

XPAR_FABRIC_AXI_CDMA_0_CDMA_INTROUT_INTR //中断号

AXI CDMA 从机接口连接到 PS 通用主机接口 M_AXI_GP1.用于 PS 来配置 AXI 寄存器用于 数据传输和状态检测。 AXI CDMA 主机接口连接到 PS 高性能从机接口 S_AXI_HP0.用于 CDMA 模块读取 DDR 系 统内存源缓冲区数据。 AXI CDMA 主机接口连接到 PS 高性能从机接口 S_AXI_HP2.用于 CDMA 模块将数据写回 DDR 系统内存目的缓冲区。 AXI CDMA 中断从 PL 连接到 PS 全局中断控制器(GIC)。当数据传输完成或传输时有错误发 生,则产生中断。 原文中源缓冲区地址 0x20000000~0x2FFFFFFF,目的缓冲区地址 0x30000000~0x3FFFFFFF, 大 小 均 为 256MB 。 我 们 要 在 ZED Board 上 实 现 , DDR2 的 内 存 空 间 ( 见 下 图 ) 为 0x00100000~0x1FFFFFFF,不能设这么大。

点 OK 确认更新。更新后的 Zynq 表单如下所示

可以看到 PS 和 PL 之间新增的绿色连线生成。 回到 Bus Interfaces 表单,展开 PS7_0,点击 M_AXI_GP1(从名字就能判断,是主机接口, AXI 总线,通用类型接口),将它连接到 axi_interconnect_gp1. 展开 axi_cdma_0,点击 S_AXI_LITE(从名字也能判断,是从机接口,AXI 总线,精简类型 接口),也连接到 axi_interconnect_gp1.连接时选择 ps7_0.M_AXI_GP1.这样就把 PS 和 PL 通 过 axi_interconnect_gp1 这个纽带连接到一起了。 接下来,选择 axi_cmda_0 下的 M_AXI,连接到 axi_interconnect_hp 上;ps7_0 下的 S_AXI_HP0 连接到 axi_interconnect_hp,选择 axi_cdma_0.M_AXI。

如何单独打开Xilinx SDK项目工程

如何单独打开Xilinx SDK项目工程

对于一个ZYNQ的项目,我们在根目录下有如下文件:

PROJECT.cache PROJECT.data PROJECT.sdk PROJECT.srcs PROJECT.ppr

.PPR文件是PLANAHEAD的工程文件,在WINDOWS下面可以直接双击打开,PROJECT.cache PROJECT.data是项目产生的临时文档,可以不用管。

在PROJECT.srcs下面我们找到PROJECT.srcs\sources_1\edk\system目录,这个目录下存在一个system.xmp文件,这就是XPS产生的以顶层实体SYSTEM为名的工程文件名,双击就可以打开XPS工程。

在PROJECT.SDK下面,结构层次为SDK\SDK_Export,包含如下目录:

.METADATA SDKPROJECT SDKPROJECT_BSP HW SYSTEM_HW_PLATFORM

其中.METADATA为临时文件,SKDPROJECT_BSP就是BOARD SUPPORT PAKCAGE工程,HW和SYSTEM_HW_PLATFORM包含了相应的硬件初始化代码,我想问这两个的PS7_init.c/h有什么区别?

SDKPROJECT就是对应的APPLICATION的目录,在这个目录下,并没有相应的工程文件,如何利用SDK单独打开这个工程呢?

打开SDKFIELswitch workspace选择相应的SDK的工作根目录就可以了,所谓的SDK根目录就是包含了.METADATA等文件夹的上层目录。

(完整版)XilinxSDK使用教程

Xilinx SDK使用教程本文参考Xilinx SDK软件内置的教程,打开方法:打开SDK->Help->Cheet Sheets...->Xilinx SDK Tutorials,这里有6篇文档。

本文详细介绍其中的4篇(与Application相关)如何创建一个新的软件应用1.打开SDK,切换到c/c++界面下。

(有两个界面,还有一个是Debug界面,在软件右上角处切换)2.指定一个新的硬件平台项目在SDK开发软件时,需要指定硬件平台。

(如果你打开一个现成的SDK工作空间,这一步可以省略)如果SDK工作空间中没有指定,BSP新建窗口会弹出,询问你硬件平台。

---File > New > Other > Xilinx > Hardware Platform Specification---Next, 显示新的硬件项目对话框。

---设定项目名称,以及由Vivado产生的硬件平台。

---Finish.3.创建一个独立的板级支持包(Board Support Package )---File > New > Board Support Package,打开对话框。

---指定新项目的名字(已初始一个默认的名称)---从CPU下拉列表中,选择目标处理器---从BSP OS下拉列表中,选择操作系统,默认是standalone(没有操作系统)---Finish.弹出BSP设置对话框---配置参数,生成一个BSP---OK4.创建应用项目---File > New > Application Project---指定项目名称---选择OS---选择目标硬件平台---选择目标处理器---选择编程语言---选择一个现有的BSP,或者新建一个---Next---选择一个模板,生成一个可直接运行的软件工程---Finish如何调试一个软件应用1.配置目标连接如果你想用本地设备,你可以跳过这个步骤。

ISE_Design_Flow_14.7

ISE_Design_Flow_14.7ISE设计流程指导⼿册——14.7在本⼿册中,我们将以⼀个简单的实验案例,⼀步⼀步的完成ISE的整个设计流程。

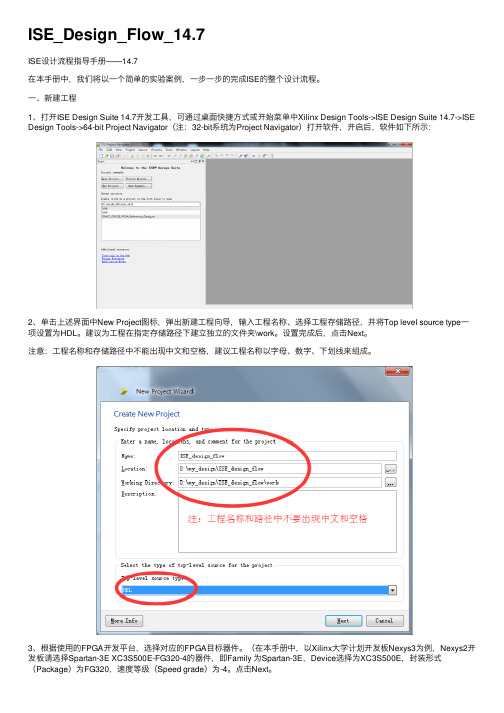

⼀、新建⼯程1、打开ISE Design Suite 14.7开发⼯具,可通过桌⾯快捷⽅式或开始菜单中Xilinx Design Tools->ISE Design Suite 14.7->ISE Design Tools->64-bit Project Navigator(注:32-bit系统为Project Navigator)打开软件,开启后,软件如下所⽰:2、单击上述界⾯中New Project图标,弹出新建⼯程向导,输⼊⼯程名称、选择⼯程存储路径,并将Top level source type⼀项设置为HDL。

建议为⼯程在指定存储路径下建⽴独⽴的⽂件夹\work。

设置完成后,点击Next。

注意:⼯程名称和存储路径中不能出现中⽂和空格,建议⼯程名称以字母、数字、下划线来组成。

3、根据使⽤的FPGA开发平台,选择对应的FPGA⽬标器件。

(在本⼿册中,以Xilinx⼤学计划开发板Nexys3为例,Nexys2开发板请选择Spartan-3E XC3S500E-FG320-4的器件,即Family 为Spartan-3E,Device选择为XC3S500E,封装形式(Package)为FG320,速度等级(Speed grade)为-4。

点击Next。

4、确认相关信息与设计所⽤的的FPGA器件信息是否⼀致,⼀致请点击Finish,不⼀致,请修改。

5、得到如下的空⽩ISE⼯程界⾯,完成空⽩⼯程新建。

⼆、设计⽂件输⼊1、如下图所⽰,点击New Source快捷图标,或在空⽩处右击选择New Source,或在File->NewSource选项,打开设计⽂件添加向导对话框。

2、选择Verilog Module,并输⼊设计⽂件名称如图所⽰,点击Next。

AXI-HP接口_DMA_GIC编程

这时打开 Zynq 表单,如下图所示

单击绿色的 32b GP AXI Master Ports,打开 PS7_0 配置向导。在 User 表单中,展开 GP Master AXI Interface,选择“使能 M_AXI_GP1 接口”,点确认。 单击绿色的 high performance AXI 32/64b Slave Ports,打开 PS7_0 配置向导。在 User 表单中 展开“高性能从机 AXI 接口”, “使能 S_AXI_HP0 接口”——将 HP0 基地址设为 0x,高地址设为 0x。位宽默认 64bit “使能 S_AXI_HP2 接口”——将 HP2 基地址设为 0x,高地址设为 0x。位宽默认 64bit

#define INTC_DEVICE_ID

XPAR_SCUGIC_SINGLE_DEVICE_ID

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

ISE软件使用

一、软件Xilinx的软件主要是ISE, EDK, ChipScope Pro, System Generator, PlanAhead, ModelSim,如果要算上AccelDSP也凑合,不过相信国内没多少人用。

ISE是主要的逻辑设计软件,其他软件的具体实现功能都依附于ISE。

ISE有Foundation版和WebPack版。

WebPack版免费,Foundation版收费。

两者的区别是支持的器件不同。

功能是相同的。

WebPack版支持的功能可以看/ise/products/webpack_config.htm。

Foundation的话当然全支持拉,要看的话在这里/ise/logic_design_prod/foundation.htm。

说这些的目的就是,如果你的器件WebPack支持,就直接到网上下载WebPack吧,没有版权之类的后顾之忧;如果不行,Verycd上找些东西还是挺方便的。

ModelSim MX有免费的starter version,可以和ISE WebPack一起下载,安装以后在开始里面点licens_e request就可以申请starter的使用权了。

另外,可以VHDL和Verilog各申请一个,那么就可以仿真两种语言了,不过不支持mix language。

/ise/verification/mxe_details.html不过那一页说的ModelSim XE的use case不准的,XE,PE,SE的差别还是仔细看这里吧。

/xlnx/xil_ans_display.jsp?getPagePath=24506ChipScope有(好像是)60天的评估版。

/chipscopePlanAhead(稍微介绍下子,没有接触过的朋友可能不知道这是什么)PlanAhead是ISE7以后推出的软件,它的主要功能是对一个综合后的NGC/EDIF网表进行布局布线的规划。

听上去功能有点像FloorPlanner,但是功能却强大得多。

在XILINX中差分输入信号到单端信号的转换

在 XILINX 中差分输入信号到单端信号的转换

在 XILINX 中差分输入信号到单端信号的转换

设计者:sunchanghong 笔名: 海豚

sunchanghong may ,2013

Suncha nghong Beijing, china QQ:750506590 Email:haitu n200@

1/4

在 XILINX 中差分输入信号到单端信号的转换

在 XILINX 中差分输入信号到单端信号的转换

一 理论基础: 1 理论: 差分传输是一种信号传输技术,区 别于传统的一根信号线一根地线的 做法,差分传输

如图所示,在这两根线上都传输信号,这两个信号的振幅相等,相位相反,在这两根线上的 传输的信号就是差分信号。信号的接收端比较这两个电压的差值来判断发送端发送的是 0 还是 1。在电路板上,差分走线必须是等长、等宽、紧密靠近,且在同一层面的两根线。

二 XILINX FPGA 中差分信号的使用方 在一个 module 模块中讲述差分信号转换到单端信号的方法 1 在代码中的定义 module chafen( clk_p, clk_n iin_p, iin_n, qin_p, qin_n, … );

Input clk_p; Input clk_n; Input [2:0] iin_p;

IBUFDS Qin_u0 ( .I(qin_p[0]), .IB(qin_n[0]), .O(qin[0]) );

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PlanAhead这个软件出现在ISE工具包里已经很久了。

具体是什么时候集成进去的,我也不去深究了。

但是,在ISE12里,PlanAhead的功能出现了很大的变化,不再仅仅是过去的约束软件,而是加入了RTL Design(Synthesize),Netlist Design(Implement),等传统上Project Navigator中的功能。

现在,在PlanAhead中即可进行全部的FPGA设计。

据称,Xilinx可能在14或者以后的版本中,取消Project Navigator。

那么本文就着重的说说PlanAhead的功能。

图 1 PlanAhead界面

图2所示,是PlanAhead的左边工具栏。

图 2 PlanAhead左边栏

上面的Project Manager用于综合管理工程文档。

Add Sources创建、管理源文件;IP Catalog创建、管理IPcore的工程设定。

Elaborate显示RTL图,并可以实现资源和功率的估计等等(在Synthesize之前,提高速度)。

RTL Design与上面的Elaborate相同,都是打开RTL Design的功能。

Synthesize是运行Xilinx 的XST Synthesis,综合工程。

Netlist Design用来配置已经综合过的工程,包括显示综合过的RTL图,估计资源占用,配置约束,时序仿真等等。

Implement执行ISE Implementation。

Implemented Design观察时序和布局结果,并可以优化约束。

Program and Debug按钮,用来生成烧写文件,启动ChipScope,iMPACT。

我们再进一步展开几个执行按钮的下拉菜单。

如图3所示。

图 3 Synthesize 的下拉菜单

进入到Synthesis Setting,得到图4。

图 4 Synthesis Setting 界面

这里面可以选择使用的约束集合(在add sources里添加约束集合);在options里应用不同的综合选项综合。

进入到Create Multiple Runs里,如图5。

图 5 Create Multiple Runs界面

这里面建立的多个synthesis可以同步运行,充分利用多核cpu的优势。

而这些多个synthesis,可以是有不同的device,或者不同的Constraint sets。

下面通过一个例子说明PlanAhead如何创建工程。

图6所示是PlanAhead的启动界面。

图 6 PlanAhead界面

选择Create New Project,进入新建工程界面,如图7所示。

图7 New Project 下面是选择工程名和位置,如图8。

图8 New Project

下面是选择Design Source,如图9。

图9 Design Source

这里我们看到5个选项。

这5个选项对应着不同的设计层次。

第一个Specify RTL Sources,是导入RTL级的设计源文件,包括Verilog、VHDL代码、库,还有Xilinx IPCORE等等。

是最开始的设计文件。

第二个Specify Synthesized(Edif or NGC)netlist,是导入已经综合过的网表文件,做分析、约束和布局布线。

第三个Create an IO Planning Project,这个选项就是产生一个管脚约束文件,不做其他的事情。

即是老版本的PA做的事情。

第四个Import ISE Place& Route Results,导入已经布局布线后的工程,作分析和优化布局。

第五个Import ISE Project,直接导入ISE的工程。

我们现在选择第一个,直接设计RTL文件。

图10所示的是导入源文件的界面。

图10 Add Sources

这里我们直接导入PA的一个示例工程的源代码,位置是

ISE_DS\PlanAhead\testcases\PlanAhead_Tutorial\Projects\project_bft_core_hdl\project_bft_core_hdl.srcs\sources_1\imports,里面hdl下面的文件作为文件导入进work lib,bftLib直接作为目录导入,修改library为bftLib。

结果如图11所示。

图11 Added Sources

后面的添加IPcore直接略过,下面是添加约束文件。

约束文件的位置是

ISE_DS\PlanAhead\testcases\PlanAhead_Tutorial\Projects\project_bft_core_hdl\project_bft_core_hdl.srcs\constrs_1\imports\So urces\bft.ucf。

如图12所示。

图12 Add Constraints 然后是选择器件,我们选择Vertix-6 xc6vcx75tff784-1器件,如图13。

图13 Device

至此,工程建立完毕,显示Project Summary,如图14。

图14 Project Summary PlanAhead的界面如图15。

图15 PlanAhead

下面开始综合工程,在Synthesize右边的下拉菜单中,选择Synthesize setting,图16。

选择options右边的按钮,进入Design Run Setting,图17。

图16 Synthesize setting

图17 Design Run Settings

这里面可以配置修改XST的综合选项,还可以使用不同的综合策略来进行综合,我们这里面就不更改设置了,用它默认的配置就可以。

之后在Synthesize setting中点击RUN,执行综合。

综合完成之后,在Synthesize Completed对话框中选择Open Netlist Design,打开Netlist Design界面。

在上面的下来菜单中选择I/O Planning,打开I/O配置页面,在下面的I/O Ports中,分配管脚。

如图18所示。

图18 I/O Planning

打开菜单栏Windows ->Report,选择XST Report,可以查看综合报告,如图19。

图19 XST Report

点击左侧的Implement,执行布局布线操作。

完成之后打开Implemented Design,查看结果。

在下面选择Timing Results,可以看到时序分析的结果。

如图20。

图20 Timing Results

点击Windows -> Device,在Device View的窗口下点击Show/Hide I/O Nets按钮。

可以查看器件间的逻辑连接情况。

如图21所示。

图21 I/O Nets

在下面的Timing Results中点击一条路径,可以在Device框中查看到对应的路径,图22。

右击path,选择Path Properties,可以查看这条路径经过的元件,图23

图22 Timing Results

图23 Path Properties

在Timing Result对话框下,点击原理图按钮,可以看到这条路径的原理图,图24。

图24。