CIC积分梳状滤波器的设计

CIC滤波器的原理与设计

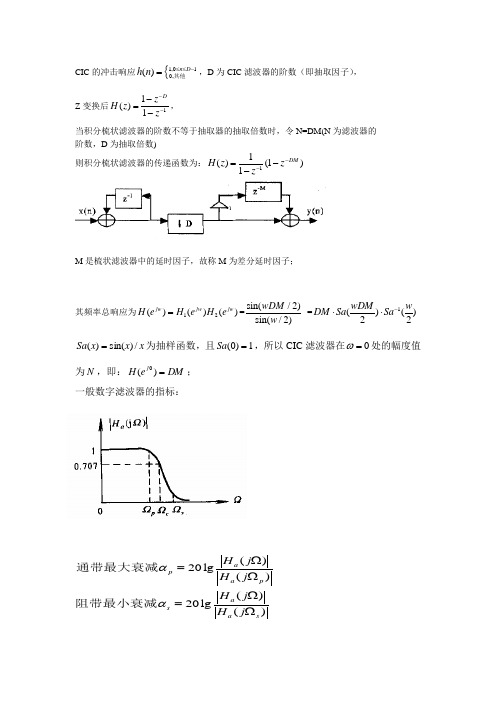

CIC 的冲击响应{1,010,()n D h n ≤≤-=其他,D 为CIC 滤波器的阶数(即抽取因子),Z 变换后11()1Dz H z z ---=-,当积分梳状滤波器的阶数不等于抽取器的抽取倍数时,令N=DM(N 为滤波器的 阶数,D 为抽取倍数)则积分梳状滤波器的传递函数为:)1(11)(1DM z zz H ----=M 是梳状滤波器中的延时因子,故称M 为差分延时因子;其频率总响应为12()()()jw jw jwH e H e H e ==sin(/2)sin(/2)wDM w =1()()22wDM wDM Sa Sa -⋅⋅x x x Sa /)sin()(=为抽样函数,且1)0(=Sa ,所以CIC 滤波器在0=ω处的幅度值为N ,即:DM e H j =)(0; 一般数字滤波器的指标:()20lg()()20lg ()a pa p a s a s H j H j H j H j ααΩ=ΩΩ=Ω通带最大衰减阻带最小衰减即:CIC 幅频特性响应曲线图由其频率响应函数可以看出其主瓣电平最大为D ,旁瓣电平为21.51()sin(3/2)/sin(3/2)sin(3/2)j DMH e DM DM ωπωπππ=⋅==,旁瓣与主瓣的差值 (用dB 数表示)为: dB A DM s 46.1323lg 20lg201===πα 可计算出旁瓣与主瓣的差值约为13.46,意味着阻带衰减很差,单级级联时旁瓣电平很大,为降低旁瓣电平,增加阻带衰减采用级联的方式,N 级频率响应为:)2()2()()2/sin()2/sin()(ωωωωωQ Q Q Qj Q Sa DM Sa DM DM e H -⋅⋅=⎥⎦⎤⎢⎣⎡=, 可得到N 级CIC 的旁瓣抑制 dB Q Q A DM Q Qs )46.13(23lg 20)lg(201⨯=⋅==πα 分析一下发现在Q 级联时多出了Q DM 这个处理增益,因此分析一下尽量减少带容差(通带衰减),即,在通带,幅度应尽量平缓;下面就它的幅平响应曲线来分析:00()20lg ()()20lg()ps j a p jw a j a s jw a H e H eH e H e αα==1、设在红线w1处抽取的信号带宽很窄,为无混叠信号的带宽,能很好的对窄带信号进行滤波,去除掉高频信号噪声;且在绿线w2=2pi/DM-w1处衰减值足够大,则在其信号带宽,红线到绿线,信号给CIC 滤 波器带来的混叠就可以忽略,计算此时阻带衰减:)2/sin()2/sin(lg 20()(lg 2022012w DM w DM e H e H A jw j ==·引入带宽比例因子b=B/(fs/DM ), B 为抽取信号的带宽,D 为抽取因子,M 为延时因子;fs 为输入端采样率,则w1=b*2pi/DM ;带入可化简得:b A lg 201-≈; (假设b=0.01;即fs=100MHz ,D=20,信号带宽为50khz,此时衰减为40dB);可见单级的CIC 滤波器的无混叠信号带宽的阻带衰减能达到40dB;;并不怎么大,适用于较粗略的滤波,适合放在第一级抽取;如果采用级联的方式可以加大无混叠信号带宽;但是满足的通带不够窄;2、在红线w1处幅度不能下降太多,通带幅值容差不能太大,否则会引起高频失真;设该带容差为s δ,则,)()(lg 2010jw j s e H e H =δ将w1带入可简化得)sin(lg 20b bs ππδ≈,当N 级时,其带容差也会增大;由上面分析可知,阻带衰减和带容差,只与带宽比例因子b 有关,Df Bb s /=,分析可知,在信号带宽一定的前提下,应尽可能采用小的抽取因子,或增大输入采样率;故一般把它放在抽取系统的第一级,所以在配置CIC 时,信号带宽,采样率,抽取因子,综合考虑,下面是阻带衰减和通带衰减的一个表:表1:大抽取因子下的通带衰减由CIC频幅响应图可以发现,幅频特性的零点位于1/M处(M取值为整数),这说明差分因子M决定了零点的位置;抽取因子D狭定了抽取后信号的采样频率,它同差分延时因子M一起还决定了主瓣和旁瓣的宽度;级数Q可以用来控制阻带衰减,Q越大阻带衰减越大,通带的混叠就越小,但Q越大,通带主瓣衰减也越大,所以Q不可太大,不宜超过5级。

宽带通信芯片中级联积分梳状插值滤波器的优化设计

宽带通信芯片中级联积分梳状插值滤波器的优化设计孙晨;赵毅强;刘强;李旭【摘要】级联积分梳状(CIC)滤波器由于其结构简单、高效等优点,经常作为宽带通信芯片中的抽取器或插值器.随着通信系统以及超大规模集成电路的发展,芯片集成密度越来越高,需要对芯片中关键模块积分梳状滤波器进行面积的优化.为此,设计一种应用于无线宽带射频芯片的CIC插值滤波器.通过位宽优化方法减少滤波器内部节点位宽,并在增益校正部分采用输出截位后的正则有符号数字量编码乘法代替全位宽二进制补码乘法.实验结果表明,与优化前的CIC插值滤波器相比,该滤波器的电路面积可优化58%左右.【期刊名称】《计算机工程》【年(卷),期】2015(041)008【总页数】5页(P252-255,261)【关键词】级联积分梳状插值滤波器;宽带通信芯片;位宽优化;增益校正;正则有符号数字量编码乘法;面积优化【作者】孙晨;赵毅强;刘强;李旭【作者单位】天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072【正文语种】中文【中图分类】TN471 概述现代通信系统中经常需要根据感兴趣的信号来调整采样率,一般通过抽取或插值来降低或提高采样率。

积分梳状滤波器具有结构简单、高效等优点,广泛用于多采样率系统中[1-3],作为抽取器或插值器。

根据级联积分梳状(Cascaded Integrator Comb,CIC)滤波器理论直接设计的滤波器虽然能满足性能的要求,但是电路面积大,往往需要根据实际应用采用一定的优化方法来减小CIC 滤波器的面积。

本文针对一款无线宽带射频芯片的需求,开展CIC 插值滤波器的设计,要求数据输入速率为20 MHz、输入采样率提高10 倍、旁带抑制大于50 dB、输出波纹小于0.05 dB 并保持输入输出位宽同为12 bit。

根据文献[4]提出的CIC 滤波器设计方法设计了一种5 级、插值因子为10、延迟因子为1 的CIC插值滤波器。

cic滤波器原理详解

级联积分梳状(Cascade Integrator Comb,CIC)[1]滤波器结构简单、标准化,是高速抽取器中十分简单有效的抗混叠滤波单元,已被广泛使用于多抽样率信号处理系统中。

其组成只有积分器、加法器、寄存器,没有乘法器,使得CIC滤波器非常适合在具有较强实时性和并行处理能力的FPGA 上实现。

但是其阻带衰减和通带波纹的相互抑制限制了其滤波性能。

锐化级联积分梳状滤波器[2]、CIC 滤波器的部分锐化[3]、在CIC 滤波器级联分解的基础上级联一级余弦滤波器[4]、二级补偿CIC 滤波器( TSC -CIC)[5]、内插二阶多项式级联积分梳状滤波器(ISOP-CIC)[6]都是用来进行CIC滤波器改进的技术。

但上述CIC 滤波器的改进或只是降低了通带衰减,或只是提高了阻带衰减,或同时降低通带衰减、提高阻带衰减,但是占用硬件逻辑资源较多。

(完整版)CIC滤波器的原理与设计

CIC 的冲击响应{1,010,()n D h n ≤≤-=其他,D 为CIC 滤波器的阶数(即抽取因子),Z 变换后11()1Dz H z z ---=-,当积分梳状滤波器的阶数不等于抽取器的抽取倍数时,令N=DM(N 为滤波器的 阶数,D 为抽取倍数)则积分梳状滤波器的传递函数为:)1(11)(1DM z zz H ----=M 是梳状滤波器中的延时因子,故称M 为差分延时因子;其频率总响应为12()()()jw jw jwH e H e H e ==sin(/2)sin(/2)wDM w =1()()22wDM wDM Sa Sa -⋅⋅x x x Sa /)sin()(=为抽样函数,且1)0(=Sa ,所以CIC 滤波器在0=ω处的幅度值为N ,即:DM e H j =)(0; 一般数字滤波器的指标:()20lg()()20lg ()a pa p a s a s H j H j H j H j ααΩ=ΩΩ=Ω通带最大衰减阻带最小衰减即:CIC 幅频特性响应曲线图由其频率响应函数可以看出其主瓣电平最大为D ,旁瓣电平为21.51()sin(3/2)/sin(3/2)sin(3/2)j DMH e DM DM ωπωπππ=⋅==,旁瓣与主瓣的差值 (用dB 数表示)为: dB A DM s 46.1323lg 20lg201===πα 可计算出旁瓣与主瓣的差值约为13.46,意味着阻带衰减很差,单级级联时旁瓣电平很大,为降低旁瓣电平,增加阻带衰减采用级联的方式,N 级频率响应为:)2()2()()2/sin()2/sin()(ωωωωωQ Q Q Qj Q Sa DM Sa DM DM e H -⋅⋅=⎥⎦⎤⎢⎣⎡=, 可得到N 级CIC 的旁瓣抑制 dB Q Q A DM Q Qs )46.13(23lg 20)lg(201⨯=⋅==πα 分析一下发现在Q 级联时多出了Q DM 这个处理增益,因此分析一下尽量减少带内容差(通带衰减),即,在通带内,幅度应尽量平缓;下面就它的幅平响应曲线来分析:00()20lg ()()20lg()ps j a p jw a j a s jw a H e H eH e H e αα==1、设在红线w1处抽取的信号带宽很窄,为无混叠信号的带宽,能很好的对窄带信号进行滤波,去除掉高频信号噪声;且在绿线w2=2pi/DM-w1处衰减值足够大,则在其信号带宽内,红线到绿线,信号给CIC 滤波器带来的混叠就可以忽略,计算此时阻带衰减:)2/sin()2/sin(lg 20()(lg 2022012w DM w DM e H e H A jw j ==·引入带宽比例因子b=B/(fs/DM ), B 为抽取信号的带宽,D 为抽取因子,M 为延时因子;fs 为输入端采样率,则w1=b*2pi/DM ;带入可化简得:b A lg 201-≈; (假设b=0.01;即fs=100MHz ,D=20,信号带宽为50khz,此时衰减为40dB);可见单级的CIC 滤波器的无混叠信号带宽内的阻带衰减能达到40dB;;并不怎么大,适用于较粗略的滤波,适合放在第一级抽取;如果采用级联的方式可以加大无混叠信号带宽;但是满足的通带不够窄;2、在红线w1处幅度不能下降太多,通带内幅值容差不能太大,否则会引起高频失真;设该带内容差为s δ,则,)()(lg 2010jw j s e H e H =δ将w1带入可简化得)sin(lg 20b bs ππδ≈,当N 级时,其带内容差也会增大;由上面分析可知,阻带衰减和带内容差,只与带宽比例因子b 有关,Df Bb s /=,分析可知,在信号带宽一定的前提下,应尽可能采用小的抽取因子,或增大输入采样率;故一般把它放在抽取系统的第一级,所以在配置CIC 时,信号带宽,采样率,抽取因子,综合考虑,下面是阻带衰减和通带衰减的一个表:表1:大抽取因子下的通带衰减由CIC频幅响应图可以发现,幅频特性的零点位于1/M处(M取值为整数),这说明差分因子M决定了零点的位置;抽取因子D狭定了抽取后信号的采样频率,它同差分延时因子M一起还决定了主瓣和旁瓣的宽度;级数Q可以用来控制阻带衰减,Q越大阻带衰减越大,通带内的混叠就越小,但Q越大,通带内主瓣衰减也越大,所以Q不可太大,不宜超过5级。

基于FPGA的多级CIC滤波器的设计与实现

基于FPGA的多级CIC滤波器的设计与实现王璞;张玉明;田野;张坤;杨军【期刊名称】《云南大学学报:自然科学版》【年(卷),期】2018(40)4【摘要】积分梳状(CIC)滤波器是一种高效的滤波器,广泛应用于无线通信技术的数字下变频和上变频端.但传统结构的级联CIC滤波器每个寄存器的位宽是固定的,在处理低频信号会造成高频的运算带宽过大,浪费计算机硬件资源的不足.利用Hogenauer"剪除"理论对每一级的输出位宽进行截短,提高CIC滤波器的性能,通过级联多个单级CIC滤波器优化其结构,构建了多级CIC滤波器;同时利用FPGA技术的重构性强、扩展性好、硬件资源占有少、成本低、可靠性高的特点,采用Verilog HDL语言设计实现了各个模块,最终基于FPGA设计完成的多级CIC滤波器模型,不仅节约了硬件资源,还使CIC滤波器每个寄存器的位宽可变.通过Modelsim对模型进行仿真并下载到以Altera DE2的EP2C35F672C6为目标芯片验证,达到了设计要求.【总页数】6页(P676-681)【关键词】CIC滤波器;数字上变频;数字下变频;Hogenauer“剪除”理论;现场可编程门阵列(FPGA)【作者】王璞;张玉明;田野;张坤;杨军【作者单位】云南大学信息学院【正文语种】中文【中图分类】TN713【相关文献】1.基于FPGA的CIC滤波器的设计与实现 [J], 徐艳;田克纯2.多级CIC滤波器的FPGA实现 [J], 谢海霞;孙志雄3.CIC抽取滤波器的MATLAB设计及FPGA实现 [J], 杨翠娥4.基于FPGA的CIC抽取滤波器设计与实现 [J], 雷能芳5.基于FPGA的CIC滤波器优化设计与实现 [J], 许彦辉;年夫顺;张超因版权原因,仅展示原文概要,查看原文内容请购买。

cic滤波器原理详解

cic滤波器原理详解

级联积分梳状(Cascade Integrator Comb,CIC)[1]滤波器结构简单、标准化,是高速抽取器中十分简单有效的抗混叠滤波单元,已被广泛使用于多抽样率信号处理系统中。

其组成只有积分器、加法器、寄存器,没有乘法器,使得CIC滤波器非常适合在具有较强实时性和并行处理能力的FPGA 上实现。

但是其阻带衰减和通带波纹的相互抑制限制了其滤波性能。

锐化级联积分梳状滤波器[2]、CIC 滤波器的部分锐化[3]、在CIC 滤波器级联分解的基础上级联一级余弦滤波器[4]、二级补偿CIC 滤波器( TSC -CIC)[5]、内插二阶多项式级联积分梳状滤波器(ISOP-CIC)[6]都是用来进行CIC滤波器改进的技术。

但上述CIC 滤波器的改进或只是降低了通带衰减,或只是提高了阻带衰减,或同时降低通带衰减、提高阻带衰减,但是占用硬件逻辑资源较多。

CIC插值滤波器的FPGA设计与实现资料

CIC插值滤波器的FPGA设计与实现摘要:基于多速率信号处理原理,设计了用于下变频的CIC插值滤波器,由于CIC 滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现,所以本文分析了CIC滤波器的原理,性能及影响参数,借助MATLAB设计符合系统要求CIC 滤波器,并利用Modelsim软件建模仿真,验证CIC滤波器性能是否达到要求。

(一)CIC滤波器基本原理A.CIC滤波器的基本单元CIC滤波器主要由积分滤波Integrator和梳状滤波Comb两个基本单元部分构成。

典型的CIC滤波器的结构,它由两个基本单元I(积分滤波器)和C(梳状滤波器)级联构成。

本设计主要针对插值滤波器,所以插值滤波器的结构示意图如图1-1所示:图 1-1 3级级联的CIC插值滤波器结构示意图积分器和梳状滤波器之间是一个采样率转换器,对于CIC插值器而言,它完成在每一个样值后补上R-1个0值的工作,,对于CIC抽取器来说,它完成在实际的抽取工作,每R个样值中取样一个。

R(插值倍数),M(延迟因子,一般取1或者2)以及N(级联级数)是影响CIC 滤波器的三个参数,它们的值需根据通带性能的需求而设定。

(二)CIC插值滤波器的设计流程根据CIC滤波器的原理,本设计的流程如图2-1所示:图2-1 CIC 插值滤波器的设计流程图(三)模型的建立和测试A .位宽策略对于数字滤波器,一个不得不考虑的问题是为防止溢出每一级所需的位宽。

对于抽取器来说,CIC 滤波器的输出增益为(*)NG R M = (3-1)所以,在全精度的情况下,最后一级输出的位宽为2log (*)out in B B N R M =+ (3-2)其中in B 表示输入数据的宽度,为了保证精度,每一个积分器和梳状滤波器的输入输出位宽都为out B 。

对于插值器而言,输出增益为212,1,2,....2(*)/,1, 2......2i i N i N i N G R M R i N N N --⎛⎫== ⎪ ⎪=++⎝⎭ (3-3)因此,第i 级为避免溢出所需要的位宽为2log ()i in i W B G =+ (3-4)最后一级输出位宽为22log (*)log out in B B N R M R=+- (3-5)在实际当中,当差分延时M=1时,为保证稳定,所有积分器的位宽在理论值的基础上加一。

宽带通信芯片中级联积分梳状插值滤波器的优化设计

宽带通信芯片中级联积分梳状插值滤波器的优化设计

孙晨;赵毅强;刘强;李旭

【期刊名称】《计算机工程》

【年(卷),期】2015(041)008

【摘要】级联积分梳状(CIC)滤波器由于其结构简单、高效等优点,经常作为宽带通信芯片中的抽取器或插值器.随着通信系统以及超大规模集成电路的发展,芯片集成密度越来越高,需要对芯片中关键模块积分梳状滤波器进行面积的优化.为此,设计一种应用于无线宽带射频芯片的CIC插值滤波器.通过位宽优化方法减少滤波器内部节点位宽,并在增益校正部分采用输出截位后的正则有符号数字量编码乘法代替全位宽二进制补码乘法.实验结果表明,与优化前的CIC插值滤波器相比,该滤波器的电路面积可优化58%左右.

【总页数】5页(P252-255,261)

【作者】孙晨;赵毅强;刘强;李旭

【作者单位】天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072

【正文语种】中文

【中图分类】TN47

【相关文献】

1.级联积分梳状滤波器与DSP的实现 [J], 李强;吴顺君

2.基于FPGA的级联积分梳状滤波器设计与实现 [J], 李铜川;陈铭;薛敏彪

3.基于外推和级联积分梳状滤波器的多普勒插值方法 [J], 罗勇;吴文启;何晓峰;郭瑶

4.级联积分梳状滤波器在超声检测系统中的应用 [J], 周文佳;毛捷;冷涛;廉国选

5.可编程多级级联积分梳状内插滤波器的设计 [J], 范晓捷;王祖锦;张甘英;朱夏冰;万书芹

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ቤተ መጻሕፍቲ ባይዱerilog HDL开发流程如下图:

设计规范

文本编辑

功能仿真

逻辑综合

布局布线

时序仿真

编程下载

6.仿真综合

Quartus II 是Altera公司的综合性PLD开发软件, 支持原理图、VHDL、VerilogHDL以及AHDL (Altera Hardware Description Language)等多 种设计输入形式,内嵌自有的综合器以及仿真器, 可以完成从设计输入到硬件配置的完整PLD设计 流程。 Quartus II 通过和DSP Builder工具与 Matlab/Simulink相结合,可以方便地实现各种 DSP应用系统;支持Altera的片上可编程系统 (SOPC)开发,集系统级设计、嵌入式软件开 发、可编程逻辑设计于一体,是一种综合性的开 发平台。

3.CIC滤波器的简单介绍

CIC(Cascaded Integral Comb)抽取滤 波器,最初由Hogenauer提出,因为它结构 简单,而且实现时无需乘法器和系数的存 储,所以作为一种简单有效的抽样率转换 方法,CIC已被广泛的应用于通信和信号处 理领域。CIC滤波器通常是由一个积分梳状 滤波器和一个抽取滤波器级联组合而成, 其中级联的积分梳状滤波器又分为积分部 分和梳状部分。

用Quartus II对三级滤波器进行仿真,得出波形

• 从波形中可以看出 • 输入 X_in=100,ComReg0[0]=496000,ComReg1[0]=4 96000, • ComReg2[0]=0,ComReg3[0]=0,y_out=0. • 2.输入X_in为100,ComReg0[0]=4166400, ComReg1[0]=4166400, ComReg2[0]=496000, ComReg3[0]=0,y_out=0. • 3.输入X_in为100, ComReg0[0]=14288000, ComReg1[0]=13792000, • ComReg2[0]=4166400, ComReg3[0]=496000,y_out=496000.

5. Verilog HDL代码实现

Verilog HDL是一种硬件描述语言,用它 可以表示逻辑电路图、逻辑表达式,还可 以表示数字逻辑系统所完成的逻辑功能。 它是由GDA公司的PhilMoorby在1983年末 首创的,最初只设计了一个仿真与验证工 具,之后又陆续开发了相关的故障模拟与 时序分析工具。

CIC积分梳状滤波器的设计

1.课题的写作目的和思路

本课题的任务就是了解CIC滤波器的基 本原理、特点。对CIC滤波器出现的几个问 题给出了解决方案,以及对其进行改善。 最后用采用Quartus II仿真软件对三级CIC 滤波器代码进行测试仿真。

2.CIC滤波器的发展史

随着信息时代和数字世界的到来,数 字信号处理在通信、语音、图像、自动控 制、雷达、军事、航空航天、医疗和家用 电器等众多领域得到了广泛的应用。在数 字信号处理应用中,数字滤波器十分重要 并已获得广泛应用。数字信号处理中多采 样率的应用非常普遍,尤其在软件无线电中 应用广泛。 CIC滤波器就是多采样处理常 用的器件之一。

4.滤波器设计时遇到的问题与改进

在DSP设计中,几乎都会面对如何解决 溢出问题,CIC滤波器设计也不例外。扩展 表示精度可以解决寄存器溢出问题。该办法 有一个缺点是滤波器各阶段信号表示精度需 要扩展,从而造成部分寄存器浪费。 CIC滤 波器的阻带衰减和过渡带特性不是很好,可 以通过级联的方法来实现加大过渡带和阻带 的衰减,还可以通过在CIC滤波器后加补偿 滤波器的方法来实现对CIC滤波器性能的改 进。