优化高速接口的时序裕量

芯片后端时序名词

芯片后端时序名词1. **Setup Time(建立时间)**- **词性解释**:名词短语。

- **意思**:在时钟信号有效沿到来之前,数据信号必须保持稳定的最小时间间隔。

就好像运动员起跑前的准备动作,必须在发令枪响(时钟有效沿)之前完成准备(数据稳定)。

- **用法**:常用来评估芯片内部电路时序是否满足要求,例如“这个寄存器的输入信号需要满足setup time要求。

”- **近义词**:无(在这个特定概念下较难找到非常准确的近义词)- **双语例句**:- 英文:The setup time of this flip - flop is very crucial for the correct operation of the circuit. If it is not met, data may be latched incorrectly.- 中文:这个触发器的建立时间对电路的正确运行非常关键。

如果不满足,数据可能会被错误锁存。

2. **Hold Time(保持时间)**- **词性解释**:名词短语。

- **意思**:时钟信号有效沿到来之后,数据信号必须保持稳定的最短时间。

这就像是火车到站后(时钟有效沿),乘客(数据)还得在站台上停留一会儿(保持稳定)。

- **用法**:用于分析芯片电路的时序关系,如“检查这个电路模块的hold time是否合格。

”- **近义词**:无- **双语例句**:- 英文:We must ensure that the hold time of the signal is long enough to prevent data corruption.- 中文:我们必须确保信号的保持时间足够长,以防止数据损坏。

3. **Clock Skew(时钟偏斜)**- **词性解释**:名词短语。

- **意思**:同一个时钟信号到达不同寄存器的时间差异。

可以想象成一群人听同一个命令(时钟信号),但由于距离不同(物理布局等原因),听到命令的时间有先后。

超高速数字电路设计与优化

超高速数字电路设计与优化随着计算机技术不断发展,数字电路已经成为现代电子系统中的核心组成部分,在各种数字处理和通信系统中得到广泛应用。

超高速数字电路是指工作速度在千兆赫到数千兆赫级别的数字电路。

在这样的高速电路中,时序设计和电路优化变得尤其重要,因为它们对电路性能的影响会更加显著。

本文将探讨超高速数字电路的设计和优化。

a. 时序设计时序设计是超高速数字电路设计的重要组成部分。

与普通数字电路的时钟周期相比,超高速数字电路要求时钟信号的频率更高,时钟周期更短,以保证数字信号的处理速度。

在时序设计中,需要考虑以下因素:1) 时钟分频及同步电路设计分频电路是超高速数字电路的常用设计技术。

分频电路可以将高频时钟信号转换为低频时钟信号,用于控制电路的不同模块和时间序列。

在实现电路分频的同时,还需要考虑同步设计,确保各个部分的时序一致性。

2) 时序约束时序约束是指电路处理数字数据时,输入和输出信号之间的时间差。

超高速数字电路对时序约束的要求更严格,需要考虑各电路模块之间的传输时间、时钟延迟等因素。

合理的时序约束可以提高电路运行速度和可靠性。

b. 电路优化在超高速数字电路设计中,电路优化是提高电路性能的重要途径。

电路优化可以使电路结构更紧凑,减小时延和功耗,提升电路的响应速度和稳定性。

电路优化主要涉及以下方面:1) 电路结构的优化优化电路结构可以使电路模块更紧凑,减小时延和功耗。

常用的优化方法包括并行结构设计和级联结构设计。

并行结构设计可以将电路多个组成部分并联,实现快速运算;级联结构设计可以增强电路稳定性和运行速度。

2)布局优化和地线设计布局优化和地线设计是减小电路时延和抑制噪声的重要手段。

优化布局可以将电路模块更加紧密地分布在电路板上,减小信号传输时间;合理的地线设计可以减小传输线的阻抗和噪声,提高电路信噪比。

3)功耗优化功耗优化是提高电路能效的手段。

在超高速数字电路设计中,功耗的大小会影响电路温度和电路的稳定性。

电子系统中的高速IO接口设计与优化策略

电子系统中的高速IO接口设计与优化策略在现代电子系统中,高速IO接口的设计和优化策略起着至关重要的作用。

高速IO接口是指在电子设备之间传输数据的通道,它的性能直接影响着整个系统的速度和稳定性。

本文将探讨高速IO接口设计的一些基本原则和优化策略。

首先,高速IO接口的设计需要考虑信号完整性。

在高速传输过程中,信号的完整性是至关重要的。

信号完整性包括减小信号的噪声、降低信号的时延和抖动等方面。

为了实现信号完整性,可以采取一些措施,例如使用阻抗匹配技术,减少信号的反射和串扰。

此外,还可以使用差分信号传输来减少噪声和抖动。

其次,高速IO接口的设计需要考虑功耗和热管理。

随着电子设备的性能提升,功耗和热量也不可避免地增加。

为了降低功耗和有效管理热量,可以采用一些优化策略。

例如,可以使用低功耗的设计技术,如功耗管理技术和动态电压频率调整技术。

此外,还可以使用散热技术,如散热片和风扇,来有效地降低温度。

另外,高速IO接口的设计需要考虑可靠性和容错性。

在高速传输过程中,由于环境干扰和设备故障等原因,可能会出现数据传输错误。

为了提高可靠性和容错性,可以采取一些措施。

例如,可以使用纠错码技术来检测和纠正数据传输错误。

此外,还可以使用冗余设计和备份机制来确保数据的可靠传输。

此外,高速IO接口的设计还需要考虑兼容性和互操作性。

在现代电子系统中,不同设备之间需要进行数据交换和通信。

为了实现兼容性和互操作性,可以采用一些标准化的接口和协议。

例如,可以使用USB、HDMI、PCI Express等标准接口来实现设备之间的数据传输和通信。

最后,高速IO接口的设计还需要考虑成本和可扩展性。

在电子系统的设计过程中,成本和可扩展性是两个重要的考虑因素。

为了降低成本和提高可扩展性,可以采用一些经济实用的设计策略。

例如,可以使用集成电路和芯片封装技术来降低成本。

此外,还可以使用模块化设计和可编程逻辑器件来提高系统的可扩展性。

综上所述,高速IO接口的设计与优化策略是电子系统设计中的重要环节。

高速总线的时序分析方法及DDR计算实例

高速总线的时序分析方法及DDR计算实例韩玉涛【摘要】随着高速存储器在通信系统和图像处理等领域的普遍使用,如果系统设计中的总线时序问题得不到满足,将会严重影响系统的运行稳定性.在详细介绍了高速总线的数学模型及时序分析方法的基础上,根据时序分析方法给出了SMP8634多媒体处理器与DDR DRAM接口连接的计算实例.【期刊名称】《常州工学院学报》【年(卷),期】2018(031)002【总页数】6页(P42-47)【关键词】DDR;高速总线;建立时间;保持时间;时序分析【作者】韩玉涛【作者单位】瑞为信息技术有限公司,广东深圳518000【正文语种】中文【中图分类】TN41随着处理器处理能力的快速提高,以及通信系统和图像处理等领域对数据高容量存储、大吞吐量传输的要求,DDR、DDR2以及DDR3 DRAM存储器得到了越来越广泛的应用。

这些存储器的工作频率都在100 MHz以上,高的可达1 GHz,这使得系统设计中的总线时序问题变得十分突出。

如果在系统设计中芯片的时序要求得不到满足,轻则会导致系统出现误码,处理能力降低,运行不稳定,严重的甚至会导致系统不能启动。

本文阐述高速数字总线的模型及时序分析方法,并给出SMP8634DDR多媒体处理器与DDR DRAM连接的计算实例。

1 高速总线模型高速总线模型如图1所示,U1和U2是两个在同一时钟CLOCK下工作的芯片,U1输出数据到U2。

图1 高速总线模型当U1输出数据时,U1在时钟上升沿后输出数据,然后输入芯片U2会在下一个时钟的上升沿去锁存数据总线上的数据,从上升沿到数据在数据总线上有效的时间称为时钟到数据的延时tCO。

图2表明了这种总线的时序关系。

图2 总线时序图tCLK:时钟CLOCK的周期。

tCO:芯片U1输出数据时,从时钟上升沿开始到数据出现在数据总线上的时间,此数据需要用到最大值tCOmax及最小值tCOmin。

tSU:芯片数据作为输入时,数据所需的建立时间(时钟上升沿前数据维持的时间),建立时间永远以最小值来计算。

PCI Express——高速串行互联接口标准

实现 P I x rs 接 H的 难点 C E p es

采用 定 制 逻 辑 在 专 用 产 品 中 实 现 P I x C — E

一

个 通 路 。 发 送 和 接 收 通 道 使 用 低 电 压 差 分

rs 接 信 号 (VDS标 准 传 输 数 据 。 据 时 钟 嵌 入 在 pe s 口 有 很 多 难 点 : L ) 数

品 在 可 能 经 受 的 工 作 电压 和 温 度 ( V 变 化 P T)

范围内有 可靠 的性能表现 。

・ 用 性 :P x rs 接 I经 常 用 于 连 通 CI pes : E 1

ห้องสมุดไป่ตู้

接不 同的半导体器件 。因此 ,该协 议的产品

维普资讯

有标准 的新标准 。

・

P I x rs 的 高 级 特 性 包 括 : C pes E ・ 动 功 耗 管 理 主 在 P I x rs 中 , 管 总 线 上 是 否 有 信 C pes E 不

系统 性 能 :由 于 P x rs 链 路 的 预 CI pes E

bs 时序 裕量 号 传 送 ,总 线 接 口总 是 一 直 在 工 作 。 空 闲状 期数据速 率在 G p 范 围内,因此 , 实现 任何 P I x rs接 I都 必须 C pe s : E 1 态 下 ,总线 上没有任何操 作时 ,这样会导 致 非常 紧张 。 图 1 CI x rs 链 很高 的功耗 。为降低功耗 ,P I x rs提 供 满足 系统 严格的性能要 求。 P pe s E C pes E 路 ・可靠性 :要实现 这一协 议必 须保证 产

P I x rs是 从 P I 展 而 来 的 一 种 系 C pe s E C发 统 互联 接 口标 准 。 P I P I 都 是 基 于 3 C 和 C— x 2

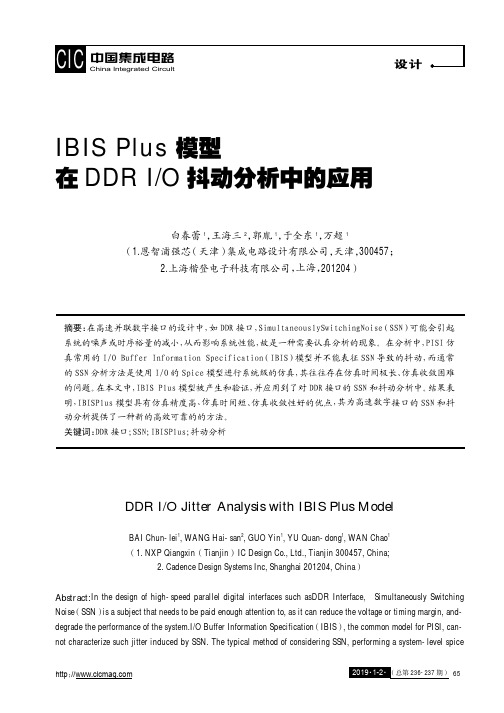

IBISPlus模型在DDRIO抖动分析中的应用

Abstract:In the design of high-speed parallel digital interfaces such asDDR Interface, Simultaneously Switching Noise(SSN)is a subject that needs to be paid enough attention to, as it can reduce the voltage or timing margin, anddegrade the performance of the system.I/O Buffer Information Specification(IBIS), the common model for PISI, cannot characterize such jitter induced by SSN. The typical method of considering SSN, performing a system-level spice

如图 1,同步开关噪声(Simultaneously Switching Noise,SSN)是指多个 I/O 同时动作,在电源上造成 的较大的电压噪声,其可能对系统性能造成影响,在 并联接口系统中更为严重,所以 SSN 及其给系统带 来的影响在设计中应该仔细考察[2]。

图 1 SSN 示意图

通常对系统的信号完整性(SI)仿真是采用 I/O 的输入 / 输出缓冲单元标准 (I/O Buffer Information Specification, IBIS)模型来进行的,此类模型并不能 表征 SSN 带来的抖动。另外,SSN 的仿真通常采用 I/O 的 Spice 模型来进行,此种方法需要的仿真时间 很长,而且极易出现难以解决的收敛性问题。

xc7vx690t使用中发现的BUG分析和测试过程

xc7vx690t使用中发现的BUG分析和测试过程

大神召唤

vivado2017.2一个工程下,两个互不相干的模块会相互影响,只有屏蔽其中一个另一个才能正常工作。

使用此芯片第一次发现如此诡异现象,现在依然没有找到根本原因,只找到了规避方法,各路大神如果有相关经验或者建议请小窗告知,感激不尽!

问题现象

工程中有一个串口通信模块,多个Aurora模块。

其中一个Aurora模块和串口模块有冲突,不能同时出现,否则串口可以正常使用,但是Aurora不能正常工作,表现为channel up 始终为低,输入时钟锁不定,locked信号一直为低。

当没有串口模块的时候所有Aurora模块都正常,硬件上也查看了时钟,完全正常,所以排除外部时钟问题。

时序报告里面没有任何告警,时序裕量大于0,而且串口是低速,高速接口是时钟锁不定,和时序也不应该有关系。

分析和测试过程

首先屏蔽了串口模块后可以正常,可以说明是串口模块里面某个部分影响到了Aurora。

可以采用如下策略,先屏蔽一半代码,如果没有复现问题说明,影响因素在屏蔽的代码里面,反之亦然。

通过这种类似二分法的方法,最终发现主要是串口里面的VIO的影响,屏蔽VIO后串口和Aurora都正常。

由于VIO控制的信号和Aurora根本没有任何联系,所以打开了布局布线图查看了二者的分布情况,示意图如下:

红色底是Aurora的分布范围,白色的是串口模块,被Aurora包围了。

尝试了一下手动布局让串口模块和Aurora不产生交叉,变成了下图所示:。

芯片设计中的高速信号完整性优化方法是什么

芯片设计中的高速信号完整性优化方法是什么在当今的科技时代,芯片作为各种电子设备的核心组件,其性能和稳定性至关重要。

而在芯片设计中,高速信号完整性是一个关键的考量因素。

高速信号完整性优化方法的目的是确保信号在芯片内部和外部传输时,能够保持准确、稳定且无失真,从而保证芯片的正常工作和高性能表现。

要理解高速信号完整性优化方法,首先得明白什么是高速信号完整性问题。

当信号在芯片内以极高的速度传输时,可能会出现信号反射、串扰、衰减、时序偏差等问题。

这些问题会导致信号质量下降,进而影响芯片的功能和性能。

那么,有哪些方法可以用来优化高速信号完整性呢?一个重要的方法是合理的布线规划。

布线就像是芯片内部的“道路”,如果道路规划不合理,就会导致交通拥堵(信号传输问题)。

在布线时,要考虑线宽、线间距、走线长度等因素。

较宽的线可以降低电阻,减少信号衰减;合适的线间距可以降低串扰。

同时,尽量缩短走线长度,减少信号传输的延迟。

电源和地的规划也是关键的一环。

稳定的电源供应对于芯片的正常工作至关重要。

为了减少电源噪声和地弹,需要采用良好的电源和地平面设计。

通过合理布局电源和地的网络,提供低阻抗的路径,可以有效地降低电源噪声对信号的影响。

终端匹配是解决信号反射问题的常用手段。

当信号在传输线上遇到阻抗不连续时,就会发生反射。

通过在传输线的终端添加合适的电阻,使其阻抗与传输线的特性阻抗匹配,可以减少反射,提高信号质量。

在芯片设计中,还需要考虑电磁兼容(EMC)问题。

电磁干扰可能会影响高速信号的完整性。

采用屏蔽措施、合理的布局以及滤波技术等,可以减少电磁干扰,保障信号的稳定传输。

另外,对芯片进行仿真分析也是优化高速信号完整性的重要步骤。

在设计阶段,通过使用专业的仿真软件,可以模拟信号在芯片中的传输情况,提前发现可能存在的问题,并进行针对性的优化。

同时,选择合适的封装技术也能对高速信号完整性产生影响。

不同的封装类型具有不同的寄生参数,如电感、电容等。

总线时序分析方法

Figure: 5 SDRAM 控制器时序指标

பைடு நூலகம்

Figure: 6 时钟芯片技术指标

3.1 外部时钟源统一提供时钟工作方式

这种 SDRAM 的工作方式如下图所示:

SDRAM Controller

Data Bus

SDRAM

Cloc k1 133MHz

Cloc k2 133MHz

Tskew = 150 ps = 0.15ns

另外由于这个 150ps 的 Skew,其实我们并不能确定到底是哪个时钟输出是提前了,或是落 后了,因此我们必须从最坏的情况去考虑,那么 Tskew 就变为:

Tskew = ±0.15ns

从 SDRAM 控制器时序指标表格中可以得到控制器数据总线的输出延迟(Output Delay)最 小是 1.2ns,最大是 3.8ns,即:

从上面的式子,我们可以得出一个重要结论: l 如果电路板在输入的建立时间方面发生问题,我们可以通过降低芯片的运行频率(增

大 Tclk)来满足所需的建立时间的要求。 从输入的 Th 考虑:

Tco min > Th

从上面的式子我们可以推算出输入保持时间的时序裕量:

HoldTimeM arg in = Tco(min) − Th ――――――――――(2)

这两个公式为 PCB 的布线计算提供理论的依据。在 Cadence 的 SPECCTRAQuest 的时 序分析模型,就是根据这两个公式来计算。

以上基本公式考虑了 Tskew,Tjitter,Tcrosstalk 对时序裕量的影响。这些信号在很多情 况下是以正负的指标来表明在一定范围内的漂移,由于设计者无法预测这些指标是带来正的 影响还是负的影响,因此以下定义取正负号的原则: 1. 在计算公式 1 中,也就是计算机最长布线时,这些指标所取的正负号应该使布线长度值

mux优化时序的方法

mux优化时序的方法对于MUX的时序优化,可以采取以下一些方法来实现:1. 减少MUX的输入数量:根据MUX的功能需求,尽量减少MUX的输入数量。

如果可能的话,可以对输入信号进行合并或者重新设计逻辑电路,以减少MUX的输入端口数量。

2. 使用级联MUX:如果MUX的输入数量仍然很大,可以考虑将多个MUX级联在一起,以减少每个MUX的输入端口数量。

这样可以将原来的复杂MUX分解为多个简单MUX的级联组合。

3. 时钟同步MUX:如果MUX的输入信号来自不同的时钟域,那么可以考虑在输入端进行时钟同步,避免由于时钟差异而产生的时序问题。

可以使用合适的时钟同步电路,例如寄存器、同步FIFO等。

4. 编码器代替MUX:对于特定的应用场景,可以考虑使用编码器来替代MUX。

编码器可以将输入信号进行编码,并生成对应的输出选择信号,从而减少MUX的输入端口数量。

5. 管理MUX的输入负载:当MUX的输入信号连接到较长的线路上时,应注意输入负载对时序性能的影响。

可以采取有效的线路驱动方案,例如增加驱动器的驱动能力、降低线路的RC延迟等,以保证MUX输入信号的快速传输。

6. 优化布线布局:在电路布局设计中,合理的位置布置MUX和其输入信号,可以最大程度地减少信号传输的延迟和时序问题。

可以使用布线规则和布局约束,将相关的信号线尽量靠近MUX,并最小化相关信号线的长度和功耗。

总之,MUX的时序优化主要是通过减少MUX的输入数量、进行时钟同步、采用级联MUX、使用编码器、管理输入负载和优化布线布局等方法来实现。

可以根据具体的应用场景和需求,选择合适的优化方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

优化高速接口的时序裕量过去十年中,高速数字总线已经获得了令人瞩目的发展,它们不仅比以往更快,而且还正在改变系统定时数据的方式。

为提高数据吞吐量,新兴的同步数字总线可以通过一套定时机制在每个时钟周期内多次发送数据。

本文将对源同步定时如何优化高速接口时序裕量进行讨论。

时序预算是对系统正常工作所需时序参数或时序要求的计算。

为了使同步系统正常工作,其时序需求必须在一个时钟周期内满足。

对时序的预算涉及到许多因素,包括对保持时间和最大工作频率的要求。

通过时序预算,可以发现传统定时方法的局限性。

图1显示了一个标准定时系统。

在该图中,一个存储器控制器与一个SRAM连接。

SRAM和存储器控制器都从同一个时钟源接收时钟信号。

假设这里有意使时钟信号电路与电路延迟相匹配,相关时序参数如下(图2):存储器控制器tSU(建立时间)、存储器控制器tH(保持时间)、主板电路tPD(传输延迟)、SRAM tCO(时钟到输出的延迟)、SRAM tDOH(输出数据的保持时间)、时钟发生器tSKEW(时钟偏移)、时钟发生器tJIT(周期抖动)以及时钟发生器tCYC(周期时间)。

如果考虑最坏情况下的输入建立时间、时钟到输出的延迟、传输延迟、时钟偏移和时钟抖动,通过计算最高频率就可以得到系统的最小周期时间。

最高频率计算如下:tCO(max, SRAM) + tPD(max) + tSU(max, CTRL) + tSKEW(max, CLK) + tJIT(max, CLK) < tCYC通过计算保持时间可发现系统输出数据太快,影响了系统接收器件的输入保持时间。

这样,最坏情况将发生在数据最早输出的时候。

计算公式如下:tCO(min, SRAM) + tPD(min) - tSKEW(min, CLK) - tJIT(min, CLK) > tH(max, CTRL)现在让我们假设SRAM和存储器控制器的时序参数值为:tSU=0.5ns;tH=0.4ns;tCO=0.45ns;tDOH*=-0.45ns;tSKEW=±0.2ns;tJIT=±0.2ns。

在这种情况下,我们将使用带有双倍数据速率(DDR)接口的高速SRAM,SRAM在每个时钟的上升沿和下降沿驱动数据。

*tDOH < 0意味着在下一个时钟上升沿/下降沿前数据已变得无效。

所需的最小保持时间计算如下:tDOH + tPD - tSKEW - tJIT > tH-0.45 ns + tPD - 0.2 ns - 0.2 ns > 0.4 ns-0.85ns + tPD > 0.4 nstPD > 1.25 ns假设FR4电路板上走线的传输延迟为160ps/英寸。

SRAM到存储器控制器的走线长度至少有7.82 in。

tPD取1.2ns,最大工作频率可计算如下。

因为SRAM有一个DDR接口,所以时序预算是基于半个时钟周期:tCO + tPD + tSU + tSKEW + tJIT < tCYC/20.45ns+1.25ns+0.5ns+0.2ns+0.2ns2.6ns5.2ns192MHz>fCYC在FR4电路板上走线的长度为7.82英寸和典型时序参数的前提下,可满足工作频率可高达192MHz时的时序预算要求。

对于那些板空间有限的系统,7.82英寸的最小走向长度约束就成了系统难以满足的一个要求。

如果无法增加走线延迟,那么通过使用延迟锁定环/锁相环(DLL/PLL)对时钟信号进行移相以更早地捕获数据,存储器控制器可以满足保持时间的要求(图3)。

存储器控制器将必须用系统时钟信号来重新同步捕获的数据。

使用这个方法将会引入额外的PLL/DLL抖动,这会降低系统的最大工作频率。

有了这个附加的PLL延迟后,所需的最小保持时间就变为:tDOH + tPD(trace) + tPLL/DLL_DELAY - tSKEW - tJIT > tHtCO + tPD + tSU + tSKEW + tJIT + tJIT_PLL/DLL < tCYC/2其中,tJIT_PLL/DLL是由PLL引入的延迟。

即使使用最快的SRAM和ASIC/FPGA,时钟偏移、时钟抖动和电路传输延迟也会很明显地限制系统性能。

如前所述,如果使用FR4电路板,走线延迟约为160ps/英寸。

鉴于很高频率下数据有效窗口已变为2ns(例如对250MHz的DDR器件而言)甚至更小,这个数字是非常重要的。

时钟信号之间的偏移也会显著减小时序裕量。

我们将会看到源同步时钟可以明显减少传输延迟、偏移和抖动,使时序收敛更容易达到。

源同步定时的优点在典型的源同步处理中,与每个数据字相关联的时钟上升沿被发送出来(DDR存储器每个时钟周期可能有多个数据),接收器件使用这个时钟上升沿来锁存数据,然后再将数据与主时钟或公用时钟同步。

由同一个器件对时钟信号和数据/控制信号进行同步后传送,实际上就消除了主板电路信号相对时钟信号的传输延迟。

但是采用源同步定时就需要考虑不同的主板布线。

在一个带有独立时钟发生器的系统中,该时钟发生器为多个器件提供时钟信号,首要的问题是电路长度的设计应使所有的时钟沿同时到达器件,这可能需要延长连接时钟发生器旁边器件的走线长度。

采用源同步的方法,主要的问题是通过匹配输出时钟和数据信号的走线长度来保持时钟和数据之间的相位对准。

如果走线正确匹配,相对时钟信号的数据传输延迟就不复存在了。

有很多种方法可以实现源同步定时:1)源同步时钟信号的上升沿对准到数据有效窗口的起始点。

诸如QDR-II/DDR-II SRAM这样的大多数DDR存储器采用了这种方法,存储器将时钟信号和数据都发送到接收器。

本文中将以它们作为例子进行讨论。

2)QDR-II产生一对输出时钟信号CQ和/CQ,理想情况下它们之间的相位差为180°,接收器利用这两个时钟信号的上升沿来锁存数据。

在两个存储器中,接收器都必须将此时钟信号延迟以满足其捕获数据所需要的建立和保持时间。

此延迟可以通过片上延迟模块来实现,具体可以在接收端使用PLL或DLL,或采用板上走线延迟的方法。

这两种方法因具有频率转移能力而在FPGA设计中受到青睐。

为在更高频率上使用同样的设计,可以修改FPGA代码以改变由PLL/DLL引入的延迟。

另外,ASIC总是运行在一个特定的频率,ASIC通常会选用板上走线延迟的方法。

也有一些源同步时钟实现方案,在源端将其源同步时钟信号延迟,在数据有效窗口的中心对齐。

在这种情况下,用户可以直接实现源同步时钟信号来锁存接收器的数据(假设时钟和数据之间的走线匹配)。

抖动的影响抖动可以被定义为时钟位转换与理想时序偏离,时钟位转换可能超前或滞后,这里有多种不同类型的抖动。

周期间抖动是时钟输出位转换中与前一个周期相应位置的偏离(参见图2)。

周期抖动用来衡量时钟输出位转换与理想时序的最大偏离。

长期抖动用来衡量在多个周期的时钟输出位转换中与理想时序的最大偏离,这里的“多个周期”的具体数目取决于具体的应用和工作频率(图4)。

根据具体的应用,在时序预算中应考虑其中一种或所有三种类型的抖动。

在同步定时环境中,产生输入时钟的时钟源或PLL/DLL一般会引起抖动变化。

在时序预算中考虑了抖动因素后,抖动(tJIT)就会显著地缩小时序裕量,特别在高频率下。

但是,如果在接收端时钟和数据存在相同的抖动,就可以从时序预算中除去抖动成分(tJIT)。

采用源同步时钟的情况下也是如此,这是时钟信号和数据由同一个发射器件驱动并一直保持对准。

将时钟设计得像其中一个输出时,通常就会产生这样的效果。

虽然仍必须考虑时钟和数据管脚之间时钟到输出的时间变化,但这个参数一般都在±100ps左右。

在某些应用中,源同步时钟被延迟1个周期以上以锁存数据。

这种情况下,时序预算中要考虑长期抖动,这将使时序裕量减小。

这种抖动也被称为N周期抖动,N是相对于数据信号,源同步时钟信号被延迟的周期数。

当然,一般不建议将源同步时钟信号延迟一个周期以上。

时序预算的计算从下面的例子中可以看出,从时序预算中消除传输延迟可以大大改善系统时序裕量。

图5给出了采用源同步时钟的SRAM的例子。

让我们按下面步聚计算时序预算。

按照设计,SRAM输出时钟信号的上升沿与数据有效窗口的起始边对准。

我们假设存储器控制器通过PLL/DLL片上延迟时钟延迟以满足建立和保持时间。

SRAM和存储器控制器采用相同的时序参数。

假设时钟和数据走线长度匹配,计算时序预算时就可以忽略电路传输延迟tPD。

另外,时钟与数据具有同样的偏移和抖动(不包括管脚之间±100 ps的偏移),因此无需再考虑时钟发生器抖动和偏移(tSKEW, tJIT)。

在这个系统中,需要考虑的另外一个参数是SRAM的tJIT:相对于数据的SRAM输出源同步时钟抖动。

这可能是由管脚间时钟到输出的时间变化而引起的。

在这个例子中,我们假设时钟和数据走线匹配地很好。

如果由于电路设计而导致走线长度出现差异,就必须考虑时钟和数据信号走线长度的差异。

如果时钟信号的走线是有意延长以延迟时钟信号(将时钟信号与数据有效窗口中心对准),就不用考虑此参数。

假设SRAM源同步时钟抖动为tJIT=±0.2ns,我们可以像表中列出的那样逐步计算最小周期时间(参见表)。

要获得非负值裕量,应满足如下条件:tM>0tCYC/2-2.2ns>0tCYC/2>2.2nstCYC>4.4nsfCYC<227MHz本例采用源同步时钟信号,满足建立和保持时间要求,对数据信号走线长度也没有什么约束。

计算得到的最大工作频率是277MHz,比传统时钟同步方法提高了35MHz。

注意本例中主要的频率限制因素是控制器的建立和保持时间。

使用源同步时钟的最优方法为最好地利用源同步时钟,设计工程师应注意以下要点:不要使源同步时钟的延迟时间超过一个周期。

源同步时钟的上升沿与其所驱动的数据信号是严格匹配的,所以时钟和数据信号应具有同样的抖动并互相抵消。

如果将源同步时钟信号的上升沿延迟到下一个周期以锁存数据,那么就必须考虑另外一个抖动成分,即N周期抖动,N是相对于数据信号,时钟信号被延迟的周期数。

图6和图7中给出了使用源同步时钟的推荐方法和不推荐方法。

这些例子采用QDR-II源同步时钟(CQ和/CQ)。

注意:如果有两个源同步时钟,最好两个都用到。

作者:Kannan Srinivasagam,David Mahashin,Cypress Semiconductor。