AD7656型模数转换器在信号采集系统中的应用

基于labview的stm32串口数据采集系统

云南化工 Yunnan Chemical Technology

doi:10.3969/j.issn.1004-275X.2019.012.071

Dec.2019 Vol.46,No.12

基于 labview 的 STM32 串口数据采集系统

欧姗姗 1袁 徐 飞 1袁 宋 楠 1袁 冯旭东 1袁 李国玮 2

Ou Shanshan1,Xu Fei1,Song Nan1,Feng Xudong1,Li Guowei2 (1.Xi’an Petroleum University, Shaanxi Xi’an 710065;

2. China Petroleum logging Group Co., Ltd., Xi’an, Shaanxi 710065)

Key words: labview;Serial port acquisition;STM32

针对现代钻井新技术对随钻数据传输及其信 息处理的要求袁 对井下声波无线遥测系统信号采 集与处理进行基础理论研究袁 对于井下传输到地 面的信号特征进行分析袁 设计了声波无线遥测地 面系统的信号处理机制遥

1 系统总体设计方案

6冤 解调则是 把加 载在 声波 信号 上的 井下 信 息分离出来袁 得到有用信息遥 3.2 软件面板

如图 4 所示波形图为数据波形显示模块遥

图 2 软件设计流程图

串行通信是工业现场仪器或设备常用的通信 方式袁 早期的仪器单片机等均使用串口与计算机 进行通信遥 上位机软件的整体设计思路如图 3 所 示遥

地面系统的硬件部分主要由放大滤波电路袁 AD 采集电路以及上位机部分组成遥 当载有井下 信息的声波信号随着钻杆传输到地面之后袁 地面 系统首先用传感器获取到井下声波信号袁 再通过 放大滤波电路袁 对信号进行初步的放大滤除干 扰袁 将干扰信号滤除之后袁 交给地面的主控芯片 STM32袁 STM32 控 制 AD7656 对 信 号 进 行 采 集 袁 将井下传输上来的模拟信号转换成了数字信号袁 通过 SPI 通信袁 把这个数字信号交给 STM32袁 利 用 labview 的 VISA 库 函 数 袁 设 计 对 应 的 串 口 通 信袁 配合下位机的 AD 采集模块袁 把井下的信号 传输给上位机进行显示遥 系统方案如图 1 所示遥

(完整word版)AD7656中文资料

AD7656—16位同步采样双极ADC转换器功能:6路独立的16位AD6路真双极模拟量输入引脚/软件可选择的范围:±10V,±5V快速通过率250KSPS指定Vcc为4.5V~5.5V低功耗以5V 供应250 kSPS的160 mW宽的输入带宽: 输入频率为100kHz时信噪比为85dB在片参考和参考缓冲器并行和串行接口高速串行接口SPI/ QSPI/μWire/DSP可兼容无流水线延迟备用模式:最大0.5μA64LQFP封装应用电力线检测系统仪器和控制系统多轴定位系统一般描述AD7656芯片包含6路16位快速、低功耗、逐步逼近ADC。

元件工作电源4.5V~5.5V,具有250kSPS通过率特性。

元件具有低噪音、宽带宽跟踪保持放大器,能够操作输入频率达到8MHz。

转换过程和数据采集由 CONVST 信号和一个内部振荡器控制。

三个CONVST引脚允许三对ADC独立的同时采样。

AD7656具有高速的并行和串行接口,可以与微处理器和DSP接口。

AD7656具有菊花链特性,允许多个ADC与一个串行接口连接。

元件没有流水线延迟。

AD7656在±10V范围内能提供真双极的输入信号。

AD7656包含一个2.5V内部参考电压,也能采用一个外部考电压,如果V REF引脚供应一个3V外部叁考电压, ADC能供给真双极±12V模拟量输入范围。

参照这±12V输入范围,需要给V DD和V SS提供±12V电压。

产品特点1 6路16位250kSPS ADC2 6路真双极高阻抗模拟量输入3 具有一个并行和一个高速串行接口。

引脚功能描述术语积分非线性这是从一条直线横传过ADC传递函数终点的最大的偏差。

传递函数终点是零刻度时,1/2LSB点低于最初代码转换,是满刻度时,1/2LSB点超出最后代码转换。

差分非线性这是一个在ADC转换中任何两个邻近代码的LSB转换的测量值与理论值差。

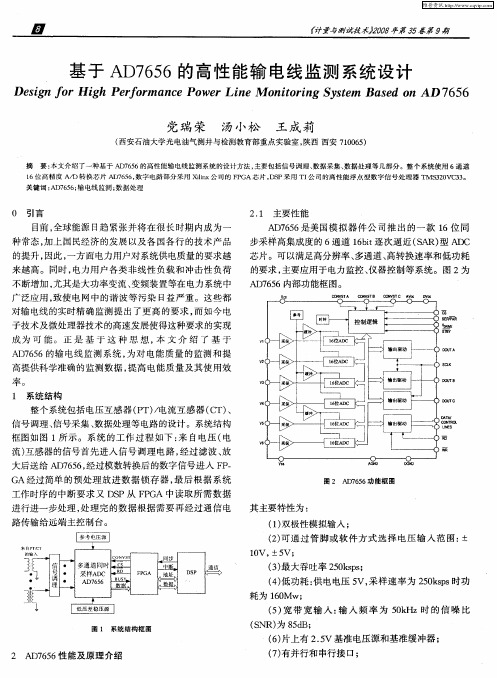

基于AD7656的高性能输电线监测系统设计

如 图 4所示 。

一 肋一

2 2 工 作 原理 .

A 6 6是高 速 低 功 耗 、 许 6路 同 时 采 样 的逐 次 D75 允

逼 近式 AD 包 括 1个 比较 器 、 C, 1个 模 傲 转 换器 、 1个 逐

次逼近寄存器 (

) 1 和 个逻辑控制单元 。转换 中的逐

( NR) 8 d S 为 5 B;

() 6片上有 25 .V基准电压源和基准缓冲器 ;

2 6 75 L 6 6性 能及原 理 介绍 D

() 7有并 行 和 串行 接 口;

维普资讯

党瑞 蒙等 : 基 AD75 6 6的 高性 能输 电 线 监 灏 系统 设 计

的要求 , 主要应 用于 电力监 控 、 器控 制 等系 统 。 图 2为 仪

A) 6 6内部功 能框 图 。 1 5 7

对 输 电线 的实 时精 确 监测 提 出 了更 高 的要 求 , 如 今 电 而 子技 术及微 处 理器技 术 的高速 发 展使得 这种要 求 的实现

成 为 可 能 。正 是 基 于 这 种 思 想 , 文 介 绍 了 基 于 本

框 图如 图 l所 示 。系 统 的 工 作 过 程 如 下 : 自电压 ( 来 电

流) 互感器的信号首先进入信号调理 电路 , 经过滤波 、 放

大 后送 给 A 7 5 , D 66 经过 模数 转换后 的数 字信 号进 入 F — P

∞

一

一

^

一 一

B C

日

三

G A经过简单 的预处理放进数据锁存器 , 最后 根据 系统

维普资讯

《 计量与瓤试技 本 O 8年 第 3 o 5巷第 9期

基于SAR-ADC的精密同步数据采集系统设计

基于SAR-ADC的精密同步数据采集系统设计王炳文【摘要】For the problem of simultaneously sampling of multi-channel analog signals in a data acquiring system, the schemes of the system were discussed.Based on SAR-ADC, a kind of 16 bit AD convert system which controlled by FPGA was designed.The system could realize real-time synchronous sampling of analog signals.And the differences of sampling rate among multi-channel analog signals were well balanced in this system.The Signal to Noise and Distortion Ratio(SINAD) and Effective Number of Bits(ENOB) of the system were tested, and it was proved that the system can achieve good AC characters.%针对某精密数据采集系统中模拟信号同步采样问题,文章研究了多通道同步模拟信号采集方法,设计了一种基于SAR-ADC、使用FPGA控制的16位同步采样AD转换系统.该系统可实现模拟信号的实时同步采样,同时兼顾多路模拟信号采样频率要求的差异性,最后通过试验测试了该系统的信纳比(SINAD)和有效位数(ENOB).测试结果表明,该系统具有良好的动态性能指标.【期刊名称】《微型机与应用》【年(卷),期】2017(036)007【总页数】4页(P29-31,34)【关键词】SAR-ADC;同步采样;FPGA【作者】王炳文【作者单位】中国航空工业集团公司西安航空计算技术研究所,陕西西安 710065【正文语种】中文【中图分类】TP353在惯性测量[1]、功率因数校正[2]、电机控制等工业应用场合,系统需要采集同一时刻来自多个传感器的模拟信号,并根据当前的状态进行计算和控制。

基于TMS320F28335的采集板卡设计

基于 TMS320F28335的采集板卡设计摘要:针对生产企业对工业设备的运行过程中的电压、电流、控制指令等参数的采集监控需求,本文设计了一款基于TMS320F28335的采集板卡,该板块具备多路采样电路,宽幅度的采集电压输入范围。

经验证,该板卡的性能功能均能满足设计要求。

关键词:板块;通信;A/D采集1引言国家智能制造2025战略对传统的制造业提出了更高的要求,为了提高设备利用率以及生产效率,越来越多的制造企业在设备运行的过程中加强对机器的运行电压、电流、控制信号等信息进行采集,实时监测设备的运行状态,收集设备的工作信息并进行分析做出生产调整决策。

同时也通过分析设备的长期运行参数进行设备故障预测,及时的对设备的进行检修,更换备件。

特别是针对老设备的改造,老设备一般不具备电流、电压、控制指令等的采集功能,需要对老设备进行改造升级,满足设备监控的要求。

基于以上原因,本文针对工业设备信息采集的需求,采用TI公司的TMS320F28335主控芯片设计了一款多路、宽电压采集板卡,并经试验验证,该板卡的功能性能能够满足要求。

2采集板卡的系统设计方案2.1系统整体方案采集板卡包含DSP最小系统电路、电源电路、采样信号调理电路、A/D采样电路、通信电路,具有最大可扩展48路电压采集功能。

通过调节信号调理电路的分压电阻输入采样电压范围可达为0~230V,测量精度不小于2%FS。

DSP主控芯片采用TI公司开发的TMS320F28332具有150MHz的高速处理能力32位浮点处理单元。

2.2系统的工作原理板卡的输入电压为DC5V,功率不大于0.5W,工作时将输入采集板卡的电压、电流、控制信号等进行调理、隔离变换后,输入至AD转换电路转变为数字信号送至DSP的数据总线,经DSP处理后经RS422通信对外输出。

2.3电路设计2.3.1板卡电源变换电路电源电路设计采用如下方案,采集板卡的输入电压为DC5V,经线性电源芯片AMS1117变换后变成3.3V系统数字电源供片内Flash编程使用。

AD7656

2 AD7656的特性及引脚功能2.1 AD7656的特性图1示出AD7656的功能框图。

AD7656的主要特性如下:●6通道16-bit逐次逼近型ADC;●最大吞吐率为250kS/s;●A Vcc范围为4.75V-5.25V;●低功耗:在供电电压为5V、采样速率为250kS/s时的功耗为160mW;●宽带宽输入:输入频率为50kHz时的信噪比(SNR)为85dB;●片上有2.5V基准电压源和基准缓冲器;●有并行和串行接口;●与SPI/QSPI/μWire/DSP兼容的高速串行接口;●可通过引脚或软件方式设定输入电压范围(±10V,±5V);●采用iCMOS工艺技术;●64引脚QFP。

2.2 AD7656的引脚功能REFCAPA、REFCAPB、REFCAPC是参考电压引脚,这几个引脚应该接去耦电容器来减小每1个ADC 通道参考缓冲器的衰减。

V1一V6是模拟输入1-6引脚,它们是模拟前端输入,对应通道的输入范围取决于RANGE引脚的定义。

AGND是模拟地,所有的模拟输入信号和外部参考信号都要用AGND。

DVcc是5V数字电源端。

VDRIVE是逻辑电源输入,该引脚的电压取决于内部参考电压,应接10μF或100μF的去耦电容器。

DGND是数字地,它是数字电路的参考点。

A Vcc是模拟电压输入(4.5V-5.5V),它只给ADC的内核供电。

CONVSTA/B/C是转换使能逻辑输入,每对有其相关的CONVST信号,用来启动每对或每4个或6个ADC同步采样。

CS是片选信号,逻辑低电平时使能。

RD是读信号,逻辑低电平时使能。

WR/PEFEN/DIS是写数据/参考使能/非使能。

BUSY是忙信号输出,当转换开始时为高电平,并且在转换结束前一直为高电平。

SER/PAR是串行/并行选择输入信号。

低电平时选择并行接口模式,高电平时选择串行接口模式。

DB[0]/SEL A是数据0位/选择输出A路。

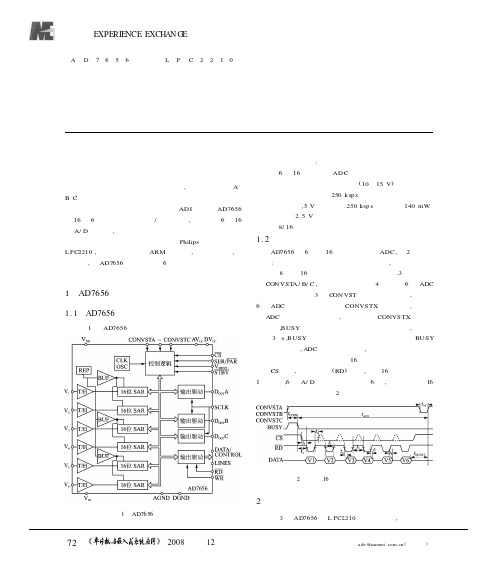

AD7656与LPC2210的并行采集接口设计

经验交流EXPERIENCE EXCHAN GEAD7656与L P C 2210的并行采集接口设计■河北大学 常铁原王欣 卢冬冬引 言在电力系统三相信号处理应用中,常需要同时对A 、B 、C 三相电压和电流信号进行数据采集和处理。

如三相功率、电能测量及谐波分析等。

美国AD I 公司的AD7656是16位6通道同时采样的模/数转换器,内部含有6个16位A/D 转换器,具有转换精度高、速度快、功耗低、输入模拟信号幅度大、信噪比高等特点。

Philips 公司出品的L PC 2210,是一款工业级的ARM 控制器,处理速度快,性能稳定,与AD7656共同组成的6通道数据采集系统能在很大程度上提高系统的信号采集和处理能力。

1 AD7656的特点及工作原理1.1 AD7656的特点图1为AD7656的内部功能框图。

图1AD7656内部功能框图其主要特性为:◆6个16位独立的AD C 通道。

◆输入模拟信号的范围为±(10~15V )。

◆最大转换速率为250k sp s 。

◆低功耗,5V 供电时在250ksp s 下功耗为140mW 。

◆片上2.5V参考电压和参考缓冲器。

◆8/16位并行接口模式和串行接口模式。

1.2 工作原理AD7656是6通道16位逐次逼近型ADC ,有2种接口模式:串行接口模式和高速的并行接口模式,并行接口模式又分为8位和16位传送方式。

在数据转换时,3个转换信号CON VST A /B/C ,用来控制每对或每4个或每6个ADC 同时采样。

如果将3个C ON VST 引脚连接在一起,就可对6个ADC 同时进行采样。

在CONVSTX 的上升沿,被选择的ADC 对被置为保持模式,转换开始。

CONVSTX 的上升沿过后,BUSY 信号变为高电平表明转换正在进行,转换时间是3μs ,BUSY 信号返回低电平表明转换结束。

在BU SY 信号的下降沿,ADC 回到跟踪模式,数据可以通过并行或串行接口从输出寄存器读出。

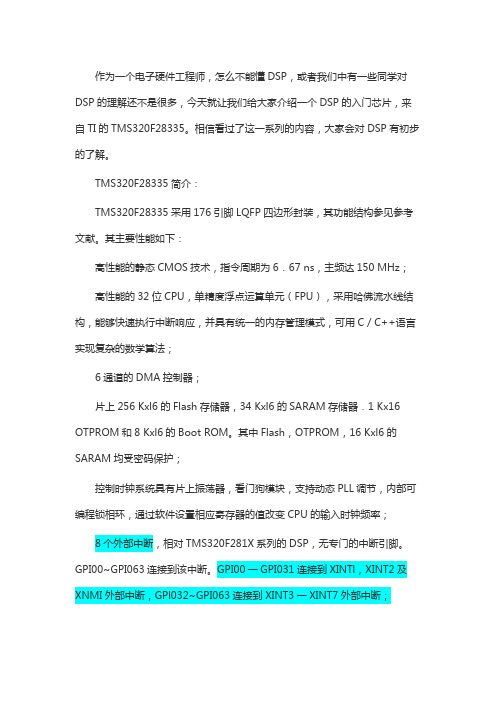

25_TI DSP入门芯片TMS320F28335

作为一个电子硬件工程师,怎么不能懂DSP,或者我们中有一些同学对DSP的理解还不是很多,今天就让我们给大家介绍一个DSP的入门芯片,来自TI的TMS320F28335。

相信看过了这一系列的内容,大家会对DSP有初步的了解。

TMS320F28335简介:TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要:首先介绍一种新型的多通道高分辨率AD7656型模,数转换器的功能和性能,详细描述它在并行接口模式下的工作方式和原理。

然后介绍AD7656在信号采集系统中的应用,给出设计方案和电路。

关键词:ADC;AD7656;信号采集;应用1 引言美国模拟器件公司(ADI)发布了一种创新的半导体制造工艺,这种工艺技术是将高电压半导体工艺与亚微米CMOS和互补双极型工艺相结合,并将该工艺命名为iCMOS(工业CMOS)。

使诸如工厂自动化和过程控制等高电压应用在性能、设计和节省成本方面均得到极大提升。

iCMOS能把更多的信号链路功能集成在一个尺寸比以前小很多的芯片内,并且不牺牲性能,将数字逻辑电路与高速模拟电路集成在一起,并且采用前所未有的小尺寸封装,提供更高的性能和更低的功耗。

AD7656就是采用iC-MOS工艺制造的,是高集成度、6通道16-bit逐次逼近(SAR)型ADC,内含1个2.5V基准电压源和基准缓冲器。

该器件的功耗比最接近的同类双极型ADC降低了60%。

AD7656在每通道250kS/s采样速率下的精度(±4LSB最大值积分线性误差)是同类产品的2倍。

基于iCOMS技术制造的ADC可以满足工业领域对高分辨率、多通道、高转换速率和低功耗的要求。

2 AD7656的特性及引脚功能2.1 AD7656的特性图1示出AD7656的功能框图。

AD7656的主要特性如下:●6通道16-bit逐次逼近型ADC;●最大吞吐率为250kS/s;●AVcc范围为4.75V-5.25V;●低功耗:在供电电压为5V、采样速率为250kS/s时的功耗为160mW;●宽带宽输入:输入频率为50kHz时的信噪比(SNR)为85dB;●片上有2.5V基准电压源和基准缓冲器;●有并行和串行接口;●与SPI/QSPI/μWire/DSP兼容的高速串行接口;●可通过引脚或软件方式设定输入电压范围(±10V,±5V);●采用iCMOS工艺技术;●64引脚QFP。

2.2 AD7656的引脚功能REFCAPA、REFCAPB、REFCAPC是参考电压引脚,这几个引脚应该接去耦电容器来减小每1个ADC通道参考缓冲器的衰减。

V1一V6是模拟输入1-6引脚,它们是模拟前端输入,对应通道的输入范围取决于RANGE 引脚的定义。

AGND是模拟地,所有的模拟输入信号和外部参考信号都要用AGND。

DVcc是5V数字电源端。

VDRIVE是逻辑电源输入,该引脚的电压取决于内部参考电压,应接10μF或100μF的去耦电容器。

DGND是数字地,它是数字电路的参考点。

AVcc是模拟电压输入(4.5V-5.5V),它只给ADC的内核供电。

CONVSTA/B/C是转换使能逻辑输入,每对有其相关的CONVST信号,用来启动每对或每4个或6个ADC同步采样。

CS是片选信号,逻辑低电平时使能。

RD是读信号,逻辑低电平时使能。

WR/PEFEN/DIS是写数据/参考使能/非使能。

BUSY是忙信号输出,当转换开始时为高电平,并且在转换结束前一直为高电平。

SER/PAR是串行/并行选择输入信号。

低电平时选择并行接口模式,高电平时选择串行接口模式。

DB[0]/SEL A是数据0位/选择输出A路。

DB[1]/SEL B是数据1位/选择输出B路。

DB[2]/SEL C是数据2位/选择输出C路。

DB[3]/DCIN C是数据3位,C路为菊花链式。

DB[4]DCIN B是数据4位/B路为菊花链式。

DB[5]/DCIN A是数据5位/A路为菊花链式。

DB[6]/SCLK是数据6位/串行时钟。

DB[7]/HBEN/DCEN是数据7位/高位使能/菊花链式使能。

DB[8]DOUTA是数据8位/串行数据输出A。

DB[9]/DOUTB是数据9位/串行数据输出B。

DB[10]/DOUTC是数据10位/串行数据输出C。

DB[11]/DGND是数据11位/数字地。

DB[12]、DB[13]、DB[15]是数据12位、数据13位、数据15位。

DB [14]/REFBUFEN/DIS是数据14位/参考缓冲使能(低电平时)/非使能(高电平时)。

RESET是复位信号输入。

RANGE是模拟输入范围选择输入信号。

VDO是正电源端。

Vss是负电源端。

H/S SEL是硬件/软件选择输入引脚。

W/B是字或字节模式选择。

3 AD7656的工作原理及系统构成3.1AD7656的工作原理AD7656是逐次逼近型转换器,包括1个比较器、1个模/数转换器、1个逐次逼近寄存器(SAR)和1个逻辑控制单元。

转换中的逐次逼近是按对分原理由控制逻辑电路完成。

其大致过程如下:启动转换后,控制逻辑电路首先把逐次逼近寄存器的最高位置1,其他置0,逐次逼近寄存器的这个内容经过模/数转换后得到约为满量程输出一半的电压值。

这个电压值在比较器中与输入信号进行比较。

比较器的输出反馈到模/数转换器,并在下一次比较前对其进行修正。

在逻辑控制电路的时钟驱动下,逐次逼近寄存器不断进行比较和移位操作,直到完成最低有效位(LSB)的转换。

这时逐次逼近寄存器的各位值均已确定,逐次逼近转换完成。

由于逐次逼近型模/数转换器在1个时钟周期内只能完成1位转换,N位转换需要N个时钟周期,故这种模/数转换器的采样速率不高,输入带宽也较小。

它的优点是原理简单,便于实现,不存在延迟问题.适用于中速率和分辨率较高的应用场合。

AD7656包含1个低噪声、宽带跟踪保持放大器来处理输入频率高达8MHz的信号,还具有高速并行和串行接口,从而允许该器件与微处理器(MPU)或数字信号处理器(DSP)连接。

在串行接口方式下,AD7656能提供菊花链功能,把多个ADC连接到1个串行接口上。

它可以接收双极性输入信号,RANGE引脚和RNG位为下次在±4xVREF-±2xVREF之间转换选择输入范围。

当3个CONVST引脚连接到一起时,允许6个片上ADC同时采样,6个ADC可以被分成3对,每对有1个相关的CONVST信号,用来启动每对或每4个或是全部6个ADC同步采样,CONVSTA用来启动V1和V2的同步采样,CONVSTB对应的是V3和V4,CONVSTC对应的是V5和V6。

跟踪保持放大器可以保证模/数转换器精确地转换满量程输入的正弦波信号,可以保证分辨率为16bit。

跟踪保持放大器的输入带宽比工作在最大吞吐率情况下的ADC的奈奎斯特速率还要大。

AD7656可以处理频率为8MHz的输入信号。

跟踪保持放大器在CONVSTx的上升沿同步采样各自的输入信号。

跟踪保持的典型时间为20ns,这可以使6个ADC同步采样。

AD7656有2种工作模式:串行接口模式和高速的并行接口模式。

本文主要介绍并行接口模式。

并行接口模式以1个字的形式来操作(W/B=0),也可采用字节的形式(W/B=1)。

从并行总线上读数据时,信号SER/PAR应被置低电平。

当CS和RD均为低电平时,数据线DBO-DB15将不再是高阻状态。

CS信号可以被永久地置低电平,RD用来访问转换的结果。

BUSY信号为低电平时开始读操作。

AD7656有1个用来执行转换的片上振荡器,转换时间tCONVER为3μS。

转换的开始是通过脉冲调制CONVSTx信号开始的,在CONVSTx的上升沿,被选中的ADC的跟踪保持电路会被置为保持模式,转换开始。

在CONVSTx信号的上升沿后,BUSY信号会变化,这表示转换正在进行。

转换时钟是由内部产生的,转换时间是从CONVSTx信号上升沿开始的3μS,BUSY信号会变为低电平,表示转换结束。

在BUSY信号的下降沿,跟踪保持电路将回到跟踪模式。

数据通过并行或串行接口从输出寄存器中被读出。

图2示出AD7656并行接口字模式下的读操作数据流。

如果只有8bit总线被使用,那么AD7656的接口将以字节模式(W/B=I)操作,这种操作下的转换结果将通过2次读操作来访问,每次读操作通过DB15-DB8来访问1个8bit 的数据,如图3所示。

其中,tCONV为转换时间3μS,内部时钟tQUIET为总线的废弃时间到下1个转换开始之间所必需的最小等待时间,最小值为400ns;t1为读操作时的最小时间20ns;t2为BUSY信号到RD信号之间的延迟时间(ns);t3为CS到RD之间的建立时间(ns);t4为CS到RD之间的保持时间(ns);t5为RD的脉冲宽度,最小值为30ns;t6为RD下降沿后的数据访问时间,最大值为30ns;t7为RD上升沿之后的总线废弃时间,最小值为15ns,最大值为25ns。

3.2系统组成图4所示是AD7656在并行接口状态下的外围电路连接。

其中的DVcc和AVcc分别是数字电压端和模拟电压端,它们在接入前要经过1个去耦电路,如图4所示,每个供电电压输入引脚都要连接1个去耦电路,该电路由1只10μF和1只100nF的电容器组成。

VDD、Vss和VDRIVE同样要连接去耦电路。

AD7656的输出接到FPGA中进行数字信号的滤波处理,然后再送入数字信号处理器(DSP)进行处理。

用FPGA控制引脚CONVSTA/B/C、RD和CS的状态,可以用编程的方法或硬件连接的方式来实现。

系统中的FPGA是ALTERA公司的EP1K30,DSP选用ADI公司的TS101S。

此系统的外围电路比较简单,比较容易实现,具有真正的高速、高性能数字信号采集功能。

3.3应用程序举例(1)A/D数据采集部分的初始化部分程序4 注意事项在绘制PCB版图时,要注意将AD7656的模拟和数字部分分开布局,并把它们放在板上的特定区域,这样可以使地层比较容易分开,使用起来比较方便。

数字地层和模拟地层应该在板上的某一处连接到一起,可以用0Ω电阻器,也可以使用磁珠或直接用焊锡连接。

建议在布线的时候不要将数据线布在该器件的下方,因为这样做会使信号和噪声混在一起。

电源线应该尽量粗一些,这样可以尽量减小电源线的脉冲干扰。

去耦电容器应尽量地靠近器件,之间的连线要尽量短以减小感抗。

电路的性能除了受核心ADC的影响外,还受到各种外围辅助电路性能的影响。

5 结束语本文介绍了采用先进的工业CMOS(iCMOS)工艺制造的AD7656型模,数转换器,并将它应用在数字采集系统中。

多通道模/数转换器同步采样技术提高了数字信号处理的速度和精度。

AD7656的外围电路配置简单,应用领域也会越来越广泛。