Cadence元件库介绍

CADENCE的PCB封装库设计

CADENCE的PCB封装库设计CADENCE封装库的建库中兴网络事业部刘忠亮一、焊盘库的建设从Cadence的开始菜单选择padstack editor工具焊盘库主要由:孔径、焊盘、阻焊、FLASH、隔离盘等组成。

通过建一个过孔来表示一个建焊盘的过程,其它的焊盘相同。

下图中各处的定义如下:Type:through—通孔Bind/buried—盲孔/埋孔Single—表面盘Drill hole:设置是金属化还是非金属化和孔径的大小。

Drill symbol;设置钻孔的标识和标识符号的大小。

上图设定各层的焊盘、热焊盘、隔离焊盘,以及表层的阻焊层、钢网层等。

各层可以用拷贝的方法。

Regular pad—焊盘Thermal relief—FLASH热焊盘/花焊盘(要先建好,在下面介绍怎么建)Anti pad—反焊盘/隔离焊盘Soldermask_top/bottom—阻焊Pastemask_top/bottom—钢网层经以上设置OK后,选择SA VE AS将文件存为*.pad的文件,这就是所用的焊盘库,库的名称最好要有一定的规则,一看焊盘名称就能理解是什么焊盘。

二、FLASH热焊盘的设计1、打开PCB工具allegro,在drawing type中选择为flash symbol,如下图1。

2、选择菜单add-flash命令加入flash,如下图2所示。

设置花焊盘的内径/外径、花辨的宽度/数量/方向。

3、保存并创建flash通过保存生成.dra文件,以及创建出.fsm文件,把这两个文件都保存好放入库中。

这里焊盘调用FLASH时只用到FSM文件,但因为以后修改等都要通过DRA 文件重新创建出,所以最好也一并将此文件保留。

三、器件库的创建以DIP14为例:1、从ALLEGRO中新建一封装文件,从TYPE中选择package symbol2、设置单位/精度,坐标原点等。

一般以器件中心或者器件的第一脚为原点,以后放置和移动器件等均以原点为操作点。

cadence liberate 单元表征

cadence liberate 单元表征"Cadence Liberate"是一种用于半导体设计中的单元表征工具。

它被广泛应用于数字和模拟设计中,旨在帮助半导体行业快速而准确地建模和分析电路库。

以下是关于Cadence Liberate的详细介绍及其相关参考内容。

一、Cadence Liberate的特点和用途1. 特点:- Cadence Liberate提供了一个全面而灵活的环境,用于评估电路库在各种工艺过程和电压/温度/容忍度(PVT)条件下的性能。

- 它具有能够自动编辑和优化电路的能力,从而提供最佳性能和功耗的可能性。

- Cadence Liberate支持瞬态和静态分析,以验证电路的功能和时序行为。

- 该工具可以生成包括时序延迟、电流、功态和功耗在内的相关报告,用于电路库的建模和验证。

2. 用途:- 定时分析:Cadence Liberate可以评估电路中各个元件的时序性能,例如时钟延迟、数据传输延迟等。

这有助于设计人员在设计过程中提前发现和解决时序问题。

- 功耗优化:通过使用Cadence Liberate,设计人员可以分析电路库的功耗,识别功耗热点,并基于优化目标自动调整电路的逻辑结构和参数,以降低功耗。

- 可靠性分析:该工具可以评估电路在不同温度和工艺变化条件下的性能,帮助设计人员预测电路库在实际工作环境中的可靠性。

- 特性提取:Cadence Liberate可以提取电路库中各个元件的特性,例如电流、容忍度等。

这些特性可以用于电路的综合和仿真。

二、相关参考内容:(以下内容为虚构内容,无实际参考价值)1. 《Cadence Liberate用户手册》- 这本用户手册是Cadence官方提供的完整使用指南,详细介绍了Cadence Liberate的各个功能和用法。

它包括详细的步骤和示例,以帮助用户快速上手,并解决常见问题。

- 手册中包括了详细的命令和选项说明,以及用于生成报告和结果的示例代码。

Cadence原理图库的制作及使用(二)

Cadence原理图库的制作及使用(二)在上一节中,我们讲述了一种原理图库的制作方法:使用封装编辑器创建封装,然后生成符号。

在本节内容当中,我们将要讲述另外一种制作方法:先创建符号,然后由符号得到封装。

本节将要讲述另外一种方法:从符号得出封装。

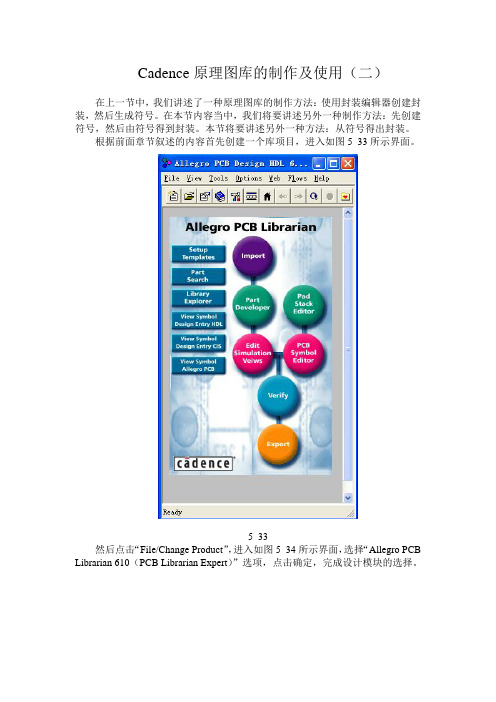

根据前面章节叙述的内容首先创建一个库项目,进入如图5_33所示界面。

5_33然后点击“File/Change Product”,进入如图5_34所示界面,选择“Allegro PCB Librarian 610(PCB Librarian Expert)”选项,点击确定,完成设计模块的选择。

5_34单击图5_33中“Part Developer”,进入库设计软件界面,如图5_35所示。

5_35选择File菜单中的New/Cell选项,出现如图5_36所示对话框。

5_36有些元件有多个相同的功能组,需要创建单个功能组的符号和整个元件的符号以方便原理图设计,满足设计的不同需求。

创建符号的方法如下:1、输入sizeable管脚并通过符号编辑器创建符号;2、创建封装;3、创建必要的通道;4、通过拷贝sym_1来创建sym_2;5、确定sym_2的SIZE属性并添加HAS_FIXED_SIZE 属性。

在“Cell”对应的空白栏处输入元件库的名称,自己可以随意写,但是最好用和芯片信息相关的名字,比如可以用元件型号命名,例如要制作74HC04的原理图元件库,在空白栏处输入74HC04,单击确定,出现如图5_37所示界面。

5_37选择左边项目栏中的symbols选项,右键点击弹出如图5_38所示界面。

5_38选择弹出菜单中的“New”选项,左键点击之后界面如图5_39所示。

5_39在右边界面当中选择“symbol pins”选项卡,界面如图5_40所示。

5_40左键点击“Pins”选项卡,弹出如图5_41 所示菜单。

选择“Add”选项,打开如图5_42所示界面。

5_415_42在该例子中,我们选择【Sizeable】单选框,74HC04芯片有一个输入管脚A,一个输出管脚Y,共有六个slots。

(完整word版)cadence软件介绍

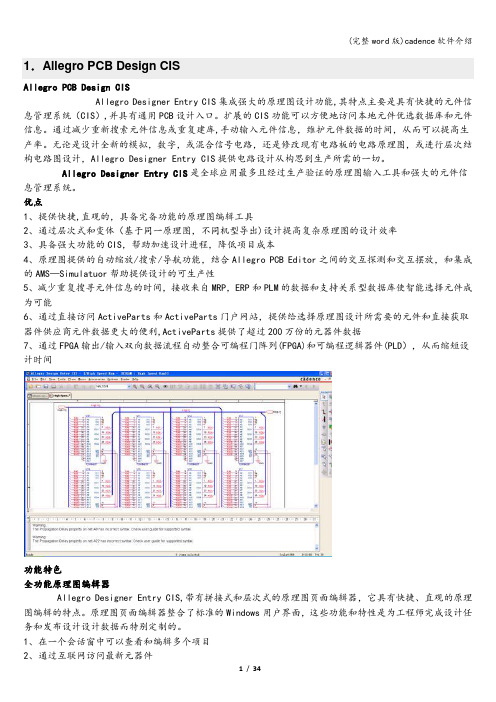

1.Allegro PCB Design CISAllegro PCB Design CISAllegro Designer Entry CIS集成强大的原理图设计功能,其特点主要是具有快捷的元件信息管理系统(CIS),并具有通用PCB设计入口。

扩展的CIS功能可以方便地访问本地元件优选数据库和元件信息。

通过减少重新搜索元件信息或重复建库,手动输入元件信息,维护元件数据的时间,从而可以提高生产率。

无论是设计全新的模拟,数字,或混合信号电路,还是修改现有电路板的电路原理图,或进行层次结构电路图设计,Allegro Designer Entry CIS提供电路设计从构思到生产所需的一切。

Allegro Designer Entry CIS是全球应用最多且经过生产验证的原理图输入工具和强大的元件信息管理系统。

优点1、提供快捷,直观的,具备完备功能的原理图编辑工具2、通过层次式和变体(基于同一原理图,不同机型导出)设计提高复杂原理图的设计效率3、具备强大功能的CIS,帮助加速设计进程,降低项目成本4、原理图提供的自动缩放/搜索/导航功能,结合Allegro PCB Editor之间的交互探测和交互摆放,和集成的AMS—Simulatuor帮助提供设计的可生产性5、减少重复搜寻元件信息的时间,接收来自MRP,ERP和PLM的数据和支持关系型数据库使智能选择元件成为可能6、通过直接访问ActiveParts和ActiveParts门户网站,提供给选择原理图设计所需要的元件和直接获取器件供应商元件数据更大的便利,ActiveParts提供了超过200万份的元器件数据7、通过FPGA输出/输入双向数据流程自动整合可编程门阵列(FPGA)和可编程逻辑器件(PLD),从而缩短设计时间功能特色全功能原理图编辑器Allegro Designer Entry CIS,带有拼接式和层次式的原理图页面编辑器,它具有快捷、直观的原理图编辑的特点。

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

Cadence自学笔记笔记

Cadence⾃学笔记笔记Cadence SPB15.7 快速⼊门视频教程⽬录Capture CIS 原理图及元件库部分第1-15讲第1讲课程介绍,学习⽅法,了解CADENCE软件Cadence下⼏个程序说明Design Entry CIS 系统级原理图设计Design Entry HDL 芯⽚设计Layout plus orcad ⾃带的pcb板布局布线⼯具,功能不是很强⼤,不推荐使⽤Pcb Editor Pcb librarian Cadence带的PCB布局布线封装设计PCB Router pcb⾃动布线Pcb SI SigXplorer Pcb电路板信号完整性仿真OrCAD Capture CIS 对元件管理更⽅便相对于OrCAD CaptureI 放⼤O 缩⼩页⾯属性设置options Design Templateoptions Schematic Page Propertie s第2讲创建⼯程,创建元件库原理图元件库,某元件分成⼏个部分,各部分间浏览ctrl+N ctrl+B元件创建完后修改footprint封装,options Package Properties第3讲分裂元件的制作⽅法1、homogeneous 和heterogeneous 区别homogeneous,芯⽚包含⼏个完全相同的部分选择该模式,画好第⼀个part后,后⾯的part会⾃动⽣成,因为完全⼀样。

但是引脚编号留空了,要⾃⼰再设置引脚编号。

heterogeneous芯⽚包含⼏个功能部分,可按照功能部分分成⼏个部分。

ctrl+N ctrl+B切换分裂元件的各个部分原理图画完之后,要对各元件⾃动编号,在项⽬管理窗⼝选择项⽬,点击tools annotate,在Action下⾯选择相应的动作。

2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使⽤heterogeneous类型的元件1、可能出现的错误Cannot perform annotation of heterogeneous part J?A(Value RCA_Octal_stack ) part has not been uniquely group(using a common User Property with differing Values) or the device designation has not been chosen2、出现错误的原因分裂元件分成⼏个part,并且⽤了多⽚这样的分裂元件。

Cadence各层作用及封装信息传输对应关系

Cadence 各层作用及封装信息传输关系(2013-12-20 22:48:04)转载▼silkscreen top:是字符层,一般称顶层字符或元件面字符,为各元器件的外框及名称标识等assemly top :是装配层,就是元器件含铜部分的实际大小,用来产生元器件的装配图。

我自己感觉这一层 如果对于贴片的元器件,如电容,就是两个贴片铜片的实际大小,而place_bound_top 层是整个贴片元器件的实际大小,这一点很多人都没真正搞懂!也可以使用此层进行布局;place_bound_top :是元器件封装实际大小,用来防止两个元器件叠加在一起不报错。

Autosilk top, Silkscreen top 和Assembly topAutosilk top :最后出gerber 的时候,自动生成的丝印层。

会自动调整丝印位置,以及碰到阻焊开窗的地方,丝印会自动消失,避免露锡的地方涂上丝印(一般画丝印层的时候,焊盘上不会画上丝印,所以过孔焊盘上有丝印,也不会有什么影响。

),所以我个人一般很少用到Autosilk top 层,毕竟最后出丝印的时候,都需要调整位置。

我一般直接用Silkscreen top 。

Silkscreen top :建库的时候,ref des 放置的层,及PCB 生产时,刷到板卡上的字符、器件外框或者公司LOGO 等放置的层。

我出gerber ,一般直接出这一层。

Assembly top :安装丝印层。

因为有些公司需要出安装图,有些为了手工焊接,喜欢把字符丝印放置在器件内部,比如电阻位号,喜欢把它的丝印放置在电阻符号外框的中间位置。

比如说电阻值等,想打印出来放置在安装图纸的电阻相应位置。

这时我们才会用到安装丝印层。

平时可以不用,或者平时只用Silkscreen top 。

所以这三个丝印层各有各的作用。

总体来说,cadence 软件定义的这些层使用很灵活,每个人用法可能稍微有差异,都是没关系的,只要实现你的使用目的即可。

cadence简介

现在需要设置元件参数,有三种方法,①菜单栏-> Edit-> Properties-> Objects,再点击要修改参数的元件,②先选中器件,再键入快捷键q,③选中器件,再点击工具栏Propertiy。

参数可以是以下三种形式的各种数学组合表达式,①变量,②常量,③skill语言函数。变量作参数会在仿真时用到。常量和skill语言函数作参数,在下面就会用到。

同样的方法继续设置NMOS参数,只是模型名为n18,栅长为固定值0.18u,栅宽设为pPar(“wn”)。设置好参数后的电路图如图3.9所示。

注意:①设置参数时不要自己输入单位,系统会自动加上。比如0.18uM是错误的写法。如果非要自己写单位,也要和数值之间留一个空格,否则系统会把M识别为变量。

2.

现在,我们可以启动Cadence了。在终端中输入命令

icfb&

出现Cadence初始界面,如图2.1所示。

然后就会打开Cadence的主控窗口CIW(Command Interpreter Window)。如图2.2所示:

这就是Cadence的集成设计环境,Cadence的大部分工具都可以从这里打开。其中最上方是标题栏,第二行是菜单栏。中间部分是输出区域,许多命令的结果在这里显示。一些出错信息也在这里显示,要学会从输出区域中获取相应的信息。接下来一行是命令输入行。Cadence的许多操作可以通过鼠标执行,也可以通过输入命令来执行。

进入连线命令后,于起点单击左键,再于终点单击左键。画完一段导线后,此时并没有退出画线命令,可以继续画连接线,直到画完所所有的连接线后,按ESC退出画线命令。连好线的电路图如图3.7所示。其中左右两条水平导线是后面连连接端口用的。

还可以对画好的线进行命名,键入快捷键l,在弹出的对话框中输入线名,比如a,点击Hide,然后将字母a移动到要命名的线附近点击左键放下,如果名字离线较远,则要求再单击所要命名的线。

Cadence元件封装及常见问题解决

Cadence元件封装及常见问题解决Cadence 使⽤及注意事项⽬录1 PCB⼯艺规则 (1)2 Cadence的软件模块 (2)2.1 Cadence的软件模块--- Pad Designer (2)2.2 Pad的制作 (3)2.2.1 PAD物理焊盘介绍 (3)3 Allegro中元件封装的制作 (5)3.1 PCB 元件(Symbol)必要的CLASS/SUBCLASS (5)3.2 PCB 元件(Symbol)位号的常⽤定义 (8)3.3 PCB 元件(Symbol)字符的字号和尺⼨ (8)3.4 根据Allegro Board (wizard)向导制作元件封装 (9)3.5 制作symbol时常遇见的问题及解决⽅法 (15)4 Cadence易见错误总结 (15)1 PCB⼯艺规则以下规则可能随中国国内加⼯⼯艺提⾼⽽变化(1)不同元件间的焊盘间隙:⼤于等于40mil(1mm),以保证各种批量在线焊板的需要。

(2)焊盘尺⼨:粘锡部分的宽度保证⼤于等于10mil(0.254mm),如果焊脚(pin)较⾼,应修剪;如果不能修剪的,相应焊盘应增⼤…..(3)机械过孔最⼩孔径:⼤于等于6mil(0.15mm)。

⼩于此尺⼨将使⽤激光打孔,为国内⼤多数PCB⼚家所不能接受。

(4)最⼩线宽和线间距:⼤于等于4mil(0.10mm)。

⼩于此尺⼨,为国内⼤多数PCB ⼚家所不能接受,并且不能保证成品率!(5)PCB 板厚:通常指成品板厚度,常见的是:0.8mm、1mm、1.2mm、1.6mm、2.0mm;材质为FR-4。

当然也有其它类型的,⽐如:陶瓷基板的…(6)丝印字符尺⼨:⾼度⼤于30mil(0.75mm),线条宽⼤于6mil(0.15mm),⾼与宽⽐例3:2(7)最⼩孔径与板厚关系:⽬前国内加⼯能⼒为:板厚是最⼩孔径的8~15倍,⼤多数多层板PCB ⼚家是:8~10倍。

举例:假如板内最⼩孔径(如:VIA)6mil,那么你不能要求⼚家给你做 1.6mm厚的PCB 板,但可以要求 1.2mm或以下的。

altium designer元件库

altium designer元件库Altium Designer元件库:从基础认识到高级应用引言:Altium Designer作为一款领先的电子设计自动化(EDA)软件,广泛应用于电子工程领域。

元件库作为其重要组成部分,承载着各种电子元器件的相关信息。

本文将从基础概念开始介绍Altium Designer元件库的基本知识和使用方法,然后探讨一些高级应用和技巧。

无论是初学者还是有一定经验的设计师,本文将为您提供宝贵的参考和指导。

一、Altium Designer元件库的基础知识1.1元件库的定义和作用元件库是Altium Designer中保存和管理电子元器件的数据库。

它包含了各种电子元器件的符号、封装、参数、模型等信息,为电子设计提供便利。

1.2元件库的分类Altium Designer中的元件库分为库文件库和数据库两种类型。

库文件库主要是以库文件的形式存储电子元器件信息,而数据库则使用统一的数据管理系统,更加强调元器件的参数和模型的管理。

二、使用Altium Designer创建和管理元件库2.1创建元件库在Altium Designer中,可以通过新建库文件或者新建数据库来创建元件库。

通过库文件,可以更加灵活地对元器件进行管理,而使用数据库则更加便于共享和协作。

2.2导入元器件库Altium Designer支持导入现有的元器件库,以便快速利用之前的工作成果。

可以导入Protel格式、OrCAD格式和许多其他常见的元器件库格式。

2.3添加和编辑元器件在元件库中,可以通过添加或编辑元器件的方式来完善库存。

对于已有的元器件,可以通过修改参数和模型来更新相关信息,也可以通过删除和复制等操作进行管理。

三、Altium Designer元件库的高级应用3.1生成3D模型Altium Designer可以根据元器件的封装信息自动生成相应的3D 模型,以便进行更加真实的设计和模拟。

在元件库中,可以添加、编辑和管理3D模型,提高设计的可靠性和可视化效果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence元件库介绍

AMPLIFIER.OLB共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093等。

ARITHMETIC.OLB共182个零件,存放逻辑运算IC,如TC4032B,74LS85等。

ATOD.OLB共618个零件,存放A/D转换IC,如ADC0804,TC7109等。

BUS DRIVERTRANSCEIVER.OLB共632个零件,存放汇流排驱动IC,如74LS244,74LS373等数字IC。

CAPSYM.OLB共35个零件,存放电源,地,输入输出口,标题栏等。

CONNECTOR.OLB共816个零件,存放连接器,如4HEADER,CON AT62,RCA JACK等。

COUNTER.OLB共182个零件,存放计数器IC,如74LS90,CD4040B。

DISCRETE.OLB共872个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零件。

DRAM.OLB共623个零件,存放动态存储器,如TMS44C256,MN41100-10等。

ELECTRO MECHANICAL.OLB共6个零件,存放马达,断路器等电机类元件。

FIFO.OLB共177个零件,存放先进先出资料暂存器,如40105,SN74LS232。

FILTRE.OLB共80个零件,存放滤波器类元件,如MAX270,LTC1065等。

FPGA.OLB存放可编程逻辑器件,如XC6216/LCC。

GATE.OLB共691个零件,存放逻辑门(含CMOS和TLL)。

LATCH.OLB共305个零件,存放锁存器,如4013,74LS73,74LS76等。

LINE DRIVER RECEIVER.OLB共380个零件,存放线控驱动与接收器。

如SN75125,DS275等。

MECHANICAL.OLB共110个零件,存放机构图件,如M HOLE2,PGASOC-15-F等。

MICROCONTROLLER.OLB共523个零件,存放单晶片微处理器,如68HC11,AT89C51等。

MICRO PROCESSOR.OLB共288个零件,存放微处理器,如80386,Z80180等。

MISC.OLB共1567个零件,存放杂项图件,如电表(METER MA),微处理器周边(Z80-DMA)等未分类的零件。

MISC2.OLB共772个零件,存放杂项图件,如TP3071,ZSD100等未分类零件。

MISCLINEAR.OLB共365个零件,存放线性杂项图件(未分类),如14573,4127,VFC32等。

MISCMEMORY.OLB共278个零件,存放记忆体杂项图件(未分类),如28F020,X76F041等。

MISCPOWER.OLB共222个零件,存放高功率杂项图件(未分类),如REF-01,PWR505,TPS67341等。

MUXDECODER.OLB共449个零件,存放解码器,如4511,4555,74AC157等。

OPAMP.OLB共610个零件,存放运放,如101,1458,UA741等。

PASSIVEFILTER.OLB共14个零件,存放被动式滤波器,如DIGNSFILTER,RS1517T,LINE FILTER等。

PLD.OLB共355个零件,存放可编程逻辑器件,如22V10,10H8等。

PROM.OLB共811个零件,存放只读记忆体运算放大器,如18SA46,XL93C46等。

REGULATOR.OLB共549个零件,存放稳压IC,如78xxx,79xxx等。

SHIFTREGISTER.OLB共610个零件,存放移位寄存器,如4006,SNLS91等。

SRAM.OLB共691个零件,存放静态存储器,如MCM6164,P4C116等。

TRANSISTOR.OLB共210个零件,存放晶体管(含FET,UJT,PUT等),如2N2222A,2N2905等。