DSP总结(附程序)

DSP入门教程(非常经典)

3)对于 C5000 系列: 硬件等待信号为 READY,高电平时不等待。 软件等待由 SWWCR 和 SWWSR 寄存器决定,可以加入最多 14 个等待。其中程序存储器、控制程序存储器和 数据 存储器及 I/O 可以分别设置。

4)地址译码、IO 扩展等用 CPLD 或者 FPGA 来做,将 DSP 的地址线、数据线、控制信 号 线如 IS/PS/DS 等都引进去有利于调试

5、如何高效开始 TI DSP 的软件开发 如果你不是纯做算法,而是在一个目标版上进行开发, 需要使用 DSP 的片上外设,需要控 制片外接口电路,那么建议在写程序前先好好将这个目标 版的电路设计搞清楚。最重要的是 程序、数据、I/O 空间的译码。不管是否纯做算法还是软硬结合, DSP 的 CPU,memory,program memory addressing, data mem.ory addressing 的资料都需要看.

1)看 CCS 的使用指南

2)明白 CMD 文件的编写

3)明白中断向量表文件的编写,并定位在正确的地方

4)运行一个纯 simulator 的程序,了解 CCS 的各个操作

5)到 TI 网站下相关的源码,参考源码的结构进行编程

6)不论是 C 编程还是 ASM 编程,模块化是必须的

6、选择 C 还是选择 ASM 进行编程 记住一条原则,TI 的工程师在不断改进 CCS 的 C 程序优化编译器,现在 C 优化的效率可 达 到手工汇编的 90%甚至更高。当然有的时候如果计算能力和内存资源是瓶颈,ASM 还 是有 优势,比如 G.729 编解码。但是针对一般的应用开发,C 是最好的选择。 新手编程则选择 C 和汇编混合编程更有利一些

DSP程序烧写说明

DSP程序烧写步骤:

1、连接好仿真器,目标板上电(通上电后仿真器的绿灯会亮)

2、打开CCS,双击此图标,如果目标板连接正常,则可进入如下图所示界面

3、如下图所示,加载meter.out文件。

文件路径:E:\test\ProgFlash

另外在归档文件中也有备份

4、成功加载后,如下图所示。

将窗口最大化,点击如下图所示的图标,运行程序

运行后(大概几秒钟)会弹出一个如下图所示对话框

在对话框中输入要烧写的bin文件路径及文件名(如果要烧写的文件就在此文件

夹内,则只输入文件名即可,不用再输入路径)

注:如果点击运行后立即弹出此对话框,说明程序未执擦除flash操作,此时将

不能正常烧

入程序。

此类

情况一般是

DSP或者

Flash等的数

据线没焊好

造成。

烧写过程中运行图标为不可用状态,如图1所示图1 图2

烧写完成后,恢复成可用状态,如图2所示。

至

此程序烧写完成。

DSP程序版本:

1、单相标准表烧smeter.bin

2、三相标准表烧DSPTX.bin

3、9700DB上用的DSP程序源上烧source.bin 表上烧DSPH.bin

烧写表上源DSP程序时,如果是新的DSP片子,先加载lj.out,运行一下,给DSP送一个基本参数。

再烧按平时操作方式烧写相应的应用程序。

但运行lj.out并未解决问题,运行后无任何反应。

dsp

摘要随着数字信号处理技术在通讯、多媒体、信息家电等各个领域得到了广泛的应用,数字信号处理器(DSP)无论从制造工艺、体系结构等方面都取得了巨大的发展。

因此设计有自主产权的DSP处理器IP核具有很高的实用价值及意义。

通过对片上串行接口的模块划分,完成了串口寄存器模块、时钟与帧同步信号控制器模块、接收控制器模块和发送控制器模块的详细设计和FPGA验证。

其中,设计了一种采用一个主控状态机和两个从状态机协同工作的层次化结构方案,规整高效地实现了接收控制器模块和发送控制器模块。

通过对6通道DMA控制器的模块划分,完成了内部寄存器组、优先级编码模块、内部寄存器寻址、地址产生模块和有限状态机等模块的详细设计和FPGA验证。

其中,设计了一种采用模计数和循环比较的结构方案,实现了对6个DMA通道进行分级循环优先级控制的机制。

论文从主机接口(HPI)寄存器、状态机两个方面论述和设计实现一个8位外总线接口。

并完成了内部定时器和可编程等待状态发生器的设计。

目前该兼容DSP处理器的设计已经完成,通过了FPGA验证,能运行基本的功能验证程序,为进一步研发该DSP的可重用IP模块打下了基础。

关键字:数字信号处理器,串行接口,直接寄存器访问控制器,主机接口、定时器、等待状态发生器引言:近年来,我国电子信息产业和市场高速增长,不仅推动了DSP处理器芯片的广泛应用,而且吸引了国内外众多厂商涉足我国DSP处理器产品市场,促使DSP处理器芯片需求量持续增大,市场竞争日渐激烈。

尽管DSP处理器在我国的应用已经有了相当的基础,而且有lO多家集成电路设计企业从事DSP系统及相关产品的开发与应用,但目前在国内芯片市场上还很少见到国内厂商自己的DSP 处理器芯片。

因此研制有自主知识产权的DSP处理器设计技术,以及相应的DSP 系统设计技术与应用能力,仍然是我国科技工作者和IT企业的重大挑战。

1.2.1 DSP处理器的发展史人们对DSP技术的研究兴趣开始于二十世纪七十年代,主要是研究诸如调制解调器和集中转接系统等电信设备。

dsp汇编指令系统介绍(精)

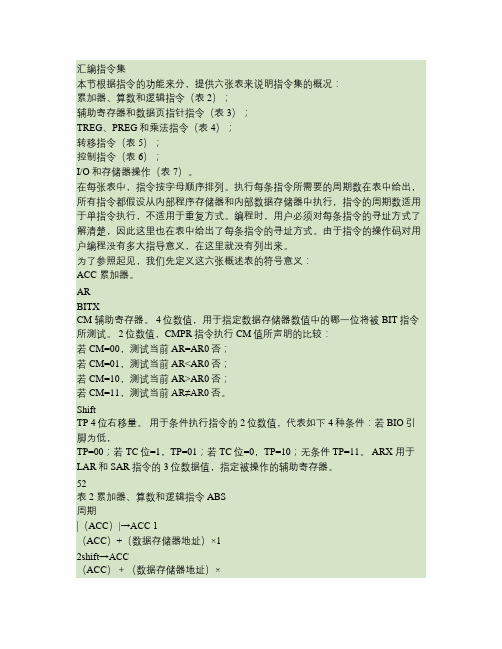

汇编指令集本节根据指令的功能来分,提供六张表来说明指令集的概况:累加器、算数和逻辑指令(表2);辅助寄存器和数据页指针指令(表3);TREG、PREG和乘法指令(表4);转移指令(表5);控制指令(表6);I/O和存储器操作(表7)。

在每张表中,指令按字母顺序排列。

执行每条指令所需要的周期数在表中给出,所有指令都假设从内部程序存储器和内部数据存储器中执行,指令的周期数适用于单指令执行,不适用于重复方式。

编程时,用户必须对每条指令的寻址方式了解清楚,因此这里也在表中给出了每条指令的寻址方式。

由于指令的操作码对用户编程没有多大指导意义,在这里就没有列出来。

为了参照起见,我们先定义这六张概述表的符号意义:ACC 累加器。

ARBITXCM 辅助寄存器。

4位数值,用于指定数据存储器数值中的哪一位将被BIT指令所测试。

2位数值,CMPR指令执行CM值所声明的比较:若CM=00,测试当前AR=AR0否;若CM=01,测试当前AR<AR0否;若CM=10,测试当前AR>AR0否;若CM=11,测试当前AR≠AR0否。

ShiftTP 4位右移量。

用于条件执行指令的2位数值,代表如下4种条件:若BIO引脚为低,TP=00;若TC位=1,TP=01;若TC位=0,TP=10;无条件TP=11。

ARX 用于LAR和SAR指令的3位数据值,指定被操作的辅助寄存器。

52表2 累加器、算数和逻辑指令 ABS周期|(ACC)|→ACC 1(ACC)+(数据存储器地址)×12shift→ACC(ACC)+(数据存储器地址)×216→ACC 1(ACC)+k→ACC 1shift(ACC)+lk×2→ACC 2指令功能(ACC)+(数据存储器地址)+(C)→ACC寻址方式直接/间接直接/间接短立即数长立即数指令说明ACC取绝对值移位时低位填0,若SXM=1,高位用符号扩展;若SXM=0,高位填0;结果存在ACC中,该指令使C=0。

DSP实验报告

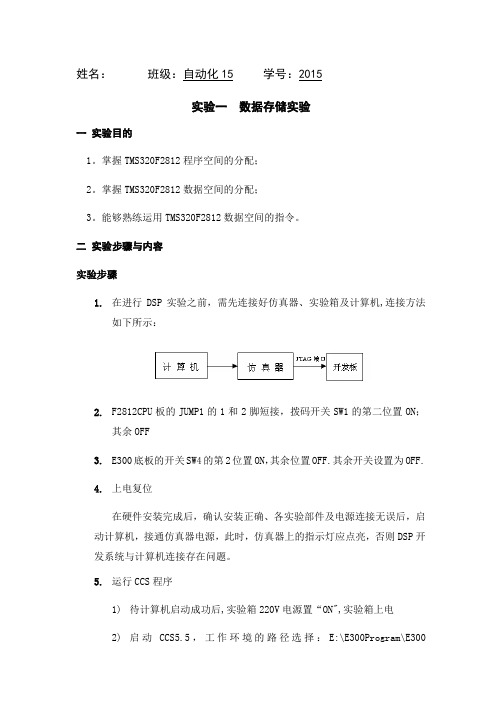

姓名:班级:自动化15 学号:2015实验一数据存储实验一实验目的1。

掌握TMS320F2812程序空间的分配;2。

掌握TMS320F2812数据空间的分配;3。

能够熟练运用TMS320F2812数据空间的指令。

二实验步骤与内容实验步骤1.在进行DSP实验之前,需先连接好仿真器、实验箱及计算机,连接方法如下所示:2.F2812CPU板的JUMP1的1和2脚短接,拨码开关SW1的第二位置ON;其余OFF3.E300底板的开关SW4的第2位置ON,其余位置OFF.其余开关设置为OFF.4.上电复位在硬件安装完成后,确认安装正确、各实验部件及电源连接无误后,启动计算机,接通仿真器电源,此时,仿真器上的指示灯应点亮,否则DSP开发系统与计算机连接存在问题。

5.运行CCS程序1)待计算机启动成功后,实验箱220V电源置“ON",实验箱上电2)启动CCS5.5,工作环境的路径选择:E:\E300Program\E300TechV-2812\normal ;6.成功运行CCS5.5程序后,出现如下图所示界面:7.右键点击Project Explorer窗口下的工程文件“e300_01_mem”,选择“Open Project"命令打开该工程,如下图所示,可以双击才看左侧源文件;8.点击菜单栏Project/Build All命令编译整个工程,编译完成后点击按钮进入仿真模式,完全进入后如下图所示:9.用“View"下拉菜单中的“Memory/Browser”查看内存单元,参数设置如下图:注意:下面的参数设置都是以16进制。

此时可以观测到以0x003F9020为起始地址的存储单元内的数据;10.单击按钮,开始运行程序,一段时间后,单击按钮,停止程序运行,0x003F9020H~ 0x3F902FH单元的数据的变化,如下图所示:11.关闭Memory Browser窗口,点击按钮,退出仿真模式。

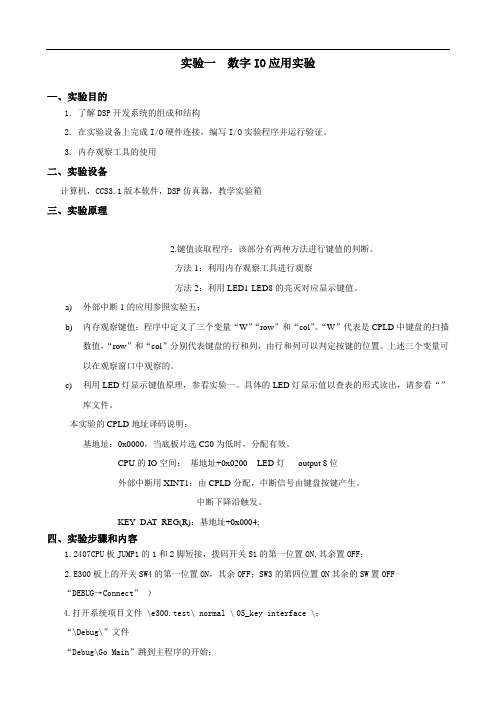

DSP实验报告

实验一数字IO应用实验—、实验目的1. 了解DSP开发系统的组成和结构2. 在实验设备上完成I/O硬件连接,编写I/O实验程序并运行验证。

3. 内存观察工具的使用二、实验设备计算机,CCS3.1版本软件,DSP仿真器,教学实验箱三、实验原理2.键值读取程序:该部分有两种方法进行键值的判断。

方法1:利用内存观察工具进行观察方法2:利用LED1-LED8的亮灭对应显示键值。

a)外部中断1的应用参照实验五;b)内存观察键值:程序中定义了三个变量“W”“row”和“col”。

“W”代表是CPLD中键盘的扫描数值,“row”和“col”分别代表键盘的行和列,由行和列可以判定按键的位置。

上述三个变量可以在观察窗口中观察的。

c)利用LED灯显示键值原理,参看实验一。

具体的LED灯显示值以查表的形式读出,请参看“”库文件。

本实验的CPLD地址译码说明:基地址:0x0000,当底板片选CS0为低时,分配有效。

CPU的IO空间:基地址+0x0200 LED灯output 8位外部中断用XINT1:由CPLD分配,中断信号由键盘按键产生。

中断下降沿触发。

KEY_DAT_REG(R):基地址+0x0004;四、实验步骤和内容1.2407CPU板JUMP1的1和2脚短接,拨码开关S1的第一位置ON,其余置OFF;2.E300板上的开关SW4的第一位置ON,其余OFF;SW3的第四位置ON其余的SW置OFF“DEBUG→Connect”)4.打开系统项目文件 \e300.test\ normal \05_key interface \;“\Debug\”文件“Debug\Go Main”跳到主程序的开始;7.指定位置设置断点;8.View--〉Watch Window打开变量观察窗口;9. 将变量“w”“row”和“col”添加到观察窗口中,改变变量观察窗口的显示方式为HEX显示。

“Debug--〉Animate”全速运行,然后点击E300板上键盘按键,观察窗口中变量变化,同时LED1-LED8灯也相应变化,指示键值。

DSP程序在线升级报告(本人觉得最给力的资料)

DSP程序在线升级唐俊松*******************.cn2015/12/04 1. 引言一般而言,DSP程序更新是在CCS环境下通过JTAG接口来实现的。

但JTAG烧写程序只能实现一对一烧写(即电脑到DSP),且不能远距离烧写程序。

而当产品发布后或需要同时升级多个DSP程序时,通过JTAG烧写程序则很难实现。

在线程序升级的主要思想是通过串口通信更新程序,通过串口通信可实现程序远程升级且可同时实现对多个DSP的程序更新,这有效地解决了JTAG烧写程序所存在的弊端。

1. 通过JTAG更新DSP程序2. 通过串口(RS232)更新DSP程序图1.1 通过不同方式实现DSP程序更新2. 程序在线升级的基本思想基于串口通信的程序在线升级功能框图如图2.1所示,底层程序(Prog Local)和应用程序(Prog App)分别由两个独立的CCS Project产生。

底层程序(Prog Local)是产品发布前通过JTAG烧写固化在DSP指定Flash空间中的程序,不允许用户修改和擦除,主要用于实现与上位机的通信,同时在需要升级程序时将上位机发送过来的程序代码烧写到FLASH中。

应用程序(Prog App)是可以更新的程序。

通过CCS编译产生程序代码文件(hex),然后通过RS232通信将程序代码发送到DSP,继而由底层程序(Prog Local)将应用程序代码烧写到应用程序所对应FLSH空间(Prog App)中。

图2.1 DSP程序在线升级功能框图在线升级程序流程图如图2.2所示。

DSP上电复位后先运行底层程序,在底层程序中判断是否需要升级,如不需要升级,则跳转到应用程序执行。

如需要升级,则擦除应用程序对应FLASH区,并将升级代码写入到应用程序FLASH区中。

图2.2 DSP程序更新流程图3. 在线程序升级的具体实现3.1 FLASH分配要实现程序在线升级,必须使底层程序和应用程序相互独立。

DSP程序的调试和分析方法

谱图与输出信号比较,可以判断DFT算法编写是否正确。

11.选择File→Data→Load/Save命令,对输入信号数据输入模拟信号,并将输出信号写入

主机上的一个数据文件,然后刷新CCS中的图形显示窗口。注意,可以在第3章的实

选择Add Files to Project命令,打开一个文件选择对话框,选择刚保存的源文件加入工

程中。

4.把CCS安装目录下的C5400\cgtools\lib\rts.1ib文件加入工程。(注意:如果选择把CCS

安装目录下的C5400\cgtools\lib\rts_ext.1ib文件加入工程,还需要设置编译选项,方法是选择Project→Build Options命令,打开Build Options对话框,在Compiler选项卡的

Files表单说明项目中每个文件的测试范围信息;Functions表单一般用于统计C函数的测试信息;Ranges用于统计“测试区域’’信息;Setup表单用于建立“测试段”。设置测试区域最方便的方法时在源文件中选中感兴趣的代码段,然后将其拖入Ranges表单即可。运行程序,程序运行时间的数据在窗口中显现。Count表示该段程序在运行停止之前所运行过的次数,其他的各项均表示运行时间信息,以指令周期为单位。

离散时间信号可以用若干个幅值不同的正弦信号叠加而成,单个正弦信号的离散时间表示方

式为x(n)=sin(n×2π×f/fs)其中f表示信号频率,fs表示采样频率。

2.离散傅里叶变换公式。

其中 = , 0≤kຫໍສະໝຸດ N-1离散傅里叶变换的目的是把信号由时域变换到频域,在频域分析信号特征,是数字信号处理领域常用的方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP总结(附程序)1.数字信号处理器也称DSP芯片,是一种特别适合于进行数字信号处理运算的微处理器,主要应用是实时快速地实现各种数字信号处理算法。

2.DSP芯片的主要特点:1。

哈佛结构;2.多总线结构;3.流水线结构;4。

多处理单元;5。

特殊的DSP指令;6.指令周期短;7.运算精度高; 8.硬件配置强3.选择DSP芯片时应考虑的因素:1)DSP芯片的运算速度:这是一项很重要的性能指标,决定系统实时性问题。

运算速度可以用以下几种性能指标来衡量:①指令周期:执行一条指令所需要的时间,通常以毫秒为单位。

② MAC时间:完成一次乘法和一次加法的时间.③ FFT执行时间:运行一个N点FFT程序所需的时间。

④ MIPS:每秒执行百万条指令。

⑤ MOPS:每秒执行百万次操作.⑥ MFLOPS:每秒执行百万次浮点操作.⑦ BOPS:每秒执行十亿次操作。

2)DSP芯片的硬件资源:如片内ROM和RAM的大小,外部可扩展的程序、数据和空间,总线接口和I/O接口等。

3)DSP芯片的运算精度:参加运算的数据字长越长精度越高。

一般DSP字长16位,如TI公司的TMS320系列;有的定点芯片字长为24位,如MOTOLORA公司的MC56001。

浮点芯片为32位。

4)DSP芯片的功耗。

4.TMS320C54x是16位定点数字信号处理器.TMS320C54x的体系结构采用改进的哈佛结构,程序与数据分开存放,内部具有8条高度并行的总线。

片内集成有片内的存储器和片内的外设以及专门用途的硬件逻辑,并配备有功能强大的指令系统,使得该芯片具有很高的处理速度和广泛的应用适应性。

再加上采用模块化设计以及先进的集成电路技术,芯片的功耗小,成本低,自推出以来已广泛地应用于诸如移动通信、数字无线电、计算机网络以及各种专门用途的实时嵌入系统和仪器仪表中。

5.TMS320C54x的硬件结构基本有三大块:1)CPU 包括算术逻辑运算单元、乘法器、累加器、移位寄存器、各种专门用途的寄存器、地址生成器以及内部总线;2)存储器系统包括16~24位外接存储器接口、片内的程序ROM、片内单访问的数据RAM和双访问的数据RAM;3)片内的外设与专用硬件电路包括片内的定时器、各种类型的串口、主机接口、片内的锁相环(PLL)时钟发生器以及各种控制电路.6.TMS320C54x的主要特性—-CPU部分1)先进的多总线结构.2)40位算术逻辑单元(ALU)。

3)17位×17位并行乘法器与一个40位专用加法器相连。

4)比较、选择、存储单元(CSSU)。

5)指数编码器可以在单个周期内计算40位累加器中数值的指数。

6)双地址生成器包括8个辅助寄存器和两个辅助寄存器算术运算单元(ARAU)。

7.TMS320C54x的主要特性—-存储器系统(内核中的汇编)具有16位192K字的可寻址空间:1)64 K字程序存储器2)64 K字数据存储器3)64K字I/O空间4)在C548、C549、C5402、C5410和C5420中程序存储器可以扩展。

5)不同型号芯片的片内存储器的结构及容量也不同.8.TMS320C54x的主要特性——在片外设和专用电路⑧可与主机直接连接的8位并行主机接口(HPI),有些产品还包括扩展的8位并行主机接口(HPI8)和16位并行主机接口(HPI16)⑨片内的串口根据型号不同可分为全双工的标准串口、支持8位和16位数据传送、时分多路(TDM)串口、缓冲串口(BSP)以及多通道缓冲串口(McBSP)9.TMS320C54x的主要特性——电源和功耗①可采用5v(C),3.3v(LC),3v(UC)1.8v或2.5v(VC)的超低电压供电②可采用功能下降指令IDLE1、IDLE2和IDLE3控制芯片的功耗.③可控制禁止CLKOUT信号10.’C54x片内存储器简介:(1)片内ROM:1)多用作程序存储空间的一部分;2)2K容量的ROM含一个TI公司定义的引导装入程序,用于将程序;3)快速引导入片内或片外的快速RAM中;4)大容量ROM可划分为数据及程序空间;5)较大的ROM属于通用的ROM,可以利用TI公司提供的合适工具和方法;6)将目标文件格式的代码和数据固化到ROM中。

(2)片内双访问RAM(DARAM):1)DARAM由几个块组成;2)各DARAM块在每个机器周期内可被访问两次;3)常被划分为数据空间存储数据值;4)也可划分为程序空间存储程序代码;5)’C5416片内含64K字程序/数据DARAM,分8块,每块8K字.11.’C54x的外部程序存储器可寻址64K字的存储空间。

他们的片内ROM、双寻址RAM(DARAM)以及单寻址RAN(SARAM),都可以通过软件映像到程序空间。

档存储单元映像到程序空间时,处理器就能自动地对它们所处的地址范围寻址.12.TMS320C54x存储器由3个独立的可选择空间组成:程序空间、数据空间和I/O空间.在任何一个存储空间内,RAM、ROM、EPROM、EEPROM或存储器映像外围设备都可以驻留在片内或者片外。

3个空间的总地址范围为192K字。

程序存储器空间存放要执行的指令和执行中所用的系数表,数据存储器存放执行指令所要用的数据。

I/O存储空间与存储映像外围设备接口,可以作为附加的数据存储空间使用.在’C54x中片内存储器的形式有DARAM、SARAM和ROM3种,取决于芯片的型号。

RAM总是安排到数据存储空间,但也可以构成存储空间。

ROM一般构成程序存储空间,也可以部分安排数据存储空间。

’C54x的3个状态位:MP/位、OVLY位和DROM位.13.2K字程序空间(F800H~FFFFH)中包含以下内容(TI公司定义的):1)自举加载程序从串行口、外部存储器、I/O口,或者主机接口自举加载;2)256字律压扩表;3)256字A律压扩表;4)256字正弦函数值查找表;5)中断向量表。

14.CPU(中央处理单元)的基本组成:1)40位算术逻辑单元(ALU)2)2个40位累加器3)一个16~30位的桶形移位寄存器4)乘法器/加法器单元5)比较、选择和存储单元(CSSU)6)指数编码器7)CPU状态和控制寄存器8)两个地址发生器15.40位桶形移位寄存器的输入端来源:(数据来源)1)DB取得16位输入数据;2)DB和CB取得32位输入数据;3)40位累加器A和B。

桶形移位器的功能框图16.程序地址发生器(PAGEN)共有5个寄存器:1)程序计数器(PC)2)重复计数器(RC)3)块重复计数器(BRC)4)块重复起始地址寄存器(RSA)5)块重复结束地址寄存器(REA)17.完整的片内外设配置包括通用I/O引脚、定时器、时钟发生器、主机接口(HPI)、软件可编程等待状态发生器、串行通信接口和可编程存储器切换逻辑等.18.锁相环电路(PLL)通过设定芯片的3个时钟模式引脚CLKMD1、CLKMD2和CLKMD3的电平,可以选择片内振荡时钟与外部参考时钟的倍频.19.软件的时钟频率调节方式灵活方便,可以设置以下两种时钟模式之一:①倍频模式,输入时钟乘以从0。

25~15共31档比例系数之一;②分频模式(DIV),输入时钟CLKIN2分频或4分频.20.HPI接口:TMS320C54x片内都有一个主机接口(HPI),而HPI是一个8位的并行口,用来与主设备或主处理器接口.外部主机是HPI的主控者,它可以通过HPI直接访问CPU的存储空间,包括映像存储器。

21.主机接口(HPI)各功能解释:1)HPI存储器(DARAM) HPI RAM主要用于TMS320C54x与主机之间传送数据,也可以用作通用的双寻址数据RAM或程序RAM。

2)HPI地址寄存器(HPIA)它只能由主机对其直接访问,寄存器中存放当前寻址的存储单元的地址。

3)HPI数据锁存器(HPID)它同HPIA一样只能由主机对其直接访问。

4)HPI控制寄存器(HPIC) TMS320C54x和主机都能对它直接访问,它映像在TMS320C54x数据存储器的地址为002CH.5)HPI控制逻辑用于处理HPI与主机之间的接口信号。

22.HPI的2种工作方式:1)共用访问模式(SAM):常用主机和DSP都能访问HPI存储器;异步工作的主机访问可以在HPI内部重新得到同步;主机和DSP的周期发生冲突时(同时读或写),主机具有访问优先权,DSP等待一个周期.2)仅主机访问模式(HOM):只有主机能访问HPI存储器;主机可以以更快速度访问,与'C54x的时钟速率无关,DSP处于复位状态或所有内部外部时钟都停止的IDLE2空闲状态(最小功耗状态)。

23.中断系统:’C54xDSP及支持软件中断,也支持硬件中断.1)由程序指令(INTR、TRAP或RESET)请求的软件中断;2)由外部物理设备信号请求的硬件中断。

该中断有两种形式:①受外部中断口信号触发的外部硬件中断;②受片内外设电路信号触发的内部硬件中断。

24.中断分类:’C54x DSP可支持16个用户可屏蔽中断(SINT15-SINT0)1)可屏蔽中断对’C5402只使用14个可屏蔽中断,这些硬件名为:① INT3-—INT0;② RINT0、XINT0、RINT1和XINT1(串行口中断)③ TINT、TINT1(定时器中断)④ HPINT(主机接口)DMAC0——DMAC5。

2)非屏蔽中断25.处理中断步骤:1)接收中断请求2)应答中断3)执行中断服务程序(ISR)26.重新映象中断向量地址:C54x的中断向量表是可重新定位的,即在DSP复位时,IPTR=1FFH,中断向量新被映象到程序存储器的第511页,中断向量表的起始地址固定为0FF80H,复位后,此表的起始地址可由用户指定.中断向量可重新被映象到程序存储器的任何一个128字页开始的地方(除保留区域外).中断向量地址由PMST中的中断向量指针IPTR(9位)和中断向量号(0~31)左移两位后组成。

27.第4章与第6、7章结合看,编程题……28.(实现求和的)例6-2 计算.程序如下:().title “example2。

asm”.mmregsSTACK 。

usect “STK”,10H ;堆栈的设置.bss x , 5 ;为变量分配6个字的存储空间。

bss y , 1。

def start。

datatable: .word 10,20,30,40,50 ;x1,x2,x3,x4,x5.textstart: STK #0 , SWWSR ;插入0个等待状态LD #1 , DPSTM # STACK+10H,SP ;设置堆栈指针STM # x,AR1 ;AR1指向xRPT #4MVPD table,*AR1+LD # 0,ACALL SUMend: B endSUM: STM # x,AR3STM # x,AR4Loop: ADD *AR3+,A ;程序存储器BANZ loop,*AR4—STL A,@ yRET.end.tit le “example2.asm”。