先进的芯片尺寸封装_CSP_技术

半导体封装技术向高端演进 (从DIP、SOP、QFP、PGA、BGA到CSP再到SIP)

半导体器件有许多封装形式,按封装的外形、尺寸、结构分类可分为引脚插入型、表面贴装型和高级封装三类。

从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进。

总体说来,半导体封装经历了三次重大革新:第一次是在上世纪80年代从引脚插入式封装到表面贴片封装,它极大地提高了印刷电路板上的组装密度;第二次是在上世纪90年代球型矩阵封装的出现,满足了市场对高引脚的需求,改善了半导体器件的性能;芯片级封装、系统封装等是现在第三次革新的产物,其目的就是将封装面积减到最小。

高级封装实现封装面积最小化芯片级封装CSP。

几年之前封装本体面积与芯片面积之比通常都是几倍到几十倍,但近几年来有些公司在BGA、TSOP的基础上加以改进而使得封装本体面积与芯片面积之比逐步减小到接近1的水平,所以就在原来的封装名称下冠以芯片级封装以用来区别以前的封装。

就目前来看,人们对芯片级封装还没有一个统一的定义,有的公司将封装本体面积与芯片面积之比小于2的定为CSP,而有的公司将封装本体面积与芯片面积之比小于1.4或1.2的定为CSP。

目前开发应用最为广泛的是FBGA和QFN等,主要用于内存和逻辑器件。

就目前来看,CSP的引脚数还不可能太多,从几十到一百多。

这种高密度、小巧、扁薄的封装非常适用于设计小巧的掌上型消费类电子装置。

CSP封装具有以下特点:解决了IC裸芯片不能进行交流参数测试和老化筛选的问题;封装面积缩小到BGA的1/4至1/10;延迟时间缩到极短;CSP封装的内存颗粒不仅可以通过PCB板散热,还可以从背面散热,且散热效率良好。

就封装形式而言,它属于已有封装形式的派生品,因此可直接按照现有封装形式分为四类:框架封装形式、硬质基板封装形式、软质基板封装形式和芯片级封装。

多芯片模块MCM。

20世纪80年代初发源于美国,为解决单一芯片封装集成度低和功能不够完善的问题,把多个高集成度、高性能、高可靠性的芯片,在高密度多层互联基板上组成多种多样的电子模块系统,从而出现多芯片模块系统。

晶片级封装(WL-CSP)基础

晶⽚级封装(WL-CSP)基础晶⽚级封装(WL-CSP)基础本⽂详细讨论了Maxim的晶⽚级封装(WL-CSP),其中包括:晶圆架构、卷带包装、PCB布局、安装及回流焊等问题。

本⽂还按照IPC和JEDEC标准提供了可靠性测试数据。

注:最终⽤户及安装⼈员应该负责提供其⾏业标准要求设计和装配⽂件,⾏业标准⽂件包括(但不限于)以下内容:概述晶⽚级(WL)芯⽚封装(CSP)是⼀种可以使集成电路(IC)⾯向下贴装到印刷电路板(PCB)上的CSP 封装技术,采⽤传统的SMT安装⼯艺。

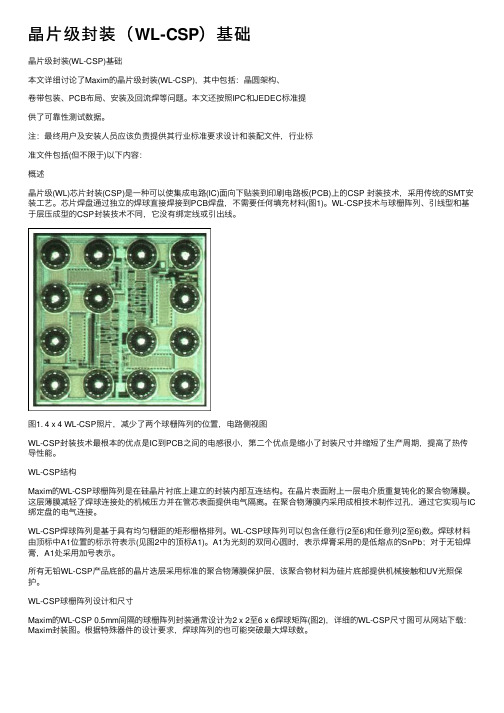

芯⽚焊盘通过独⽴的焊球直接焊接到PCB焊盘,不需要任何填充材料(图1)。

WL-CSP技术与球栅阵列、引线型和基于层压成型的CSP封装技术不同,它没有绑定线或引出线。

图1. 4 x 4 WL-CSP照⽚,减少了两个球栅阵列的位置,电路侧视图WL-CSP封装技术最根本的优点是IC到PCB之间的电感很⼩,第⼆个优点是缩⼩了封装尺⼨并缩短了⽣产周期,提⾼了热传导性能。

WL-CSP结构Maxim的WL-CSP球栅阵列是在硅晶⽚衬底上建⽴的封装内部互连结构。

在晶⽚表⾯附上⼀层电介质重复钝化的聚合物薄膜。

这层薄膜减轻了焊球连接处的机械压⼒并在管芯表⾯提供电⽓隔离。

在聚合物薄膜内采⽤成相技术制作过孔,通过它实现与IC 绑定盘的电⽓连接。

WL-CSP焊球阵列是基于具有均匀栅距的矩形栅格排列。

WL-CSP球阵列可以包含任意⾏(2⾄6)和任意列(2⾄6)数。

焊球材料由顶标中A1位置的标⽰符表⽰(见图2中的顶标A1)。

A1为光刻的双同⼼圆时,表⽰焊膏采⽤的是低熔点的SnPb;对于⽆铅焊膏,A1处采⽤加号表⽰。

所有⽆铅WL-CSP产品底部的晶⽚迭层采⽤标准的聚合物薄膜保护层,该聚合物材料为硅⽚底部提供机械接触和UV光照保护。

WL-CSP球栅阵列设计和尺⼨Maxim的WL-CSP 0.5mm间隔的球栅阵列封装通常设计为2 x 2⾄6 x 6焊球矩阵(图2),详细的WL-CSP尺⼨图可从⽹站下载:Maxim封装图。

电子元件 集成电路 IC 的封装 DIP、QFP、PGA、BGA CSP CGA LGA ZIF SOP PFP

电子元件集成电路 IC 的封装 DIP、QFP、PGA、BGA CSP CGA LGA ZIF SOP PFP... 从foundry厂得到圆片进行减薄、中测打点后,即可进入后道封装。

封装对集成电路起着机械支撑和机械保护、传输信号和分配电源、散热、环境保护等作用。

芯片的封装技术已经历了好几代的变迁,从DIP、QFP、PGA、BGA到CSP再到MCM,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。

近年来电子产品朝轻、薄、短、小及高功能发展,封装市场也随信息及通讯产品朝高频化、高I/O 数及小型化的趋势演进。

由1980 年代以前的通孔插装(PTH)型态,主流产品为DIP(Dual In-Line Package),进展至1980 年代以SMT(Surface Mount Technology)技术衍生出的SOP(Small Out-Line Package)、SOJ(Small Out-Line J-Lead)、PLCC(Plastic Leaded Chip Carrier)、QFP(Quad Flat Package)封装方式,在IC 功能及I/O 脚数逐渐增加后,1997 年Intel 率先由QFP 封装方式更新为BGA(Ball Grid Array,球脚数组矩阵)封装方式,除此之外,近期主流的封装方式有CSP(Chip Scale Package 芯片级封装)及Flip Chip(覆晶)。

BGA(Ball Grid Array)封装方式是在管壳底面或上表面焊有许多球状凸点,通过这些焊料凸点实现封装体与基板之间互连的一种先进封装技术。

BGA封装方式经过十多年的发展已经进入实用化阶段。

1987年,日本西铁城(Citizen)公司开始着手研制塑封球栅面阵列封装的芯片(即BGA)。

ic封装术语

ic封装术语IC封装术语IC(集成电路)封装是将芯片封装成实际可应用的器件的过程。

在IC封装过程中,使用了许多术语来描述不同的封装类型、尺寸和特性。

本文将介绍一些常见的IC封装术语,以帮助读者更好地理解和选择合适的封装。

1. DIP封装(Dual In-line Package)DIP封装是最早也是最常见的IC封装类型之一。

它采用两排引脚,引脚以直线排列,适用于手工插入和焊接。

DIP封装通常用于较大的芯片,如微控制器和存储器芯片。

2. SOP封装(Small Outline Package)SOP封装是一种比DIP封装更小型的封装类型。

它采用表面贴装技术,引脚以直线或弯曲排列。

SOP封装适用于对空间要求较高的应用,如移动设备和计算机外围设备。

3. QFP封装(Quad Flat Package)QFP封装是一种较大的表面贴装封装类型。

它采用四个方向平均分布的引脚,具有较高的引脚密度和良好的散热性能。

QFP封装适用于需要处理大量信号的芯片,如通信芯片和图形处理器。

4. BGA封装(Ball Grid Array)BGA封装是一种先进的表面贴装封装类型。

它采用小球形引脚,以网格状排列在芯片底部。

BGA封装具有更高的引脚密度和更好的散热性能,适用于高性能处理器和FPGA芯片。

5. LGA封装(Land Grid Array)LGA封装是一种类似于BGA封装的表面贴装封装类型。

它采用金属焊盘而不是小球形引脚,以更好地支持高频率和高速信号传输。

LGA封装适用于需要较高信号完整性的应用,如服务器和网络设备。

6. CSP封装(Chip Scale Package)CSP封装是一种尺寸更小的封装类型,接近芯片的尺寸。

它采用直接焊接或粘贴技术将芯片封装成器件。

CSP封装适用于对尺寸和重量要求极高的应用,如智能卡和便携式设备。

7. QFN封装(Quad Flat No-leads)QFN封装是一种无引脚的封装类型,引脚隐藏在芯片的底部。

超级CSP封装技术

( i su u t n T c n lg o, t.T a h i 4 0 h a T a h i a a e h oo yC . d, i S u 0 ,C i ) n H i L n 71 0 n

Abs r c :S pe CSP i a rc t d b ui n p t e i t r os r wi g e ibl n a u a n t e ta t u r s f b ia e y b l g u h n e p e t hih r la e e c ps lnto h di h

芯片 上任 意 部位 暴 露 的 电极 。超 级 C P封 装 技术 , S

4 个 焊球 , 球 间距为 0 5 n 体尺 寸为 6 X 8 焊 . , 7 ml .mm 8 69ml 最 大 高度 为 1 n . n, . ml 。图 2示 出了该 封装 的 0 断 面 图和 层 结 构 。 在制 作 超 级 CS P封 装 中涉 及 到

下 一步 , 用 溅 射把 薄 金 属膜 安装 到 晶 圆表 面 使 上 ,此 膜 是 由黏 附 金属 层和 导 电层 ( 常 为 铜) 通 构

维普资讯

超 级 G P封 装技 术 S

杨建 生

( 水华 天 科技 股份 有 限公 司 , 肃 天 水 7 10 ) 天 甘 4 00

摘 要 : 级 C P是 利 用 晶 圆级 封 装技 术 工Байду номын сангаас艺在 芯 片上 用高 可靠 密封 剂安 装 插板 装 配 的新 密封 工 超 S

艺技 术 。它能 够使 封 装 结 构成 为真 正 的 芯 片尺 寸型 封装 ( GE 。 绍 了超级 C P具 有 良好 的板 K D) 介 S 级 可 靠性 的原 因 : 密封 剂 的 C.. 近 于母 板 的 C.. 密封 剂 的 高粘 附 强度 、 T E接 TE、 焊球 和 端 子连接 部

芯片常见的封装方式

芯片常见的封装方式随着电子科技的发展,芯片技术也在不断地进步和发展。

芯片是电子产品中最关键的部件之一,它的封装方式直接影响到芯片的性能和应用范围。

在现代电子领域中,芯片封装的种类繁多,本文将介绍常见的芯片封装方式。

一、DIP封装DIP (Dual In-line Package)是芯片封装中最常见的一种类型。

DIP封装是一种双行直插式封装,它的引脚排列在两排中间,每排有一些引脚。

DIP封装的优点是结构简单,容易制造,成本低廉,同时也容易进行手工焊接。

但是,由于DIP封装引脚的间距较大,其封装体积较大,不适合在高密度电路板上使用。

二、QFP封装QFP (Quad Flat Package)是一种方形封装,它的引脚排列在四个边上。

QFP封装可以分为LQFP (Low-profile Quad Flat Package)和TQFP (Thin Quad Flat Package)两种类型。

QFP封装的优点是体积小,引脚数量多,适用于高密度电路板。

但是,QFP封装的制造工艺较为复杂,成本较高,同时也不适合手工焊接。

三、BGA封装BGA (Ball Grid Array)是一种球形网格阵列封装。

BGA封装的引脚是由许多小球组成,它们排列在芯片的底部。

BGA封装的优点是引脚数量多,封装体积小,适用于高密度电路板,同时也具有良好的散热性能。

但是,BGA封装的制造工艺极为复杂,需要高精度的制造设备和技术,因此成本较高。

四、CSP封装CSP (Chip Scale Package)是一种芯片级封装,也称为芯片级封装。

CSP封装的特点是封装体积非常小,几乎与芯片本身大小相同。

CSP封装的优点是封装体积小,引脚数量少,适用于高密度电路板,同时也具有良好的散热性能。

但是,CSP封装的制造工艺非常复杂,需要高精度的制造设备和技术,因此成本非常高。

五、COB封装COB (Chip-on-Board)是一种将芯片直接贴在电路板上的封装方式。

LED封装技术之CSP陶瓷封装神奇之处在哪里?

LED封装技术之CSP陶瓷封装神奇之处在哪里?当陶瓷基板的尺寸做到和芯片尺寸几乎一样大小时,其逐渐失去了帮助LED 散热的功能。

相反,如果去掉陶瓷基板,则去掉了一层热界面,有利于热的快速传导到线路板。

同时,随着倒装芯片的成熟,陶瓷基板作为绝缘材料对PN电极线路的再分布的功能已不再需要。

除了在机械结构和热膨胀失配上对LED起到一定保护作用,陶瓷基板对芯片的电隔离和热传导的重要功能已基本丧失。

免去基板同时是传统陶瓷封装固晶所需的GGI或AuSn共晶焊接可以改为低成本的SAC焊锡。

并借助倒装芯片,免去金线及焊线步骤,降低了封装成本。

在各大厂商及媒体宣传CSP封装时,多数绕不开这样一段话——传统LED照明生产分为芯片、封装、灯具三个环节,使用CSP封装后,可省去封装环节,芯片厂可直接和灯具厂进行无缝对接,大幅简化产出工艺和降低成本——这字里行间似乎都在表达封装环节从此将被剔除,封装厂将无活路。

但事实并非如此。

先来普及一个概念,所谓的“芯片级封装”,或者“无封装”、“免封装”其实正解是采用倒装芯片直接封焊到封装底部的焊盘,无金线、无支架、简化生产流程、降低生产成本,这可使得封装尺寸更小,即同样的封装尺寸下可以提供更大的功率。

而且在生产制造的过程当中体积小就会导致生产工艺要求高那么对生产设备的精以及操控人员的水平要求随之就会升度高,同时生产设备价格的高低决定了精度的高低,量产良率和成本将成为最大考量。

在整个CSP生产工艺流程中,每一个工艺步骤,对技术、设备、人才都有较高的要求,而以下几个难点值得一提:1、芯片与芯片之间的距离控制;2、芯片与衬底之间的位置匹配度控制;3、外延芯片波长范围的掌控;4、荧光粉厚度的均匀性控制;5、点胶控制技术;6、密封性。

过去几年,大功率LED的国际巨头纷纷着力改进原有陶瓷封装技术,凭借其先进的大功率倒装芯片或垂直结构芯片,逐渐使封装小型化,以降低陶瓷基板及较低的生产效率带来。

新型电子封装技术

新型微电子封装技术高尚通杨克武(中国电子科技集团公司第十三研究所,河北石家庄050051)摘要:本论文综述了自;十世纪九十年代以来迅速发展的新型微电子封装技术,包括焊球阵列封装(BGA)、芯片尺寸封装(CSP)、圆片级封装(WLP)、三维封装(3D)和系统封装(SIP)等项技术。

同时,叙述了微电子三级封装的概念。

并对发展我国新型微电子封装技术提出了一些思索和建议。

关键词:微电子封装;BGA;CSP;WLP;3D封装;SIP;三级封装中图分类号:305.94 文献标识码:A1 前言集成电路产业已成为国民经济发展的关键,而集成电路设计、制造和封装测试是集成电路产业发展的三大产业之柱。

这已是各级领导和业界的共识。

微电子封装不但直接影响着集成电路本身的电性能、机械性能、光性能和热性能,影响其可靠性和成本,还在很大程度上决定着电子整机系统的小型化、多功能化、可靠性和成本,微电子封装越来越受到人们的普遍重视,在国际和国内正处于蓬勃发展阶段。

本文试图综述自二十世纪九十年代以来迅速发展的新型微电子封装技术,包括焊球阵列封装(BGA)、芯片尺寸封装(CSP)、圆片级封装(WLP)、三维封装(3D)和系统封装(SIP)等项技术。

介绍它们的发展状况和技术特点。

同时,叙述了微电子三级封装的概念。

并对发展我国新型微电子封装技术提出了一些思索和建议。

2 微电子三级封装谈到微电子封装,首先我们要叙述一下三级封装的概念。

一般说来,微电子封装分为三级,如图1所示。

所谓一级封装就是在半导体圆片裂片以后,将一个或多个集成电路芯片用适宜的封装形式封装起来,并使芯片的焊区与封装的外引脚用引线键合(WB)、载带自动键合(TAB)和倒装芯片键合(FCB)连接起来,使之成为有实用功能的电子元器件或组件。

一级封装包括单芯片组件(SCM)和多芯片组件(MCM)两大类。

应该说,一级封装包含了从圆片裂片到电路测试的整个工艺过程,即我们常说的后道封装,还要包含单芯片组件(SCM)和多芯片组件(MCM)的设计和制作,以及各种封装材料如引线键合丝、引线框架、装片胶和环氧模塑料等内容。