北理工通信课程设计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

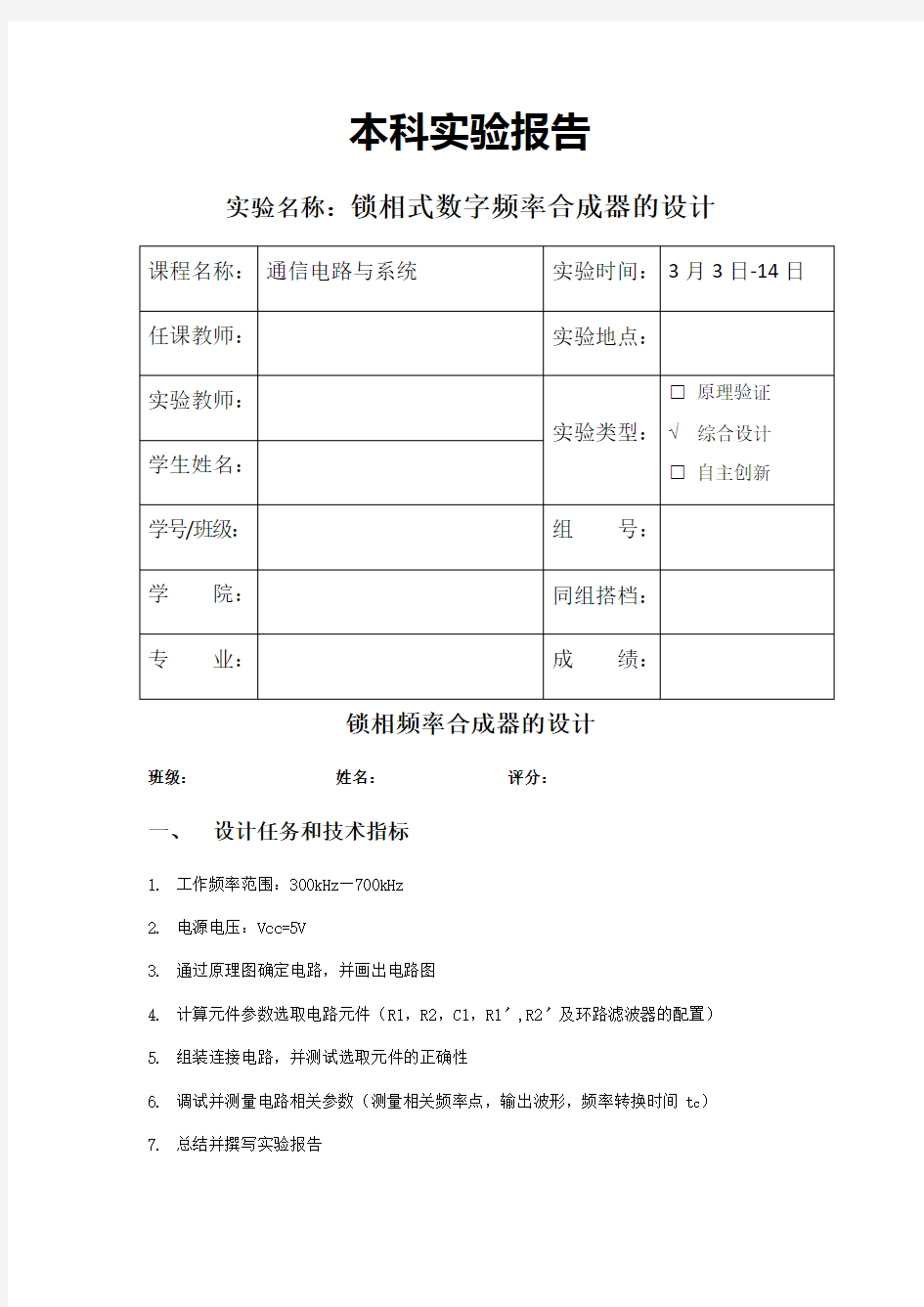

本科实验报告

实验名称:锁相式数字频率合成器的设计

锁相频率合成器的设计

班级:姓名:评分:

一、设计任务和技术指标

1.工作频率范围:300kHz—700kHz

2.电源电压:Vcc=5V

3.通过原理图确定电路,并画出电路图

4.计算元件参数选取电路元件(R1,R2,C1,R1ˊ,R2ˊ及环路滤波器的配置)

5.组装连接电路,并测试选取元件的正确性

6.调试并测量电路相关参数(测量相关频率点,输出波形,频率转换时间t c)

7.总结并撰写实验报告

二、 设计方案

锁相频率合成器原理

锁相环(PLL )是一个相位误差控制系统,利用反馈控制原理实现频率及相位的同步技术。锁相环通过比较输入信号和压控振荡器输出频率之间的相位差,产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频。

锁相环路的基本组成框图如图1-1所示。它由鉴相器(PD )、环路滤波器(LF )和压控振荡器(VCO )三部分组成。其中,PD 和LF 构成反馈控制器,而VCO 就是它的控制对象。

锁相环路的基本组成框图(1-1)

将一个或几个标准频率,经过加、减、乘、除四则运算,变成具有同稳定度和准确度的多个所需频率的技术称为频率合成技术。锁相式频率合成器,其优点是可以实现任意频率和带宽的频率合成,具有极低的相位噪声和杂散。是目前应用最为广泛的一种频率合成方法。

典型的直接式频率合成器组成框图如图1-2所示。它由参考振荡器、参考分频器、鉴相器(PD )、环路滤波器(LF )、压控振荡器(VCO )和可编程分频器等部分组成。

直接式频率合成器(图1-2)

由图1-2可知,晶体振荡器的频率i f 经过M 固定分频后得到步进参考频率REF f ,将REF

f 信号作为鉴相器的基准与N 分频器的输入进行比较,鉴相器的输出Ud 正比于两路输入信号的相位差,Ud 经过环路滤波器得到一个平均电压Uc ,Uc 控制压控振荡器(VCO )频率0f 的变化,

使鉴相器的两路输入信号相位差不断减小,直到鉴相器的输入为零或者某一直流电平,这时称为锁定。锁定后的频率为0//i REF f M f N f ==即0(/)i REF f N M f N f ==。当预置分频数N 变化时,输出信号频率0f 随着发生变化。

锁相环中的滤波器时间常数据定了跟随输入信号的速度,同时也限制了锁相环的捕捉范围。

三、 电路原理与设计

1.CD4046锁相环工作原理

CD4046是通用的CMOS 锁相环集成电路,其特点是电源电压范围宽(为3V -18V ),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz 下功耗仅为600μW,属微功耗器件。

CD4046是带有RC 型VCO 的锁相环路,属于低频锁相环路。采用 16 脚双列直插式,图1-3为CD4046的内部功能框图和构成锁相频率合成器时的外围元件连接图。从图中可以看出,CD4046主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO )、线性放大器、源跟随器、整形电路等部分构成。芯片内含有一个低功耗、高线性VCO ,两个工作方式不同的鉴相器PDI 和PDII ,A1为PDI 和PDII 的公用输入基准信号放大器,源跟随器A2与VCO 输入端相连是专门作FM 解调输出之用的,此外还有一个6V 左右的齐纳稳压管。CD4046的管脚排列图如图1-4。

1-3 CD4046的内部功能图 1-4 CD4046引脚图 CD4046引脚功能描述:

2.参考振荡器工作原理

参考振荡器可采用门电路(74LS系列或CD系列)与标称石英晶体构成振荡器。石

英晶体振振器的电路符号、等效电路、电抗曲线如图1-5所示。工作电路图如1-6所示。

1-5晶振 1-6参考晶体振荡器电路图从石英晶体谐振器的电抗特性可看出,在串、并联谐振频率之间很狭窄的工作频带内,它呈电感性。因而石英振荡器可以工作于感性区和串联谐振频率上,但不能使用容

性区。根据晶体在振荡电路中的不同作用,振荡电路可分为两类:一类是石英晶体在电

路中作为等效电感元件使用,这类振荡器称为并联型晶体振荡器;另一类是把石英晶体

作为串联谐振元件使用,使它工作于串联谐振频率上,称为串联型晶体振荡器。

3.分频器工作原理

分频器采用预置法将两个74HC163先反馈后级联构成,前一级的RCO信号作为后一级的使能信号。时钟信号采用同一输入。分频数通过改变ABCD的高低电平来实现。工作电路图如图1-7。

1-7 分频器电路图

所测频率点为300kHz、500kHz、700kHz,74LS163设置如下:

四、测量结果及分析

实验在面包上搭建电路,共用了1片2.5MHz晶体振荡器、1KΩ电阻两枚、100KΩ和5.1K Ω电阻各一枚、0.1μf、56pf、0.1nf电容各一枚、4片74HC163、2片74HC04、1片CD4046,搭建的时候完成一个模块测试一个模块。

调试电路设备有双路直流稳压电源、数字频率计、数字示波器、万用表、

低频信号发生器。调试采用分步逐级调试。

1.晶体振荡器输出频率的测量:将晶体振荡器输出的信号接入多功能计

数器接头上,测量晶体产生的频率。稳定在2.5MHz。

2.1/M分频器输出频率的测量:测量74ls163高位片15脚输出频率。

稳定在25KHz。

f测量:测量CD4046第4管脚输出频率,应稳定在300、500、700KHz。

3.输出频率

4.峰值时间tm和频率转换时间tc的特征参数:N分频器低位片3管脚接50Hz占

空比为50%的方波和双踪示波器1路接,示波器2路测量CD4046第9管脚输出波形,

测量tc和tm。

f输出稳定,结果见下表

实验结果: